通过增益校准提高DAC积分非线性(INL)

数字模拟转换器(DAC) 的静态绝对精度可以从三个基本错误类型来描述:偏移、增益误差和非线性。线性误差是这三个中最具挑战性的,在许多应用中,用户可以忽略偏移和增益误差或者在系统设计中建立终端自动校验来补偿。然而,线性错误则需要更复杂的修正方法。

DAC(见图1)把数字输入代码转换为模拟输出信号,可能是电流或电压。DAC的分辨率指的是DAC能产生的单位输出电平数量。例如,一个8位分辨率的DAC能够产生28(256)的不同输出电平。理想情况下,每一个数字代码提供同等的模拟阶数;然而,实际上很难达到。

图1:8位DAC符号

DAC线性问题

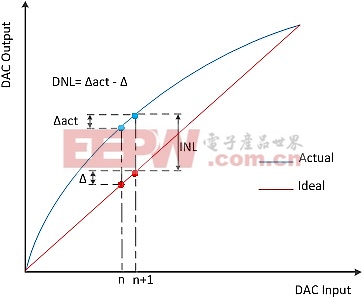

在介绍提高DAC积分非线性(INL)之前,最好先回顾一下如何确定其线性,如图2所示。在DAC中,我们通常都把注意力放在两个方面:微分非线性(DNL)和积分非线性(INL)。DNL是指实际模拟输出阶数的最大偏差,即相邻输入代码之间与理想阶数值(Δ) 的最大偏差。INL是指在传递函数中的任何点,实际输出和理想阶数的最大偏差。理想值是零和DAC满量衡之间的一条直线 (见图2)。

图2:DAC线性误差,DNL和INL

传统的终端校准技术用来消除DAC 增益误差。然而,增益误差一般不会在DAC满量程都是线性的,因为硅内部有各种非理想体系。这些体系模式可能造成单向梯度,从而导致比较差的INL性能。

非线性主要原因如下:

- 边缘效应,例如长度扩散(LOD)

- 掺杂梯度

- 氧化层厚度梯度变化导致阈值移位

- 热梯度

- 供电线路电压下降 ?

因此,终端校正技术并不足以完全清除增益误差,INL性能仍旧很差。需要输出精度高的应用就需要很低的INL。

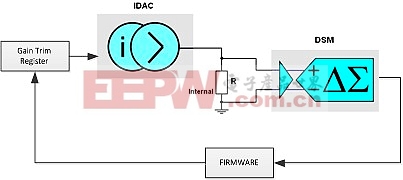

固件技术

提高INL性能的方式之一是使用固件技术。该方法充分利用了片上系统 (SoC)技术,在系统中建立两点自动校验。在这个例子中,我们将使用PSoC® 3系列,其有4个多重范围 8位电压/电流DAC(INL约为1.5 LSB)。片上20位 Delta-Sigma模拟/数字转换器(ADC)的 INL在12位模式下小于1 LSB。这足够用来校准8位DAC。需要固件来完成DAC输出和ADC之间的反馈回路 (见图3)。

图3:带ADC反馈的IDAC

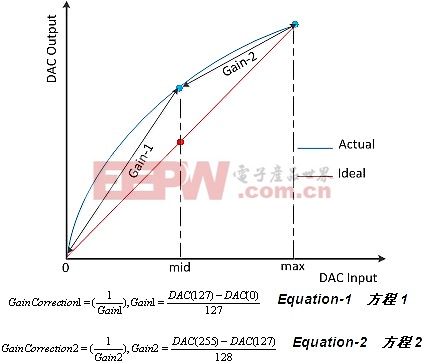

INL通常在满量程的一半达到其最大值,如图 4所示。如果我们能把这个峰值降下来,我们将会显著改善INL。这个发现引导我们使用两点校正代替终端或单点校正技术,因为通过终端或单点校正技术并不足以完全去除增益误差。第一个校准点用来校准前半部分(见方程1)。同样,第二个校准点用于校准后半部分(见方程2)。

该算法工作流程如下,见图5。最初,这两个增益修正值在DAC数字输入值中间和末端计算和保存。这是唯一一次使用ADC。因此,我们只有需要测量和计算校准一次。

图5:两点增益校准算法流程图

在正常操作期间,如果传到DAC的数字代码小于中间点,转换前使用第一个增益校准值来修正。如果传到DAC的数字代码大于中间点,转换前使用第二个增益校准值来修正。通过更新图3所示的gain trim registers(增益调整寄存器)校准即时完成。使用SoC里面的直接存储器存取(DMA)模块,寄存器更新速度会更快。

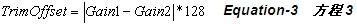

在全范围中间改变增益修正值会产生调整偏移(见方程3)。这个调整偏移需要在算法的后半部分来补偿 (见图5)。

结果

我们来做个比较,使用传统终端校验的8位电流DAC(iDAC)没有实施我们所讲的算法之前测量的INL性能,INL大约为1.5 LSB,如图6所示。

图6:使用传统终端增益校验IDAC的INL

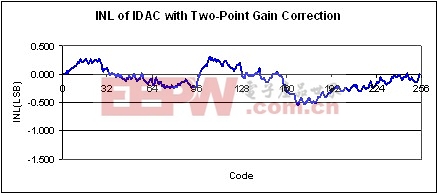

使用该算法后,INL现在降到0.8LSB,如图7所示。

图7:使用两点增益校准IDAC的INL

结论

我们介绍了SoC中用于提高DAC积分非线性 (INL)的固件技术。并以PSoC® 3为例进行了验证。对于PSoC® 3中的电流和电压DAC,该方法可以使INL改善85%。

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 高速DAC AD9712B/AD9713B的原理和应用(11-30)

- 混频器用作开关,可使 DAC 采样频率加倍(01-22)

- 什么是DAC(数模转换器)(01-24)