功率管理技术介绍

关系,并且存在体偏压系数γ。

相同方法还适用于存储器设计。存储器在其位单元和外围电路中都可能有高阈值电压器件,并具有反向偏压控制来管理关断状态时的泄漏。把不同的阈值电压器件组合用于位单元和外围电路,这可提供广泛的存储器泄漏控制和多个性能级别。如果降低存储器的电源电压,就会使性能明显下降。

功率管理

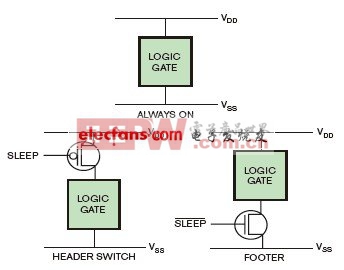

在研究了电路级的功率管理方法后,你可以研究芯片级的方法。第一种是当电路不工作时,用电源开关来关闭它们。在关闭模式中,电路仅消耗泄漏功率,不消耗有功功率。你可把MOSFET用作连接到电源轨和接地轨的开关,来关闭电源(图4)。在实现关闭时,你必须考虑电路如何苏醒,并且有时你必须保持设计方案的状态。在此情形中,你可使用保持双稳态多谐振 荡器来存储状态。

图4,可以用头开关和脚开关来关断逻辑电路,以便节省有功功率。

在控制设计方案的哪些零件需要关闭方面,你可以用电源开关来提供多级粒度。你可以在逻辑门级开关电源,为每个门配备连接到电源的头开关(header switch)和脚开关(footer switch)。或者你可以把头开关和脚开关与逻辑集群一起使用,或是在块级与功率岛一起使用。你还可以简单地把功率岛连接到不同的电源,设计方案在外部接通或关断电源,由此在不使用电源开关的情况下使用功率岛。

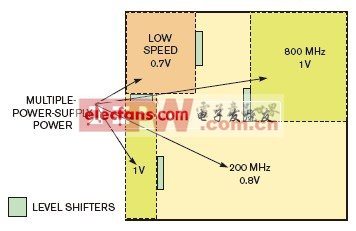

多电源设计方案配备具有不同值的功率岛(图5)。该方法使较慢的逻辑块能以较低电压运行,由此省电。对于多电源设计方案,你必须在功率岛边界插入电平移位单元。这些单元把逻辑电平转换成它们连接的功率岛的恰当电平。统一功率格式(UPF)语言使芯片设计者能描述带有电源选通和多个电源的设计方案。它允许定义隔离单元、电平移位器、电源选通开关。共同功率格式(CPF)是一种相似的语言,具有相同目的。这些语言目前在彼此竞争,以便成为定义设计方案功率管理的唯一标准。

图5,在具有多个电源域的芯片中,低性能部分使用功率较低的电源来降低功率。电平移位器恰当地连接了不同域中的逻辑电路。

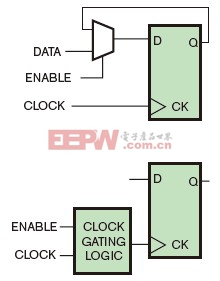

目前的EDA工具有效地支持这些功率管理方法。它们还在实现期间提供额外的省电效果。由于时钟网络和它们驱动的双稳态多谐振荡器消耗大量电力,因此你可以在不需要它们运行时关断时钟(即选通时钟),由此实现省电。时钟选通可在双稳态多谐振荡器的输入端不工作的周期内,取消该振荡器中的时钟活动(图6)。

图6,时钟选通在双稳态多谐振荡器的输入端不工作的周期内取消该振荡器中的时钟活动。

你还能优化时钟分配网络中的功率。利用克隆方法,你可以把时钟树分解成更小的部分,由此降低时钟网络的总电容和功率。物理优化过程也考虑了功率。一旦你满足了时序约束,物理优化就会减少非关键路径中的门,来降低功率,并且不影响时序。

泄漏优化

主要的泄漏功率优化途径是使用标准单元库和多电压阈值器件。许多工具允许设计者在物理实现期间使用多个库,并自动从恰当的库中选择单元,来优化泄漏功率并实现性能目标。但是,应小心使用该特性,这是因为设计方案的面积有时可能会变大。较高阈值电压的单元很脆弱,在混合阈值电压设计方案中,80%的单元一般具有高阈值电压,其余20%具有标准阈值电压或低阈值电压。你可以把具有多种沟道长度的库和多阈值电压器件相结合,来提供额外灵活性。

另一种可能是使用台积电公司的Power-Trim服务,它改变非关键路径中的晶体管的沟道长度,并且实际上不影响设计布局。该方法向多晶硅掩模施加偏压,指示掩模制造工艺做出调整,来增加晶体管的有效沟道长度。Power-Trim把这项任务作为制造期间的一个加工后的步骤,优点是不影响设计日程表。

一旦设计方案实现了它的性能目标,Power-Trim就用Tela公司从Blaze DFM公司收购来的软件分析设计方案,并给沟道长度可以增加的晶体管加标签。典型情况下,这些器件位于设计方案的非关键路径中。该工具以预定义的增量来增加沟道长度,它有一个预先分配了特征的标准单元库。该工具用改造后的门来执行时序分析,以便确保没有影响芯片性能。该方法能额外节省20%至30%的泄漏功率。由于该方法只改造标准单元库中的晶体管,因此它只在数字逻辑占主导地位,并且泄漏功率是总功率重要部分的设计方案中有意义。

有时被工程师们忽视的功率管理的另一方面是功率完整性。功率完整性同时影响芯片的核心和I/O功率。你必须在核心中小心配电,特别是在多电源设计方案中,并且外部供电是通过焊线封装来完成时。 在典型的双稳态多谐振荡器设计方案中,可供使用的大量凸块(尤其是在芯片的核心区)促成了向核心配

功率管理 相关文章:

- 优化移动多媒体传输链的功耗(05-25)

- 功率管理优化功率的实现(08-11)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)