DAC及其缓冲器有助于提升系统性能与简化设计一

本文将考察一款新型精密16位DAC,同时针对性能可与变压器媲美的高速互补电流输出DAC的输出缓冲谈一些想法。

电压开关式16位DAC提供低噪声、快速建立时间和更出色的线性度

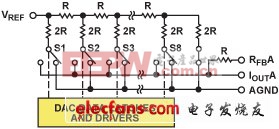

基于突破性10位CMOSAD7520--推出已近40年--的电阻梯乘法DAC最初用于反相运算放大器,而放大器的求和点 (IOUTA) 则提供了方便的虚拟地(图1)。

图1. CMOS乘法DAC架构

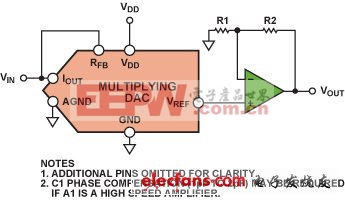

然而,在某些限制条件下,它们也可用于提供同相电压输出的电压开关配置 其中,运算放大器用作电压缓冲器(图2)。此处,基准电压VIN施加于OUT,输出电压VOUT,则由VREF提供。后来不久即出现了针对这种用途而优化的12位版本。

图2. 电压开关模式下的乘法DAC

快速推进到现在: 随着单电源系统的不断普及,设计师面对一个挑战,即在维持高电压下的性能水平的同时控制功耗。对能用于这种模式的更高分辨率(最高16位)的器件的需求也日益增加。

在电压开关模式下使用乘法DAC的显着优势是不会发生信号反相,因此,正基准电压会导致正输出电压。但当用于该模式时,R-2R梯形架构也存在一个缺陷。相对于同一DAC用于电流导引模式的情况,与R-2R梯形电阻串联的N沟道开关的非线性电阻将导致积分线性度(INL)下降。

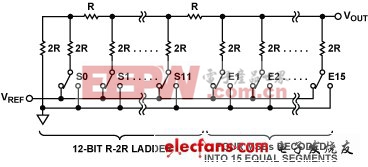

为了克服乘法DAC的不足并同时保持电压开关的优势,人们开发出了新型的高分辨率DAC,比如AD5541A,(如图3所示)。AD5541A采用一个部分分段的R-2R梯形网络和互补开关,在16位分辨率下可实现±1-LSB精度,在?40°C至+125°C的整个额定温度范围内均无需调整,其噪声值为11.8 nV/√Hz,建立时间为1?s.

图3. AD5541A架 构

性能特点

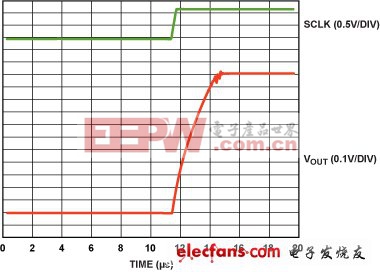

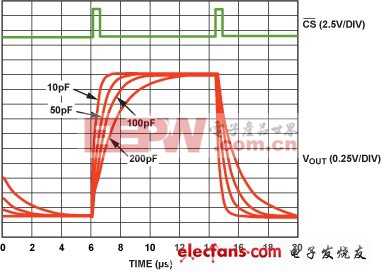

建立时间: 图4和图5比较了乘法DAC在电压模式下的建立时间以及AD5541A的建立时间。当输出上的容性负载最小时,AD5541A的建立时间约为1?s.

图4. 乘法DAC的建立时间

图5. AD5541A的建立时间

噪声频谱密度: 表1比较了AD5541A和乘法DAC的噪声频谱密度。AD5541A在10kHz下的性能略占优势,在1 kHz下优势非常明显。

表1. AD5541A与乘法DAC的噪声频谱密度

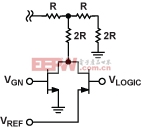

图6. 乘法DAC开关

要使电流在NMOS器件中流动, VGS必须大于阈值电压, VT.在电压开关模式下, VGS = VLOGIC – VIN必须大于VT = 0.7 V.

乘法DAC的R-2R梯形电阻设计用于将电流平均分配至各个引脚。这就要求总接地电阻(从各引脚顶部看)完全相同。这可以通过调节开关来实现,其中,各个开关的大小与其导通电阻成比例。如果一个引脚的电阻发生变化,则流过该引脚的电流将发生变化,结果导致线性度误差。VIN不能大到会使开关关闭的程度,但必须足以使开关电阻保持低位,因为VIN的变化会影响VGS 从而导致导通电阻发生非线性变化,如下所示:

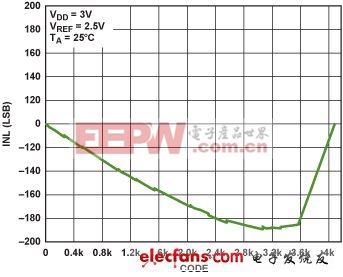

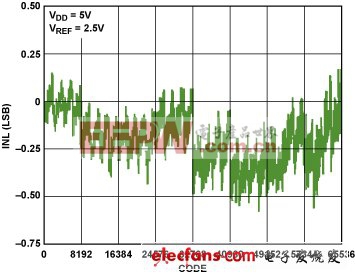

导通电阻的这种变化会使电流失衡,并使线性度下降。因此,乘法DAC上的电源电压不能减少太多。相反,基准电压超过AGND的值不得高于1V,以维持线性度。对于5V电源,当从1.25V基准电压变化至2.5V基准电压时,线性度将开始下降,如图7和图8所示。当电源电压降至3V时,线性度将完全崩溃,如图9所示。

图7. INL of IOUT 乘法DAC在反相模式下的INL,( VDD = 5 V, VREF = 1.25 V)

图8. INL of IOUT乘法DAC在反相模式下的INL(VDD = 5 V, VREF = 2.5 V)

图9. 乘法DAC在反相模式下的INL( VDD = 3 V, VREF = 2.5 V)

为了减少这种影响,AD5541A采用互补NMOS/PMOS开关,如图10所示。现在,开关的总导通电阻来自NMOS和PMOS开关的共同贡献。如前所示,NMOS开关的栅极电压由内部逻辑控制。内部产生的电压,VGN,设置理想栅极电压,以使NMOS的导通电阻与PMOS的相平衡。开关的大小通过代码调节,以使导通电阻随代码调节。因此,电流将上下调节,精度将得以维持。由于基准输入的阻抗随代码变化,因此,应通过低阻抗源驱动。

图10. 互补NMOS/PMOS开关

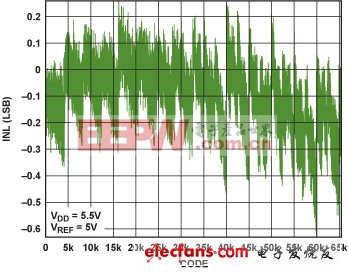

图11和图12所示为AD5541A在5 V和2.5 V基准电压下的INL性能。

图11. AD5541A的INL( VDD = 5.5 V, VREF = 5 V)

图12. AD5541A的INL( VDD = 5.5 V, VREF = 2.5 V)

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 高速DAC AD9712B/AD9713B的原理和应用(11-30)

- 混频器用作开关,可使 DAC 采样频率加倍(01-22)

- 什么是DAC(数模转换器)(01-24)