高速数模转换器的数字特性

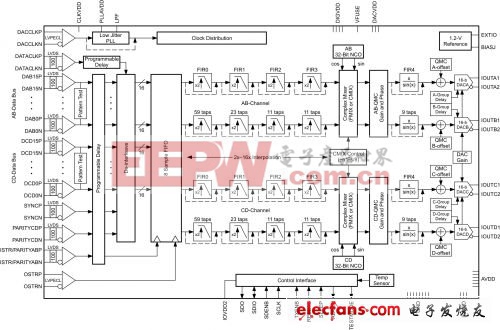

当今的高速数模转换器 (DAC) 通常都包含有许多数字信号处理模块,让其更加易于使用。应论述需要,我们使用了 TI 的 DAC34H84,它是一款 4 通道、16 位、1250 Msps 的 DAC。这样做的原因是,它是一种典型的高速数模转换器,拥有隔离输入和 DAC 时钟域的输入 FIFO、插值数字模块、精细频率分辨率数字正交调制、模拟正交调制器校正以及 sin(x)/x 校正。本文将逐一介绍这些特性的功能和作用。

图 1 DAC34H84 功能结构图

第一个数字模块是插值模块,它负责增加 DAC 内部数字信号的采样速率。一般而言,利用两倍采样速率增加步骤,来实现插值。利用在输入采样点之间插入零来完成这项工作,其在 fIF和 FIN – fIF产生两个信号。通过一个数字低通滤波器后,去掉了位于 FIN – fIF的第二个信号,只在 fIF留有信号。使用插值的原因与大多数高速 DAC 使用的零阶保持输出结构有关。利用零阶保持,DAC 根据时钟周期初期的数字采样对输出振幅进行相应的设置,然后保持住,直到时钟周期和下一个输出采样末端为止。这样便产生一种“上楼梯式”的输出,其频率响应如方程式 1 表示:

sin(π*fIF/fs)/(?π*fIF/fs) 方程式 1

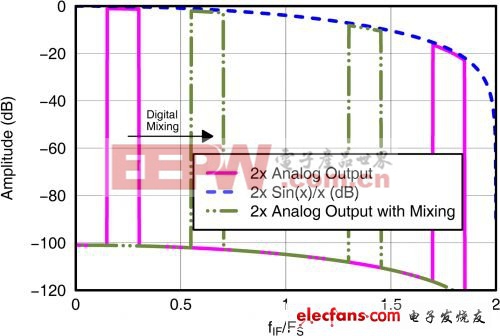

其中,fIF为模拟输出频率,而 fs为采样速率。这种响应具有低通效果(请参见图 2),其 f = fs/2 时的损耗为 ~ 3.5 dB,并在 fs倍数时为零。尽管 DAC 输出在 N*fs +/- fIF时会有信号图像,但较高奈奎斯特 (Nyquist) 区域的图像振幅远低于 fIF 处的信号,从而有更低的信噪比 (SNR),并可能出现明显的振幅下降。这便将大多数应用限制在 fs/2 以下的输出信号频率。另外,fIF处的信号和 fs – fIF图像之间的间隔,随着 fIF接近 fs/2 而减小,从而让 DAC 输出端的模拟滤波器(作用是去除 fs – fIF多余图像)难以建立,最终将大多数应用的 fIF限制在 fs/3 以下。

图 2 无插值模块的 DAC 输出频谱

利用 DAC 插值模块增加 DAC 内部采样速率,只需让 DAC 的数字接口速率 fIN足够高,以允许信号带宽传输,并且只需增加少量的额外带宽便可以拥有插值滤波器过渡频带(实信号时 fin > 2.5*BW,复信号时 fin> 1.25*BW)。利用插值增加采样速率,可以让信号轻松地位于 fs/2 以下。

增加采样速率的另一个好处是,让数字混频能够将输出IF增加至更高频率。例如,使用 2X 插值,输出频率便可高于 fin/2,而如果不使用插值就不可能获得这一结果(请参见图 3)。一般而言,复输入信号使用复混频器,目的是避免混频过程中产生图像。混频输出可以为实 IF 信号,也可以是复 IF 信号,在模拟 IQ 调制器 DAC 之后有效。

图 3 2X 插值的 DAC 输出频谱

将复 DAC 输出用于模拟正交调制器 (AQM),突出表明了高速 DAC 共有的另一个有用的数字特性—正交调制器校正模块。该模块负责对模拟正交调制器的增益、相位和偏移失衡进行校正,从而改善 AQM 边带抑制度和 LO 馈通性。

最后,位于数字信号链末端的是数字 FIR 滤波器,它负责对首个奈奎斯特区域的 Sin(x)/x 高低频规律性衰减进行补偿。在 DAC34H84 实施中,该滤波器可以提供高达 0.4*fDAC的补偿,且误差低于 0.03dB。

正如本文所述,如 DAC34H84 等高速 DAC 拥有大量的数字特性。这些特性,通过降低数据速率和改善输出信号特性,让系统实施变得简单和容易。

- 高速差分ADC驱动放大器AD8137及其应用(01-17)

- 8位高速A/D转换器TLC5510的应用(02-16)

- 一种高速低压低静态功耗欠压锁定电路(03-13)

- 高速串行接口特征与应用(05-20)

- 高速数字电路电源系统的电磁兼容研究(11-20)

- 数字式超声波探伤仪中高速数据采集模块设计(04-04)