MC8051微处理器硬件模块

MC8051硬件模块

单片机作为一个大型设计,其内核由定时器时钟管理单元、ALU算数逻辑单元、串口及控制单元、存储单元RAM及ROM等模块组成。

1 时钟管理单元

MC8051内核采用完全同步的时钟设计。只有一个时钟信号控制每个存储单元的输入。没有使用门时钟,时钟没有输入到任何组合逻辑单元。中断输入线使用两级同步(锁存2次)与全局时钟同步。可以达到完全同步,即使用其他时钟的外部电路在驱动。并行I/0端口没有采用这种同步方式。

2 定时器、串口和中断

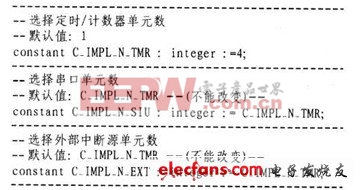

标准8051微控制器只提供两个定时/计数器单元、一个串口单元及两个外部中断源。而在MC805l IP核中,这些单元最多可增加到256组,只需修改VHDL源代码增加兼容的单元数。在VHDL源程序文件mc8051_p.vhd中,更改C_IMPL_N_TMR、C_IMPL_N_SIU、C_IMPL_N_EXT的常量值就可以,其范围是1~256。相关的VHDL代码如图1所示。

图1 相关VHDL代码

这里C_IMPL_N_TMR、C_IMPL_N_SIU、C_IMPL_N_EXT3个常量参数不能独立修改数值,只能同时增减。C_IMPL_N_TMR加l意味着对应的添加了2个定时/计数器、一个串口单元和2个外部中断源。为了能寻址所生成的单元而不改变微控制器的地址空间,在微控制器的特殊功能寄存器(SFR)内存空间增加了2个8位寄存器作为附加功能寄存器:分别是TSEL(定时/计数器选择寄存器,地址为Ox8E)和SSEL(串口选择寄存器,地址为Ox9A)。如果以上的寄存器指向不存在的器件单元,将使用默认的l单元,如果没有对这两个寄存器赋值,其缺省值为1。如果在中断发生期间设备(寄存器)没被选中(比如TSEL),那么相应的中断标志位将保持置位,直到执行中断服务程序。

3 存储器接口单元

由于采用优化结构设计,存储器采用同步结构,限制输入、输出的时序,因而存储器输入、输出数据没用寄存器寄存。

- 一种通信电源监控系统组网方案的设计(01-05)

- 通信电源监控系统下位机硬件电路的设计(01-05)

- 支持CAN总线的电动车辅助逆变电源的设计(02-23)

- 微处理器电源监控芯片SGM803及其应用(06-18)

- 微控制器的市场前景及发展趋势(06-21)

- RS485串行总线可靠性的研究(03-24)