基于Protues的集成运放非线性应用仿真

摘要:集成运算放大器是电子系统中最重要的模拟器件。它的应用主要分为线性应用和非线性应用。在非线性应用中,运算放大器构成的单门限电压比较器、迟滞比较器是构成矩形波、三角波和锯齿波等信号产生电路的核心模块。在此主要讨论利用Protues平台对集成运放的非线性应用设计及仿真。

关键词:Protues;集成运放;非线性应用;仿真

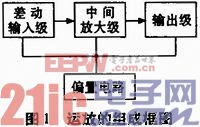

集成运算放大器(简称运放,integrated operational amplitier,OPA)是一种高增益多级直接耦合放大器,其内部结构如图1所示。

集成运放的应用可以分为线性应用和非线性应用。在线性应用范畴,主要用于各种放大器和运算电路;在非线性应用范畴,主要用于构成比较器及其应用电路,如矩形波产生电路等。下面,对集成运放在非线性应用领域的应用进行讨论和仿真。

1 集成运放的非线性应用

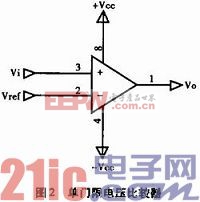

1.1 单门限电压比较器

单门限电压比较器的电路如图2所示。这是一个同相比较器,即当Vi大于Vref时,输出电压约等于+Vcc;当输入电压小于Vref时,输出电压约等于-Vcc。

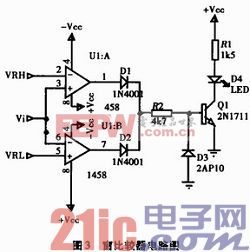

1.2 用单门限电压比较器构成的窗比较器

图3是一个用单门限电压比较器构成的窗比较器。它是由一个同相比较器和一个反相比较器组合而成。该电路的功能是,可以判断输入电压的值Vi是否介于下参考电压VRL与上参考电压VRH之间(所谓的窗)。如果VRLViVRH,窗比较器的输出电压值为0,如果输入电压ViVRL或Vi>VRH,则输出电压Vo将等于运放的饱和输出电压+VSAT(+VSAT比+Vcc小1.4V左右)。可以用发光二极管判别窗比较器的输出电平。窗比较器广泛用于信号的电平监测与报警。

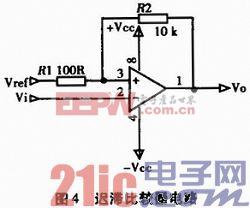

1.3 迟滞比较器

反相输入迟滞比较器原理图如图4所示。

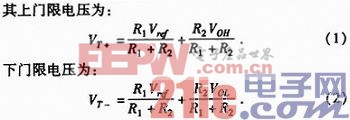

由于迟滞比较器的运放处于正反馈状态,因此一般情况下,输出电压Vo与输入电压Vi不成线性关系。只有在输出电压Vo发生跳变瞬间,集成运放两个输入端之间的电压才近似认为等于0,即VID=0或Vp=Vn=Vi是输出电压Vo转换的临界条件,当Vi>Vp,输出电压为低电平VOL;反之,为高电平VOH。

1.4 利用迟滞电压比较器构成方波发生器

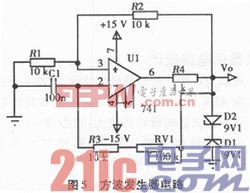

方波发生器的电路如图5所示。

该电路产生的方波信号频率为:

式中,R为R3与RV1之和。通过调节RV1可以改变信号频率。

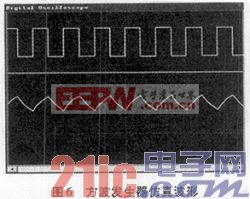

仿真波形中方波为电路的输出波形,下面的波形是电容器充放电波形。

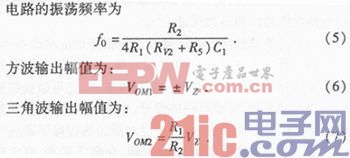

1.5 利用迟滞比较器和积分电路构成三角波方波发生器

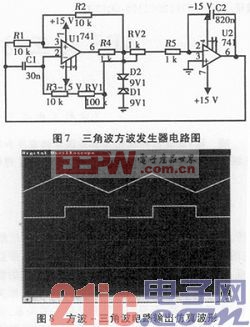

把迟滞比较器和积分电路首尾相接形成正反馈闭环系统,如图7所示。

迟滞比较器U1输出的方波经积分电路U2积分即可得到三角波,三角波又触发比较器自动翻转形成方波,这样即可构成三角波-方波发生器。

调节RV2可以改变方波和三角波的频率,也可以改变C1粗调频率。

综上所述,集成运放的非线性应用与线性应用一样,在模拟电路中都具有十分重要的地位。正确掌握集成运放的非线性应用对电子设计人员是非常必要的。

- 基于GB3442-82的集成运放参数测试仪设计 (03-05)

- 高灵敏度集成运放等效模型设计(12-29)

- 集成运放电路设计原理图(10-19)

- 各类集成运放的性能特点(05-15)

- 引起集成运放闭环工作不稳定的其他因素(02-12)

- 集成运放的表示符号及引出端(11-19)