良好接地指导原则

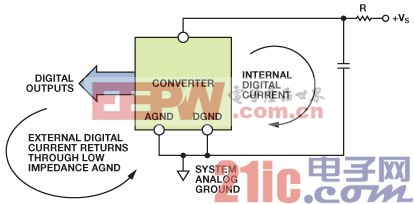

独的模拟地和数字地 事实上,数字电路具有噪声。饱和逻辑(例如TTL和CMOS)在开关过程中会短暂地从电源吸入大电流。但由于逻辑级的抗扰度可达数百毫伏以上,因而通常对电源去耦的要求不高。相反,模拟电路非常容易受噪声影响—包括在电源轨和接地轨上—因此,为了防止数字噪声影响模拟性能,应该把模拟电路和数字电路分开。这种分离涉及到接地回路和电源轨的分开,对混合信号系统而言可能比较麻烦。 然而,如果高精度混合信号系统要充分发挥性能,则必须具有单独的模拟地和数字地以及单独电源,这一点至关重要。事实上,虽然有些模拟电路采用+5 V单电源供电运行,但并不意味着该电路可以与微处理器、动态RAM、电扇或其他高电流设备共用相同+5 V高噪声电源。模拟部分必须使用此类电源以最高性能运行,而不只是保持运行。这一差别必然要求我们对电源轨和接地接口给予高度注意。 请注意,系统中的模拟地和数字地必须在某个点相连,以便让信号都参考相同的电位。这个星点(也称为模拟/数字公共点)要精心选择,确保数字电流不会流入系统模拟部分的地。在电源处设置公共点通常比较便利。 许多ADC和DAC都有单独的“模拟地”(AGND)和“数字地”(DGND)引脚。在设备数据手册上,通常建议用户在器件封装处将这些引脚连在一起。这点似乎与要求在电源处连接模拟地和数字地的建议相冲突;如果系统具有多个转换器,这点似乎与要求在单点处连接模拟地和数字地的建议相冲突。 其实并不存在冲突。这些引脚的“模拟地”和“数字地”标记是指引脚所连接到的转换器内部部分,而不是引脚必须连接到的系统地。对于ADC,这两个引脚通常应该连在一起,然后连接到系统的模拟地。由于转换器的模拟部分无法耐受数字电流经由焊线流至芯片时产生的压降,因此无法在IC封装内部将二者连接起来。但它们可以在外部连在一起。 图1显示了ADC的接地连接这一概念。这样的引脚接法会在一定程度上降低转换器的数字噪声抗扰度,降幅等于系统数字地和模拟地之间的共模噪声量。但是,由于数字噪声抗扰度经常在数百或数千毫伏水平,因此一般不太可能有问题。 模拟噪声抗扰度只会因转换器本身的外部数字电流流入模拟地而降低。这些电流应该保持很小,通过确保转换器输出没有高负载,可以最大程度地减小电流。实现这一目标的好方法是在ADC输出端使用低输入电流缓冲器,例如CMOS缓冲器-寄存器IC。 图1. 数据转换器的模拟地(AGND)和数字地(DGND)引脚应返回到系统模拟地。 如果转换器的逻辑电源利用一个小电阻隔离,并且通过0.1 μF (100 nF)电容去耦到模拟地,则转换器的所有快速边沿数字电流都将通过该电容流回地,而不会出现在外部地电路中。如果保持低阻抗模拟地,而能够充分保证模拟性能,那么外部数字地电流所产生的额外噪声基本上不会构成问题。 接地层 接地层的使用与上文讨论的星型接地系统相关。为了实施接地层,双面PCB(或多层PCB的一层)的一面由连续铜制造,而且用作地。其理论基础是大量金属具有可能最低的电阻。由于使用大型扁平导体,它也具有可能最低的电感。因而,它提供了最佳导电性能,包括最大程度地降低导电平面之间的杂散接地差异电压。 请注意,接地层概念还可以延伸,包括 电压层。电压层提供类似于接地层的优势—极低阻抗的导体—但只用于一个(或多个)系统电源电压。因此,系统可能具有多个电压层以及接地层。 虽然接地层可以解决很多地阻抗问题,但它们并非灵丹妙药。即使是一片连续的铜箔,也会有残留电阻和电感;在特定情况下,这些就足以妨碍电路正常工作。设计人员应该注意不要在接地层注入很高电流,因为这样可能产生压降,从而干扰敏感电路。 保持低阻抗大面积接地层对目前所有模拟电路都很重要。接地层不仅用作去耦高频电流(源于快速数字逻辑)的低阻抗返回路径,还能将EMI/RFI辐射降至最低。由于接地层的屏蔽作用,电路受外部EMI/RFI的影响也会降低。 接地层还允许使用传输线路技术(微带线或带状线)传输高速数字或模拟信号,此类技术需要可控阻抗。 由于“总线(bus wire)”在大多数逻辑转换等效频率下具有阻抗,将其用作“地”完全不能接受。例如,#22标准导线具有约20 nH/in的电感。由逻辑信号产生的压摆率为10 mA/ns的瞬态电流,流经1英寸该导线时将形成200 mV的无用压降: 对于具有2 V峰峰值范围的信号,此压降会转化为大约200 mV或10%的误差(大约“3.5位精度”)。即使在全数字电路中,该误差也会大幅降低逻辑噪

![]()

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)