硅频率控制器(SFC)技术(二)

R1:动态阻抗

C1:动态电容

L1:动态电感

C0:静态电容

CL:负载电容

并行振荡模式的频率可根据以下公式:

FL=[1/2π√(L1*C1))] 2eq eq *√[1+C1/(C0+CL)]

其中[1/2π√(L1*C1))]是晶体串行振荡模式的频率

根据泰勒展开:

FL=[1/2π√(L1*C1) 2eq eq ]*[1+C1/2(C0+CL)] (1)

从公式中可以看出,频率与C0,C1和CL都有关。

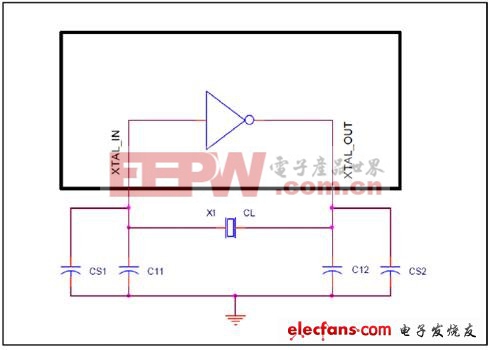

在基频谐振中C1为10-30fF,一般取值为20fF。C0取值与晶体的尺寸有关,一般取值为5pF。但是CL的计算与晶体外接电容和PCB设计和材料有关。下图是参考电路图

图3 晶体外接负载电容示意图

从上面电路中可得出:

1/(C11+CS1)+1/(C12+CS2)=1/(CL) (2)

其中C11,C12是外接电容,也就是线路设计中放在晶体两边接地的两个电容。CS1和CS2是寄生电容,和PCB 电路板的走线,焊盘及芯片的管脚有关。一般为5-10pF(在本文的计算中可设为8pF)。对于C11和C12,没有确定的值(15pF-30pF),这和实际设计有关,例如取18pF。

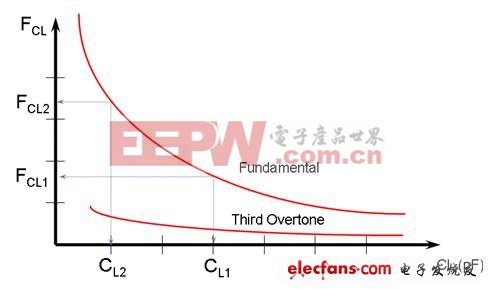

CL如有变化,并行振荡模式的频率也随之变化,请看图4

图4 负载电容变化与频率的关系

由公式(1)可得频率变化为:

(FCL1-FCL2)/FCL1=C1/2 * [1/(C0+CL1)-1/(C0+CL2)] * 10E6 (3)

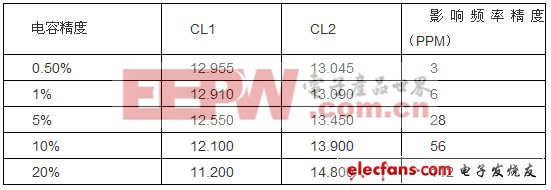

从公式(2)和公式(3)中可知C11和C12的精度将影响频率的精度。具体数据如表1所示。其中参数的取值如前文:C1=20fF,C0=5pF,CS1=CS2=8pF,C11=C12=18pF。

表1

在很多应用场合,电容精度取5%,从上表可看出它对频率精度的影响可达到28PPM。这在设计中容易被忽略的。

其他因素:如回流焊接的影响,湿度的影响,大气压的影响等。这些因素影响不大,不再这里详述。

晶体振荡总的频率精度就是上述五个方面之和。

- 硅频率控制器(SFC) 晶体替代市场的宠儿(08-30)

- 硅频率控制器(SFC)技术(一)(09-22)

- 硅频率控制器(SFC)技术(三)(09-22)

- 智能铅酸蓄电池充电器的设计(01-02)

- PWM控制电路的基本构成及工作原理(02-23)

- 可对储能器件进行安全且快速充电的通用型电流源(03-13)