将数据转换器IP集成到系统芯片简化设计技术(三)

技术9:尽量减小电源域转换

由于信号沿着时钟网络进展,并在不同的电源域进行转换,信号会受到不同电源的电源噪声耦合的影响。这会导致抖动增加。因此,时钟路径中的所有缓冲器应由同一个电源域(无论是源极电源或终极电源)供应电源。

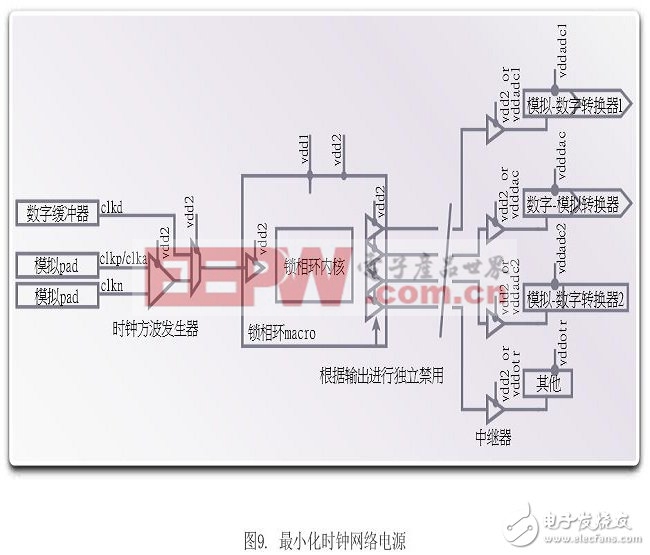

图 9是系统芯片内时钟分布网络的示例。如图所示,锁相环在vdd2电源域生成时钟为四个模块所用,它们是:两个模拟-数字转换器(ADC1和ADC2)、一个数字-模拟转换器和一个通用逻辑块。在这个图中,repeater单元由源极电源(锁相环buffer,vdd2)或是由终极电源(vddadc1、 vdddac、vddadc2或vddotr)供电。

技术10:将时钟信号与攻击信号屏蔽开

将时钟信号与攻击信号屏蔽开,目的是避免噪声与时钟耦合并减少抖动。图10介绍了一种屏蔽信号的方法。在图中,信号路径为M1(蓝线),在各个方向与电路中的其他信号屏蔽开。屏蔽层通常与时钟网络相同的接地电位连接。

4. 保持电源和接地电源干净

任何模拟电路的电源抑制比(PSRR)都是有限的。电源和接地电源噪声过大可能影响性能。处理宽带信号时更是如此,原因是低频率时抑制比高,但高频率时抑制比自然会降低。因此,模拟电源应保持干净,并且使用时应正确去耦合电容。

还有些其他影响,如布线电阻过大可能导致直流(DC)电压压降超出数据转换器工作范围,还可能造成交流(AC)电压响应数据转换器的自生纹波噪声变慢,可以采用以下技术。

技术11:保持电源和接地布线电阻够小

设计师应遵循数据转换器厂商的建议,使电源和接地布线电阻在限制范围内。这些限制的目的是确保数据转换器的电流消耗造成的压降不会使电源电压超出IP的工作范围。此外,如前面所解释的,走线电阻会使自生纹波响应变慢。

技术12:使用专用的电源布线

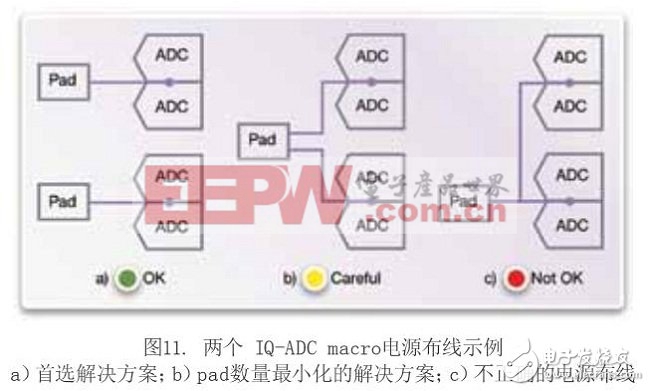

集成多个数据转换器时,设计师应使用专用电源布线,至少包括IO电源。图11a解释了两个IQ-模拟-数字转换器情况下的要求。

对于pad数量受限的系统,只要数据转换器使用相同的时钟频率和相位,多个数据转换器就可以共用相同的IO电源(如图11b所示)。布线必须与I/O电源(采用星形连接)隔离,并保持电源分布对称。图11c图示说明了不正确的电源分布。在这个例子中,电源分布没有保持对称,造成性能降低和串扰。

结论

任何模拟电路的电源抑制比(PSRR)都是有限的。电源和接地电源噪声过大可能影响性能。处理宽带信号时更是如此,原因是低频率时抑制比高,但高频率时抑制比自然会降低。因此,模拟电源应保持干净,并且使用时应正确去耦合电容。

通过在系统芯片设计中选用Synopsys数据转换器IP,设计师将经过优化的数据转换器IP集成在系统芯片中,满足应用要求和应对系统芯片的恶劣环境。

除了选择IP外,IP物理集成部署不正确会影响系统性能。采用本文中的技术有助于系统地解决IP集成挑战。除提供高质量、可靠耐用的数据转换器IP进行系统芯片集成外,Synopsys可在集成过程中提供广泛的工程支持(包括详细的集成指南、集成检查清单和由经验丰富的新思科技应用工程师专门进行集成审核)并简化系统芯片集成过程,有助确保芯片一次成功。

Synopsys具有超过十五年的数据转换IP研发与应用经验,可提供全面的、经硅验证的200多种DesignWare数据转换器IP产品,包括过采样sigma delta模拟-数据转换器、流水线型模拟-数字转换器、逐次逼近型模拟-数字转换器(SAR ADC)和电流舵数字-模拟转换器。DesignWare数据转换器IP产品具有非常低的功率损耗,占用面积小,支持从180纳米到28纳米的制程。

- 新型人机对话接口与音频数据转换器技术及选用(05-23)

- 混合信号系统接地揭秘(07-22)

- 初步了解信号链中的数据转换器(11-17)

- 合适数据转换器选择:JESD204B与LVDS技术对比(09-15)

- Delta-sigma数据转换器的抗混滤波器设计方案(08-06)

- TI:电源创新中的热门趋势(04-15)