一种1.9V供电、8位3.0GSPS A/D转换器设计

,当时钟CLK1为低电平时,节点④被电容N10自举到接近2Vdd的电位,由于节点⑦的电位也近似为2Vdd,故P8截至,同时节点②为低电位,N4管导通,最终使得节点⑥为低电平,NMOS开关N2关断。

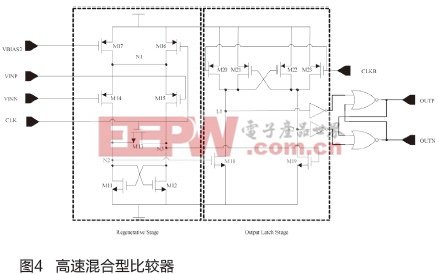

高速混合型比较器

模数转换器通过比较器才能产生最后的输出码,需要数量较多的比较器。比较器会为模数转换器带来延迟、精度、功耗、输入电压范围、输入阻抗以及芯片面积等诸多方面的影响。比较器的性能,特别是速度和精度,会直接决定模数转换器所能够实现的性能。

在高速A/D转换器的设计中,一般都采用动态锁存再生比较器。动态锁存比较器内部包含一个交叉耦合的正反馈回路,从而能够大大地提高比较器的速度。同时由于动态比较器在复位过程中,电路中没有直流通路,所以相对静态比较器,其静态功耗大大减小。这种结构的不足之处是在复位状态和再生状态之间还存在一个过渡状态,用于完成共源节点电位的建立,会影响比较器的再生速度。在再生状态时,比较器电路中会有很大的动态电流,会产生比较大的动态误差。由于本设计前级电路的增益足够大,能够使得比较器自身的失调电压被忽略。因此,在进行比较器的设计时,可放宽对于失调电压的要求,着重提高比较器的再生速度。

本文所设计的比较器如图4所示。CLK为高电平时,M13、M16、M20、M23开启,再生级的N2、N3会被复位到相同的电位。而由于M17被一个预设的直流电平偏置,这时节点N1仍会维持在一个较高的电位。当CLK为低电平时, M13、M16、M20、M23均关闭,比较器工作在再生状态。前级电路的输入VINN、VINP通过M14、M15输入到锁存再生级。M11和M12构成了一组正反馈,正反馈使得N1、N2的输出电位被分离成一组不平衡的输出(一端为高接近VDD,一端为低接近GND)。这一组非平衡的输出经过输出锁存级进一步的调整后,产生最终的比较器输出信号。

与传统的动态锁存式比较器相比,增加了一个由预设直流电平偏置的管子M17,M17会在比较器的工作过程之中一直稳定地提供一个恒定的静态电流,从而大大提高了比较器的再生速度,完全满足本文转换器设计对于比较器速度的要求。

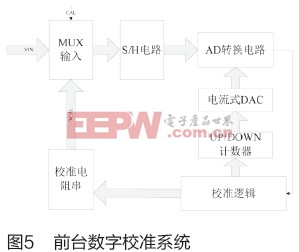

数字校准技术

数字校准技术的应用可以使得在进行超高速A/D转换器设计时,着重注意A/D转换器的速度性能提高,打破按器件匹配进行设计的传统方式。在进行A/D转换器设计时,可以选用更有利于发挥A/D转换器速度优势的器件,将进行失调校正、精度优化的工作由数字校准技术完成。对于超高速折叠内插A/D转换器而言,在选择校准方法时,首先要考虑到其校准的速度要求,在优先保证高速度的前提下,再考虑其精度。因此,本文中的超高速折叠内插A/D转换器采用了前台数字校准方法,结构如图5所示。

其工作过程如下:校准电阻串采用N组间隔均匀的校准矢量电压VCAL,为N个直流电平。输入MUX模拟开关电路为二选一电路,在正常模式下选择外部信号输入,在校准模式下选择矢量电压VCAL输入。校准逻辑模块对校准模块进行逻辑控制和时序控制。可加/可减计数器是校准电路的运算核心,产生的数值将作为电流DAC的码位,并产生对应的调整电流。ADC模块的比较器产生输出信号,这个输入信号作为ADC模块的反馈在校准部分输入,通过对于反馈信号的判断,调整接口DAC的电流大小,从而使得A/D转换器的误差得到补偿,实现电路的校准。由于校准矢量信号依次通过了采保电路和转换电路,故整个模拟通道都得到了校准。

仿真结果

单元电路模块在Spectre仿真条件下进行设计仿真,包括电压拉偏、温度拉偏以及工艺角拉偏仿真等;整体电路的前仿及后仿则全部采用快仿工具完成仿真。转换器电路主要技术指标的仿真结果汇总见表1。

流片及测试结果

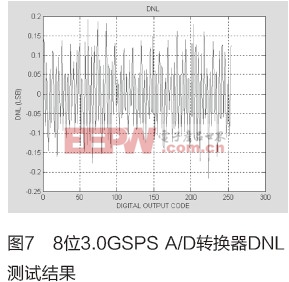

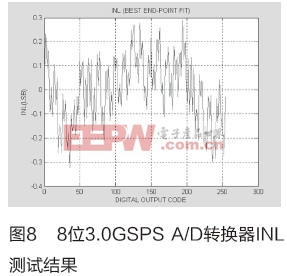

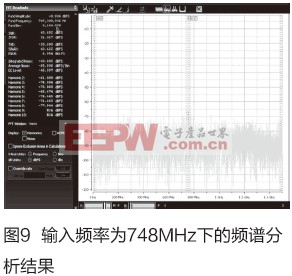

本文设计的8位3.0GSPS A/D转换器晶体管总数约为70万个,整体版图面积约为4.10×4.05mm2,采用0.18μm CMOS工艺流片,选用LQFP144封装,电路照片见图6。图7、图8和图9分别给出了转换器样片典型应用条件下的DNL、INL以及输入为747.390906MHz正弦波信号时的频谱分析结果。从图中可以看出,本文设计的8位3.0GSPS A/D转换器︱DNL︱最大值为0.22LSB,︱INL︱最大值为0.32LSB,常温条件下转换器的有效位为6.95Bits、信噪比达44.10dB、信噪谐波失真比为43.57dB、总谐波失真为-52.68dB、无杂散动态范围为51.18dB,测试指标全部达到或接近仿真结果。

结论

本文采用0.18μm CMOS工艺设计了一款单电源1.9V供电、8位精度、采样速率可达3.0GHz的超高速A/D转换器。仿真及测试结果表明:本文设计的超高速A/D转换器差分非线性误差小于±0.22LSB、积分非线性误差小于±0.3

A D转换器 示波器 量化电路 宽带 比较器 201311 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 利用GM6801实现智能快速充电器设计(11-20)

- 利用阻性负载增强LNA稳定性(中)(11-19)

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)