高功率数字放大器的设计挑战

高功率数字放大器的设计挑战包括:

1) SMPS 问题,包括拓朴及高流量设计等问题;

2) 必须正确指定 SMPS 及高流量信号路径中的重要组件,以处理较高的功率和电流;

3) 印刷电路板 (PCB) 设计问题,包括信号线宽度及电磁波干扰 (EMI)。

SMPS 问题

一般而言,可达到各通道 300 W 的立体声或多通道产品需要能够持续达到 600 W,才能符合美国联邦贸易委员会 (FTC) 现今制定的规定。根据 FTC 的规定,左右声道必须持续五分钟发挥全功率,厂商才能声称此功率为额定功率。由于切开关式电源(SMPS) 是数字放大器目前最普遍使用的电源技术,因此这需要 SMPS 能够提供至少五分钟的600 W功率级 。从散热的角度而言,五分钟是相对较长的时间,实际上,SMPS 必须能够持续达到这一功率。对于此这一高功率,一般建议采用推挽式、半桥式或全桥式 SMPS。

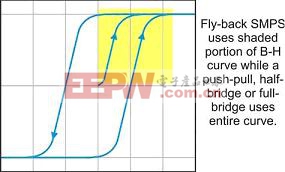

至于低功率 SMPS 设计 (低于 200 W),最常采用反向拓扑。本文不在此细述何以推挽式或半桥式 SMPS 适用于高功率级等,以下仅提供概略说明。在反向 SMPS 中,仅使用一部分的变压器磁性 B-H 曲线 (见图 1),另外,反向 SMPS 的构造较为简易,成本也较为低廉。

图 1. SMPS 变压器磁性的 B-H 迟滞曲线

由于高功率 SMPS 的高电流会在 SMPS 变压器中造成极高的磁通量,因此使用整个 B-H 迟滞回路曲线可降低磁性核心的损耗。推挽式或半桥式拓朴可增加 SMPS 的功率,然而,设计的复杂度及成本也随之增加。

另外也需要更换 SMPS 中使用的组件,才能达到高功率及高电流。而 SMPS 变压器也必须增大,才能处理高功率及高电流。对于 220 VAC 输入,600 W SMPS 的峰值电流可达到 15 安培。对于 110 VAC 设计 (90 VAC 至 136 VAC),则建议在滤波器后使用倍压器或功率因素修正 (PFC),这是因为对于 90 VAC至 136 VAC 输入的 600 W SMPS 而言,输入电流会相当大。其中需要密切监视的组件包括主要输入交流转直流整流器电容,以及辅助 DC 涟波电压消除电容。另外,输入 EMI 线路滤波器也必需能够支持增加的功率负载。

由于设计这些电源供应相当复杂,而且需要专业知识,因此一般建议使用现有的 SMPS 电源供应。

音频信号路径的组件

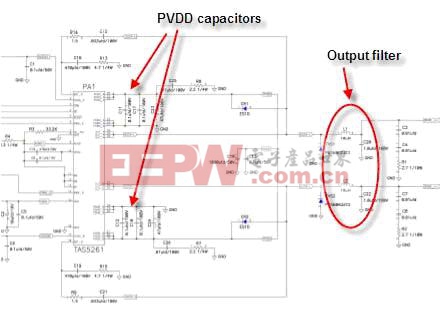

针对较高的纹波电流进行设计则有另外的考虑。例如,根据图 2 显示的电路,在 H-桥电压 (PVDD) 为 50V、使用 10μH 电感且切换频率为 384 kHz 的情况下,使用 TAS5261 的系统所出现的纹波电流可达到 1.6 安培。这表示,输出 LC 滤波器及 PVDD 电容中的电感及电容必须能够处理负载电流及此纹波电流。滤波器电感中出现高电流也表示电感必须有相当低的 DC 电阻 (建议低于 25 毫欧姆),然而,即使电阻相当低,滤波器电感也会出现 I2R 耗损。电感必须能够因应最终造成的温度上升,尤其核心材料更是如此。TAS5261 参考设计包含材料表及特定电感零件编号。

图 2. TAS5261 参考设计的 PVDD 电容及输出 LC 滤波器等组件

PCB 设计问题

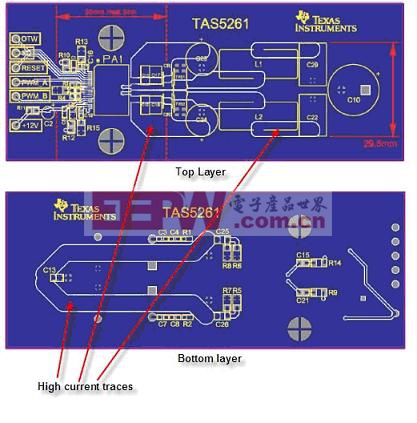

高电流放大器及 SMPS 的 PCB 信号线必须有最小的电阻,才能够将 I2R 耗损降至最低。一般而言,这表示应该使用 2 盎司的铜,并且使信号线尽可能宽。图 3 显示 TAS5261 参考设计 PCB 的信号线。为了将 EMI 及音频性能的问题降至最低,应该尽可能按照其中的配置,并且将这一配置完全不变地应用于功率级的高电压/高功率端。高功率信号线位于顶层的集成电路 (IC) 右侧 (如箭头所示)。图 3 另显示 TAS5261 参考设计的 PCB 配置。

图 3. TAS5261 参考设计 PCB 的高电流信号线范例

数字放大器的全新高瓦数功率级有助于开发更加多样化的产品及应用,本文所述的概念可协助克服进行高功率设计时遭遇的主要挑战。

- 什么是高功率放大器(01-24)

- 兼容标准的高功率PoE系统设计(11-19)

- 高功率LED照明设计师应清楚的5大概念(04-23)

- 基于SVPWM的航空高功率因数整流器设计(08-15)

- 高功率因数低空载损耗AC/DC电源的研究(02-06)

- 便携式电源产品中的电池充电器发展趋势━━高功率和宽范围输入(07-06)