集成同步解调功能的低功耗LVDT信号调理器

以便演示电路的主要特点。E-100冲程范围为±2.54 mm,冲程端输出灵敏度为240 mV/V,满量程范围最大线性度误差为±0.5%,工作频率范围为100 Hz至10 kHz.完整详情请参见E-Series LVDT数据手册。

ADA2200输入耦合网络

可调谐ADA2200输入耦合网络以支持不同的LVDT.LVDT次级绕组电感和分流电容(C4)组成振荡电路。R4和R33电阻降低了振荡电路的Q值,使该电路不易受LVDT绕组电感和电阻的变化影响,但功耗有所上升。R34/C24和R35/C25组成的RC滤波器对可降低信号带宽,同时提供调节电路相对相位所需的额外自由度。ADA2200内部相位敏感检测器(PSD)的最大输出发生在0°或180°相对相移处。

对于采用4.8 kHz方波激励信号的E-100 LVDT而言,采用下列元件值可获得最大输出条件下的最优相位:

●R4 = R33 = 2.2 kΩ

●R34 = R35 = 1 kΩ

●C24 = C25 = 3300 pF

●C4 = 0.01μF

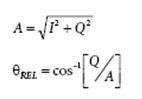

如需调谐该电路,则可通过放置LVDT核心以产生接近满量程输出信号的方式测量相位;然后,测量同相(I)和正交(Q)输出信号。采用这些测量结果便可计算相对相位:

调节网络元件,直到θREL绝对值低于约±3°;这样可以改善电路对于LVDT电气参数变化的灵敏度。

ADC选择和同步

选择AD7192Σ-Δ型ADC,因为该器件支持可配置输出数据速率,并具有各种不同的数字滤波器输出选项,从而允许在带宽和噪声之间进行权衡取舍。主时钟输出功能可轻松实现ADC采样时钟频率与ADA2200输出信号的锁定。这对于优化数字滤波器性能而言是必须的。由LVDT信号确定位置所需的数值是一次激励时钟周期的平均值。因此,当AD7192输出数据速率设为4.8 kHz时,即设为一个激励时钟周期时,可获得所需的平均值。如果激励时钟周期和ADC采样频率未锁定,则恢复的位置测量信息中包含错误。除以输出数据速率便可有效求取多个激励时钟周期的平均值。

ADA2200输出信号哪怕在LVDT核心位置固定的情况下亦含有电能,数值为激励信号频率的倍数。还可在频率域中分析数字滤波器性能。AD7192具有sinc3或sinc4传递函数,该传递函数在输出数据速率的倍数处归零。这些频率分量是杂散误差的来源。通过将ADC的输出数据速率设为激励信号频率(或激励频率的约数)便可抑制输出杂散。如果激励时钟周期和ADC采样频率未锁定,则杂散将不会落在传递函数的零点。

用于性能分析的用户软件

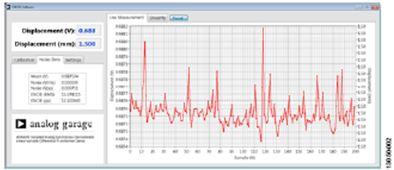

该电路支持图形用户界面,可方便地进行板上的器件配置,并评估电路性能。该软件的选项卡可执行电路校准和器件配置,以及显示噪声性能、线性度性能和实时位置测量。

图2.用户软件屏幕截图

噪声分析

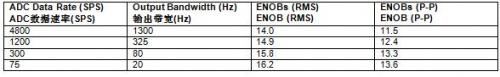

该电路的输出噪声是ADC输出数据速率的函数。表1显示数字化数据相对于ADC采样速率的有效位数(ENOB),假设满量程输出电压为2.5 V.该电路的噪声性能与LVDT核心位置无关。

表1.噪声性能与带宽的关系

如果ADA2200输出噪声与频率无关,则预计有效位数将在输出数据速率每4次折叠下降时增加一位。ENOB在较低输出数据速率下的增加放缓是由于输出驱动器的1/f噪声所导致的;该噪声在较低的输出数据速率下成为噪底的主要成分。

线性度测试结果

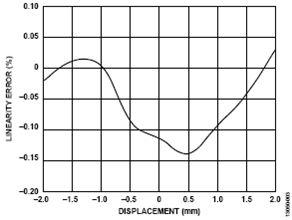

首先在±2.0 mm核心位移处执行一次两点校准即可测量线性度结果。由这两次测量结果可确定斜率和失调,从而实现预期直线拟合。然后,在±2.5 mm满量程范围内测量核心位移。从预期直线拟合数据中减去测量数据即可确定线性度误差。

图3.位置线性度误差与LVDT内核位移的关系

测得的数据显示电路性能优于E-Series LVDT数据手册中指定的线性度性能。

多LVDT同步工作

很多应用都会近距离使用多个LVDT.若这些LVDT以相似的载波频率运行,杂散磁耦合可能导致拍频。产生的拍频可能会影响这些条件下的测量精度。为避免这种情况,所有LVDT必须同步工作。

通过让器件同时退出复位状态,可同步多个ADA2200器件。ADA2200在RST引脚解除置位之后的第一个CLKIN上升沿时退出复位模式。因此,从单一源驱动所有ADA2200 CLKIN引脚以及所有RESETB线路便足以确保器件同步工作。避免在CLKIN上升沿附近对RESETB解除置位,以防器件在不同时钟沿上复位。可监控ADA2200器件的RCLK输出,确保ADA2200器件正确同步。

常见变化

在某些系统中,可能需要使用SAR ADC,而非Σ-Δ型转换器。这些情况下,ADC转换时钟必须与ADA2200更新速率同步。如前所述,ADA2200输出会在激励频率的倍数处含有杂散。这些杂散可通过移动平均滤波器或级联多个移动平均滤波器加以抑制。移动平均滤波器易于实现,且具有出色的时域特性。若

- 精密幅度稳定的低失真正弦波振荡器(03-01)

- 通用LVDT信号调理电路(01-07)

- 经典案例分享,告诉你低成本、低功耗的同步解调器设计没那么难(07-21)

- 线性差动变压器的电路分析(02-18)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)