ADC时钟输入考虑

为了充分发挥芯片的性能,应利用一个差分信号驱动ADC的采样时钟输入端(CLK+和CLK?)。 通常,应使用变压器或电容将该信号交流耦合到CLK+引脚和CLK?引脚内。 这两个引脚有内部偏置,无需其它偏置。

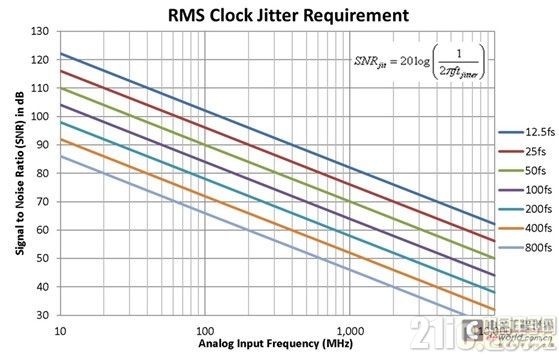

高速、高分辨率ADC对时钟输入信号的质量非常敏感。 为使高速ADC实现出色的信噪比(SNR),必须根据所需的输入频率认真考虑均方根(rms)时钟抖动。 rms时钟抖动可能会限制SNR,哪怕性能最佳的ADC也不例外,输入频率较高时情况会更加严重。 在给定的输入频率(fA)下,仅由孔径抖动(tJ)造成的SNR下降计算公式如下:

SNR = 20 × log10 (2 × π × fA × tJ)

公式中,均方根孔径抖动表示所有抖动源(包括时钟输入信号、模拟输入信号和ADC孔径抖动)的均方根。 中频欠采样应用对抖动尤其敏感,如下图所示。 均方根时钟抖动相同时,若ADC的模拟输入频率提高到三倍,SNR会降低10dB。

图中显示了不同均方根时钟抖动条件下受限于SNR的性能与输入频率的关系。 可注意到,随着输入频率提高,为了实现与较低输入频率下相同的SNR限值,需要降低均方根时钟抖动。 例如,均方根时钟抖动为200fs时,ADC在250MHz时的SNR性能限值为70dB,但1GHz输入信号要实现相同性能,均方根时钟抖动必须为50fs或更低。

理想信噪比与模拟输入频率和抖动的关系

当孔径抖动可能影响ADC的动态范围时,应将时钟输入信号视为模拟信号。 为避免在时钟信号内混入数字噪声,时钟驱动器电源应与ADC输出驱动器电源分离。 如果时钟信号来自其它类型的时钟源(通过门控、分频或其它方法),则应在最后对原始时钟进行重定时。

作者简介: Ian Beavers,ADI公司数字视频处理部(位于美国北卡罗莱纳州格林斯博罗)高级工程师,HDMI及其他视频接口产品组主管。 1999年进入ADI公司,拥有超过15年的半导体行业工作经验。 他拥有美国北卡罗来纳州立大学电气工程学士学位和格林斯博罗分校MBA学位。

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)