通过一个差分接口来延长SPI总线

21ic 讯 通过一个差分接口来延长串行外设接口 (SPI) 总线,而这可以应用在支持远程温度或压力传感器的系统的设计。

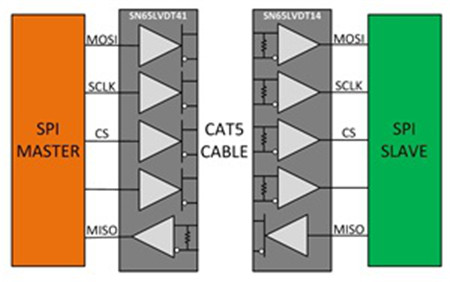

在SPI应用中,主控器件和受控器件间的距离相对较近,而信号也通常不会传递到印刷电路板 (PCB) 之外。SPI信号类似于单端、晶体管-晶体管逻辑 (TTL) 信号,根据应用的不同,运行速率可高达100Mbps。一条SPI总线由四个信号组成:系统时钟 (SCLK) ,主器件输出从器件输入 (MOSI) ,主器件输入从器件输出 (MISO) 和芯片选择 (CS) 。主控器件提供SCLK,MOSI和CS信号,而受控器件提供MISO信号。图1显示了一条标准SPI总线的总线架构。

图1:SPI 总线

如果用户需要将SPI信号从你的微控制器或数字信号处理器 (DSP) 上发送到电路板以外的远程电路板(包含一个模数转换器 (ADC),一个数模转换器 (DAC) 或是其它器件)上,该怎么办呢?

由于以下几个原因,这种操作是具有一定挑战性的。

首先由未端接信号线路所导致的反射会严重影响信号完整性。而传输介质的特性阻抗和端接阻抗差异很大,会导致总线上的阻抗不匹配。其结果将会是从总线一端放射到另一端的能量驻波,从而导致通信误差。电磁干扰 (EMI) 也是一个问题,其原因是SPI信号的高频部分向外放射,导致此信号与邻近信号的混同的。

不过这里有一个简单的解决方法:使用差分信号。诸如SN65LVDT41和SN65LVDT14的差分收发器接收SPI信号,并将它们转换为低压差分信令 (LVDS) 。由于其抗噪性和带宽,LVDS在SPI应用中可以运转良好。一篇之前的《获得连接》博客之前有一篇文章论述了LVDS的基本原理和优势;点击这里查看这篇文章。

SN65LVDT41和SN65LVDT14的架构可以使整条SPI总线转化为支持LVDS:同一方向上用于MOSI,SCLK和CS信号的4个收发器,相反方向上用于MISO信号的1个收发器。LVDS芯片组也具有内置端接带来的额外优势,应用简单,还可以减少电路板空间本就非常宝贵的应用中的组件数量。图2显示的是使用上述芯片组的一个已扩展SPI总线架构的组成结构。这个实现方式并不要求必须使用5类屏蔽双绞线 (STP) ,但是如果使用此类线缆的话,会使这种架构的实现方式更加简单。

图2:已扩展SPI总线

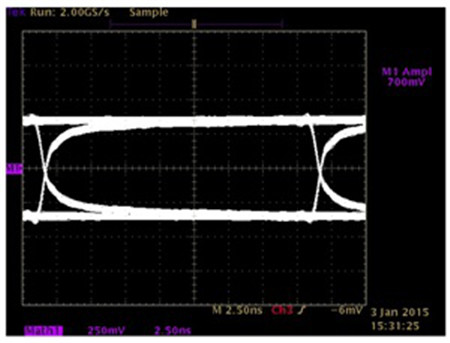

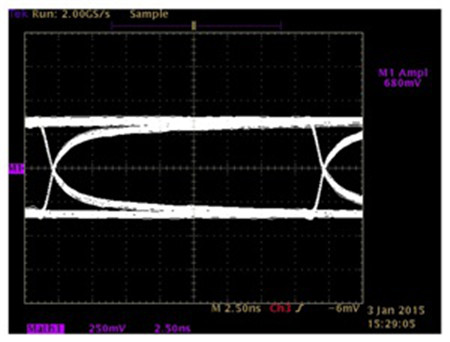

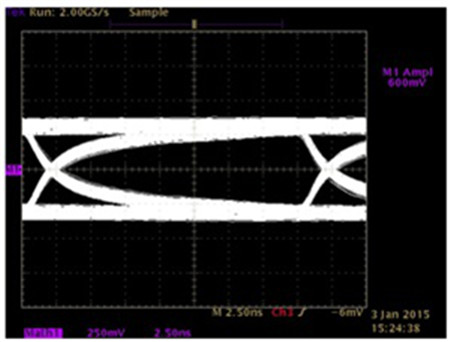

图3,4和5显示了SN65LVDT41和SN65LVDT14发射器在数倍于五类线的长度上发射速度为100Mbps时的性能。SN65LVDT41和SN65LVDT14内的接收器支持200mV输入耐受阀值,处于这些距离和速度下的发射器可以轻松符合这一耐受阀值。

图3:8米五类线100Mbps TX波形

图4:15米五类线100Mbps TX波形

图5:25米五类线100Mbps TX波形

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)