AC耦合电容优化

时间:02-26

来源:互联网

点击:

作者:一博科技SI工程师张吉权

摘要:从系统角度看,随着系统信号速率25Gbps即将到来和未来更高高速率的发展,SerDes(高速串行)信号通道上一个很小阻抗不连续的问题都会带来反射,串扰,模态转换和其它一些影响。这些SI(信号完整性)带来的问题将会使得系统出问题的风险大大增加。AC耦合电容以往被视为对系统影响很小,设计比较随意,但随着10Gbps以及跟高的信号速率,不好的AC耦合电容设计带来的问题将不可忽视。

1.引言

SERDES(串行信号)差分通道上通常都有AC耦合电容。每个电容本身,电容的扇出引线和电容换层过孔都是一个阻抗不连续点。高速串行信号对于阻抗一致性提出非常高的要求,如果阻抗匹配不好将会带来反射,最后影响整个通道的IL (插损), RL(回损), Jitter(抖动)以及 BER(误码率),最终影响整个通道性能。本文从AC耦合电容pad处理以及扇出走线来分析AC耦合电容的设计对通道SI影响。

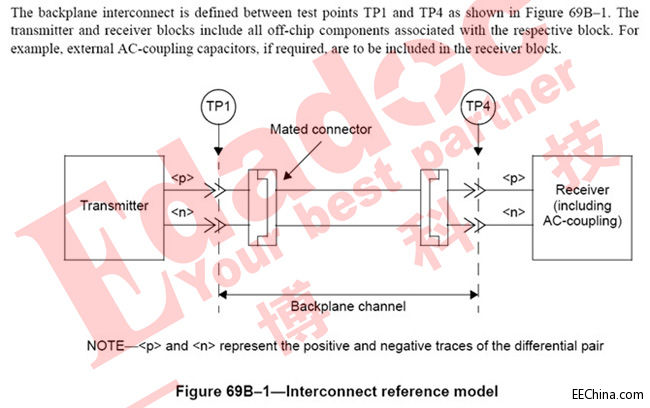

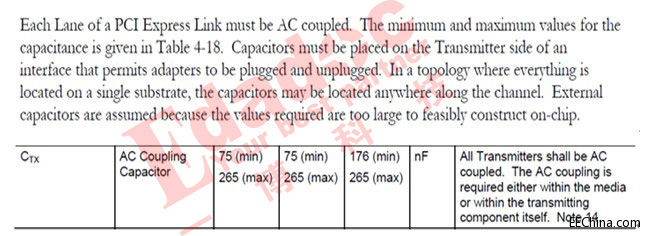

2.AC耦合电容位置及容值大小

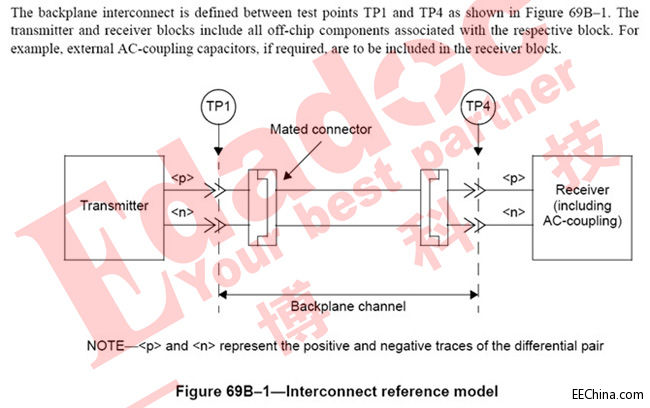

一般来讲AC耦合电容的位置和容值大小都是由信号的协议或者芯片供应商去提供,对于不同信号和不同芯片,其位置和容值大小都是不一样的。比如PCIE信号要求AC耦合电容靠近通道的发送端,SATA信号要求AC耦合电容靠近连接器处,对于10GBASE-KR信号要求AC耦合电容靠近信号通道的接收端。

图2.1 10BASE-KR信号AC耦合电容规范

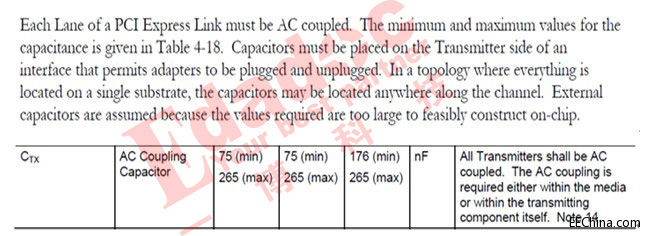

图2.2 PCIE协议对AC耦合电容规范

图2.3 Intel Romley平台SATA信号AC耦合电容位置

图1到图3例举了PCIE ,SATA和KR信号对AC耦合电容位置和容值大小的要求,都各不相同,设计者在设计不同的SerDes信号对于AC耦合电容需要熟悉各类串行信号的协议,理解各信号协议对AC耦合电容的要求,同时需要理解具体芯片对AC耦合电容的要求。

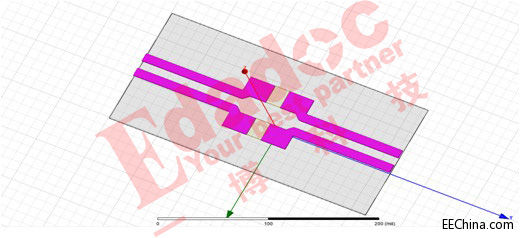

3.仿真优化

3.1.AC耦合电容pad有完整参考面

仿真层叠采用如图3.1所示的6层板层叠,表底层和art04层为走线层,GND1,Art03层和GND5都为参考地平面层。电容pad走在表层,参考第二层的GND平面。如果考虑pad阻抗对pad做优化,会在pad正下方的第二层GND掏空,电容pad将参考第三层的GND平面。

图3.1 仿真层叠

仿真电容信息如下:

电容尺寸:0402封装

pad尺寸:square 20mil*20mil

电容容值:100nf

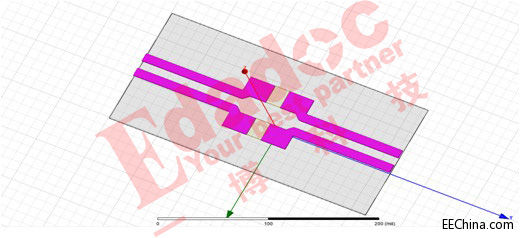

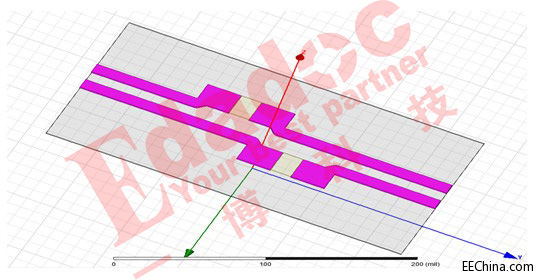

图3.2 电容pad仿真模型

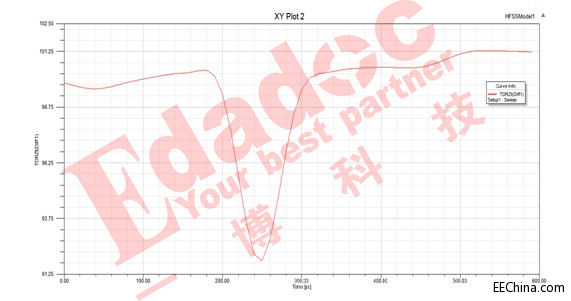

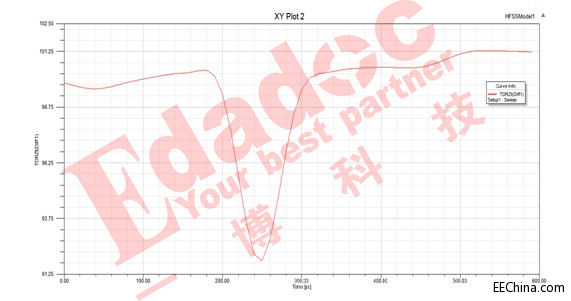

在仿真时候,端口两边各向外延时1000mil线长以方便更好的观察电容pad阻抗不连续性。电容pad TDR仿真结果如下图3.3所示:

图3.3 TDR仿真曲线

在上图中比较平滑的部分为差分线阻抗,中间凹陷下去的地方为电容pad处的阻抗。可以看出差分线的设计阻抗为100ohm,电容pad处由于pad的宽度为20mil,大于走线宽度,而阻抗和线宽是成反比的一种关系,因此pad处阻抗会变小。从图3.3看出在此层叠结构下pad处阻抗约为92ohm。

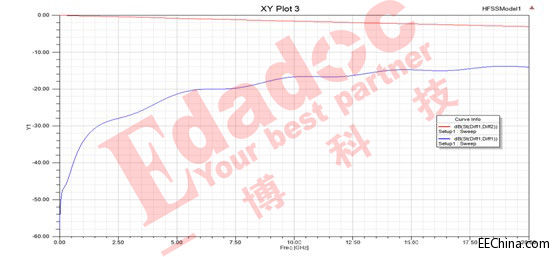

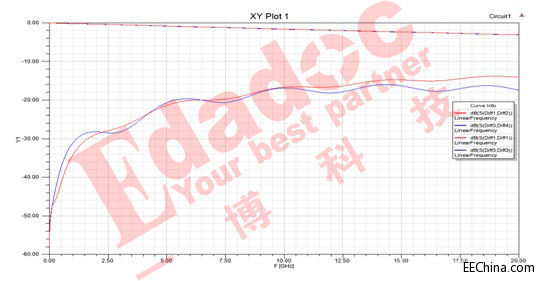

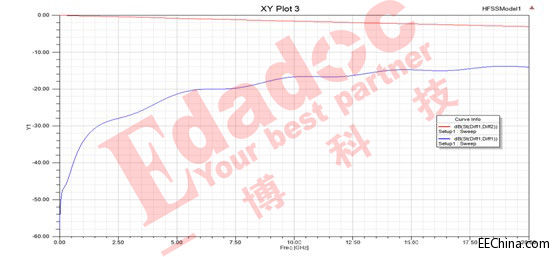

图3.4 插损回损曲线

插损和回损曲线是SerDes信号很重要的系数指标,插损曲线和回损曲线可以很好反应通道损耗以及阻抗不连续性。仿真插损曲线和回损曲线如上图3.4所示。插损和回损曲线可以和后续优化后的曲线做一个简单的对比。

3.2.AC耦合电容pad参考面掏空优化

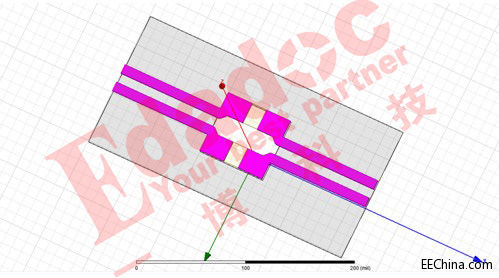

仿真层叠和电容参数和上面完全一样。板子的层叠结构以及板材的介电常数都一定。要增大pad处的阻抗,可以使pad和参考面的距离增大。因此可以把pad正下方的GND2给掏空,电容pad就参考了Art03层的电源平面,这样阻抗就会变大。

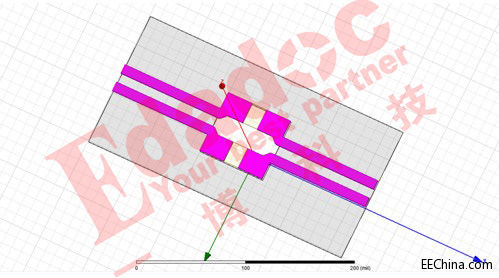

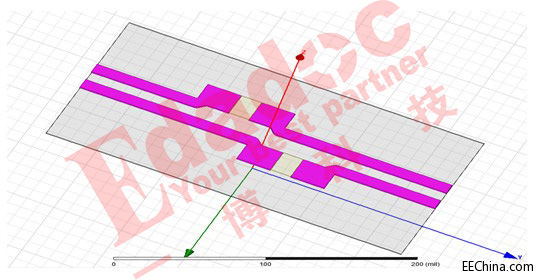

图3.5参考面挖空优化仿真建模

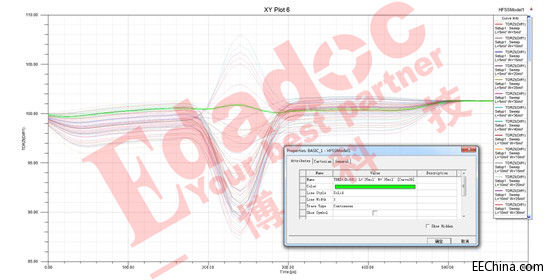

挖空需要挖多大合适呢?传统2D阻抗计算软件无法准确计算出此种情况下的阻抗,采用3D电磁场仿真软件可以准确计算此种情况下的阻抗。对图3.5挖空区域做参数扫描,加上挖空区域为以坐标轴为中心的矩形,长从0到80mil每10mil取一点,宽从0mil到80mil没10mil取一个点。这样一共有64中情况,对这64种情况进行分析的结果如下图3.6所示:

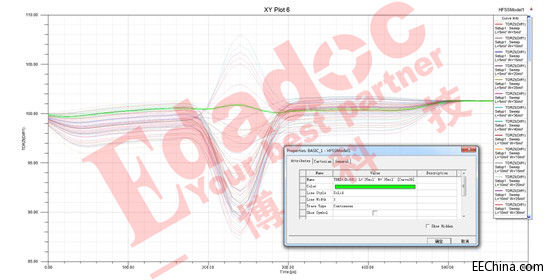

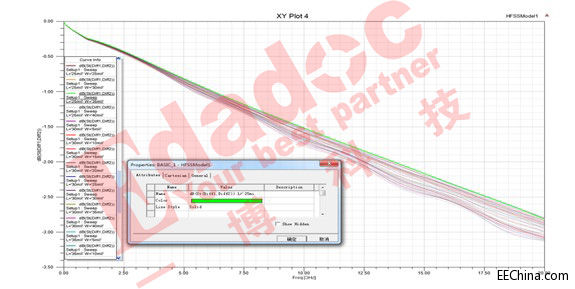

图3.6 TDR扫描结果

从上图3.6可以看出,不同挖空形状对阻抗的影响还是较大。选择一个TDR曲线最平滑的情况,如上图中绿色曲线,可以看出绿色曲线和差分线的阻抗匹配非常好,都几乎为100ohm。去查看挖空面积的参数,长为50mil,宽为70mil的一个矩形,也就是挖空的形状为和电容长度相等,和两个电容并排的宽度稍微宽一点。这样的设计会让通道的阻抗一致性最好。

阻抗通道的一致性越好,其反射会越小,从而带来了插损和回损曲线的改善,最终会使整个系统工作更稳定,下图3.7和图3.8分别为通道的插损和回损曲线的扫描结果。

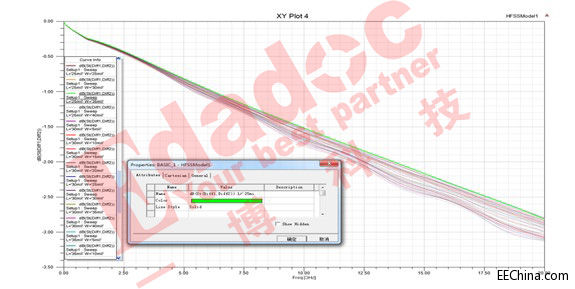

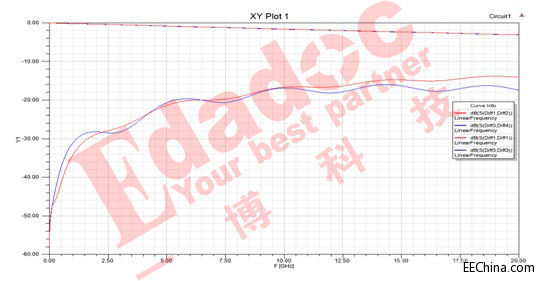

图3.7 插损扫描结果

插损是对信号经过通道能传输部分一个考量,对于PCB串行信号来讲,通常情况下通道插损越小越好,也就是插损曲线越接近0越好。比如对于高速背板,由于走线长,经过连接器和过孔换层,通道的插损就会越大,那么通道就越需要做设计优化以改善通道的插损曲线。

从图3.7可以看出,在2.5Ghz之前,各种情况下的插损曲线几乎重合,电容pad不同的设计对通道的插损几乎没有影响,这也是为什么以前速率较低情况下,AC耦合电容pad设计会比较随意。但随着频率的升高,电容pad之间的偏差会越来越大。能够通过优化电容pad改善通道插损的空间越来越大。绿色插损曲线对应TDR曲线最平滑的那条直线,可以看出在0到20Ghz整个频段内,插损都最接近于0。因此从插损的角度看,这种掏空设计也是最优的设计。

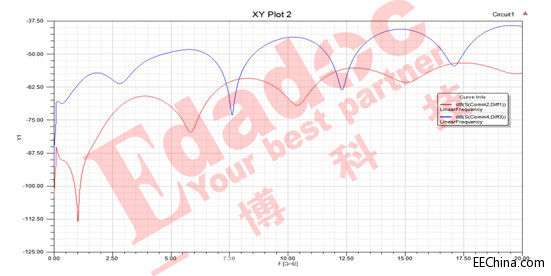

图3.8 回损扫描结果

回损是对信号传输时候遇到阻抗不连续反射回源端信号的度量。从能量守恒看反射越多传输到接收芯片的就越少。因此在设计的时候都尽量使回损曲线远离0。从回损曲线看,不同设计差别同样很大,绿色的曲线同样对应TDR曲线最平滑的情况。从回损看,也是此种设计较优。

3.3.AC耦合电容位置不对称

差分信号在设计时候需要尽量做到对称,任何不对称的因素都会使得部分差分信号转换为共模信号。对于共模信号而言,信号和参考面的耦合和回流路径一旦处理不好,都会成为EMI的潜在威胁。

图3.9 AC耦合电容不对称

通过仿真可以明显看到不对称的电容摆放会带来更多的共模信号,而不对称摆放对插损回损影响不大。

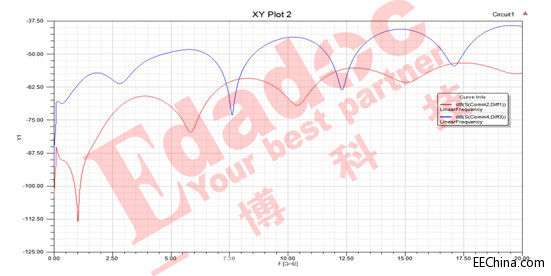

图3.10插损和回损结果

图3.10为电容对称和不对称摆放的一个对比结果,红色为对称摆放,蓝色为不对称,可以看到插损曲线几乎重合,回损曲线只有很细微的差别。总的来说插损和回损影响都不是很大。

图3.11 差模转共模

图3.11为电容对称和不对称摆放的差模转共模一个对比,同样红色为对称摆放,蓝色为不对称,可以看出不对称将带来更多共模信号,将对EMI带来潜在的威胁。

3.4.时域波形对比

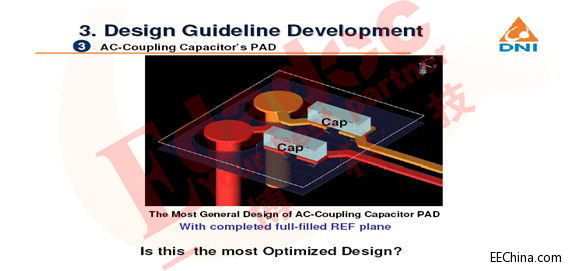

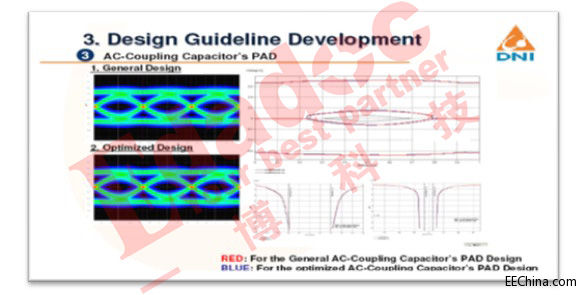

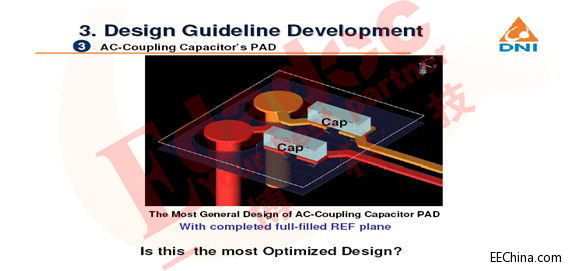

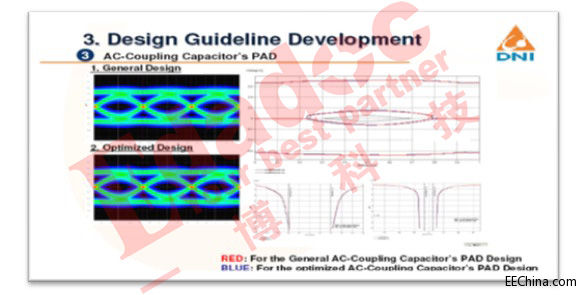

时域波形是判断信号质量好坏最直观的表现。通过对AC耦合电容pad优化,最终会体现在时域波形的改善上。图3.12和图3.13是引用DNI的文档。

图3.12 DNI关于电容优化

图3.13 DNI电容优化后时域波形改善

从图13可以看出,通过对电容pad优化可以对眼图以及浴盆曲线都会有所改善。浴盆曲线直接体现了在相同眼宽的情况下误码率更低。更低的误码率从而保证了系统工作更加稳定。

小结

本文分析了AC耦合电容的pad优化对阻抗TDR曲线,IL&RL,差模转共模以及时域眼图分析可以得出,在更高速度SerDes信号中,AC耦合电容pad优化会改善通道的性能参数。在设计时候丰富的工程经验加上3D电磁场仿真软件可以准确的优化AC耦合电容的pad,使电容pad和传输线以及过孔阻抗一致性最好,使得设计的产品更能满足设计需求。

摘要:从系统角度看,随着系统信号速率25Gbps即将到来和未来更高高速率的发展,SerDes(高速串行)信号通道上一个很小阻抗不连续的问题都会带来反射,串扰,模态转换和其它一些影响。这些SI(信号完整性)带来的问题将会使得系统出问题的风险大大增加。AC耦合电容以往被视为对系统影响很小,设计比较随意,但随着10Gbps以及跟高的信号速率,不好的AC耦合电容设计带来的问题将不可忽视。

1.引言

SERDES(串行信号)差分通道上通常都有AC耦合电容。每个电容本身,电容的扇出引线和电容换层过孔都是一个阻抗不连续点。高速串行信号对于阻抗一致性提出非常高的要求,如果阻抗匹配不好将会带来反射,最后影响整个通道的IL (插损), RL(回损), Jitter(抖动)以及 BER(误码率),最终影响整个通道性能。本文从AC耦合电容pad处理以及扇出走线来分析AC耦合电容的设计对通道SI影响。

2.AC耦合电容位置及容值大小

一般来讲AC耦合电容的位置和容值大小都是由信号的协议或者芯片供应商去提供,对于不同信号和不同芯片,其位置和容值大小都是不一样的。比如PCIE信号要求AC耦合电容靠近通道的发送端,SATA信号要求AC耦合电容靠近连接器处,对于10GBASE-KR信号要求AC耦合电容靠近信号通道的接收端。

图2.1 10BASE-KR信号AC耦合电容规范

图2.2 PCIE协议对AC耦合电容规范

图2.3 Intel Romley平台SATA信号AC耦合电容位置

图1到图3例举了PCIE ,SATA和KR信号对AC耦合电容位置和容值大小的要求,都各不相同,设计者在设计不同的SerDes信号对于AC耦合电容需要熟悉各类串行信号的协议,理解各信号协议对AC耦合电容的要求,同时需要理解具体芯片对AC耦合电容的要求。

3.仿真优化

3.1.AC耦合电容pad有完整参考面

仿真层叠采用如图3.1所示的6层板层叠,表底层和art04层为走线层,GND1,Art03层和GND5都为参考地平面层。电容pad走在表层,参考第二层的GND平面。如果考虑pad阻抗对pad做优化,会在pad正下方的第二层GND掏空,电容pad将参考第三层的GND平面。

图3.1 仿真层叠

仿真电容信息如下:

电容尺寸:0402封装

pad尺寸:square 20mil*20mil

电容容值:100nf

图3.2 电容pad仿真模型

在仿真时候,端口两边各向外延时1000mil线长以方便更好的观察电容pad阻抗不连续性。电容pad TDR仿真结果如下图3.3所示:

图3.3 TDR仿真曲线

在上图中比较平滑的部分为差分线阻抗,中间凹陷下去的地方为电容pad处的阻抗。可以看出差分线的设计阻抗为100ohm,电容pad处由于pad的宽度为20mil,大于走线宽度,而阻抗和线宽是成反比的一种关系,因此pad处阻抗会变小。从图3.3看出在此层叠结构下pad处阻抗约为92ohm。

图3.4 插损回损曲线

插损和回损曲线是SerDes信号很重要的系数指标,插损曲线和回损曲线可以很好反应通道损耗以及阻抗不连续性。仿真插损曲线和回损曲线如上图3.4所示。插损和回损曲线可以和后续优化后的曲线做一个简单的对比。

3.2.AC耦合电容pad参考面掏空优化

仿真层叠和电容参数和上面完全一样。板子的层叠结构以及板材的介电常数都一定。要增大pad处的阻抗,可以使pad和参考面的距离增大。因此可以把pad正下方的GND2给掏空,电容pad就参考了Art03层的电源平面,这样阻抗就会变大。

图3.5参考面挖空优化仿真建模

挖空需要挖多大合适呢?传统2D阻抗计算软件无法准确计算出此种情况下的阻抗,采用3D电磁场仿真软件可以准确计算此种情况下的阻抗。对图3.5挖空区域做参数扫描,加上挖空区域为以坐标轴为中心的矩形,长从0到80mil每10mil取一点,宽从0mil到80mil没10mil取一个点。这样一共有64中情况,对这64种情况进行分析的结果如下图3.6所示:

图3.6 TDR扫描结果

从上图3.6可以看出,不同挖空形状对阻抗的影响还是较大。选择一个TDR曲线最平滑的情况,如上图中绿色曲线,可以看出绿色曲线和差分线的阻抗匹配非常好,都几乎为100ohm。去查看挖空面积的参数,长为50mil,宽为70mil的一个矩形,也就是挖空的形状为和电容长度相等,和两个电容并排的宽度稍微宽一点。这样的设计会让通道的阻抗一致性最好。

阻抗通道的一致性越好,其反射会越小,从而带来了插损和回损曲线的改善,最终会使整个系统工作更稳定,下图3.7和图3.8分别为通道的插损和回损曲线的扫描结果。

图3.7 插损扫描结果

插损是对信号经过通道能传输部分一个考量,对于PCB串行信号来讲,通常情况下通道插损越小越好,也就是插损曲线越接近0越好。比如对于高速背板,由于走线长,经过连接器和过孔换层,通道的插损就会越大,那么通道就越需要做设计优化以改善通道的插损曲线。

从图3.7可以看出,在2.5Ghz之前,各种情况下的插损曲线几乎重合,电容pad不同的设计对通道的插损几乎没有影响,这也是为什么以前速率较低情况下,AC耦合电容pad设计会比较随意。但随着频率的升高,电容pad之间的偏差会越来越大。能够通过优化电容pad改善通道插损的空间越来越大。绿色插损曲线对应TDR曲线最平滑的那条直线,可以看出在0到20Ghz整个频段内,插损都最接近于0。因此从插损的角度看,这种掏空设计也是最优的设计。

图3.8 回损扫描结果

回损是对信号传输时候遇到阻抗不连续反射回源端信号的度量。从能量守恒看反射越多传输到接收芯片的就越少。因此在设计的时候都尽量使回损曲线远离0。从回损曲线看,不同设计差别同样很大,绿色的曲线同样对应TDR曲线最平滑的情况。从回损看,也是此种设计较优。

3.3.AC耦合电容位置不对称

差分信号在设计时候需要尽量做到对称,任何不对称的因素都会使得部分差分信号转换为共模信号。对于共模信号而言,信号和参考面的耦合和回流路径一旦处理不好,都会成为EMI的潜在威胁。

图3.9 AC耦合电容不对称

通过仿真可以明显看到不对称的电容摆放会带来更多的共模信号,而不对称摆放对插损回损影响不大。

图3.10插损和回损结果

图3.10为电容对称和不对称摆放的一个对比结果,红色为对称摆放,蓝色为不对称,可以看到插损曲线几乎重合,回损曲线只有很细微的差别。总的来说插损和回损影响都不是很大。

图3.11 差模转共模

图3.11为电容对称和不对称摆放的差模转共模一个对比,同样红色为对称摆放,蓝色为不对称,可以看出不对称将带来更多共模信号,将对EMI带来潜在的威胁。

3.4.时域波形对比

时域波形是判断信号质量好坏最直观的表现。通过对AC耦合电容pad优化,最终会体现在时域波形的改善上。图3.12和图3.13是引用DNI的文档。

图3.12 DNI关于电容优化

图3.13 DNI电容优化后时域波形改善

从图13可以看出,通过对电容pad优化可以对眼图以及浴盆曲线都会有所改善。浴盆曲线直接体现了在相同眼宽的情况下误码率更低。更低的误码率从而保证了系统工作更加稳定。

小结

本文分析了AC耦合电容的pad优化对阻抗TDR曲线,IL&RL,差模转共模以及时域眼图分析可以得出,在更高速度SerDes信号中,AC耦合电容pad优化会改善通道的性能参数。在设计时候丰富的工程经验加上3D电磁场仿真软件可以准确的优化AC耦合电容的pad,使电容pad和传输线以及过孔阻抗一致性最好,使得设计的产品更能满足设计需求。

- LT3751如何使高压电容器充电变得简单(08-12)

- 2A超级电容器充电器平衡和保护便携式应用中的超级电容器(11-01)

- 电容器与声音的关系(11-04)

- 升压电源与高压天线和滤波器提供调谐信号(01-28)

- 电容降压LED驱动电路(06-24)

- 一种无电解电容LED驱动方案中输出功率的测量(06-10)