转向使用即插即用的分层 DFT 的好处

时间:10-24

来源:互联网

点击:

- 内核层面的模式生成

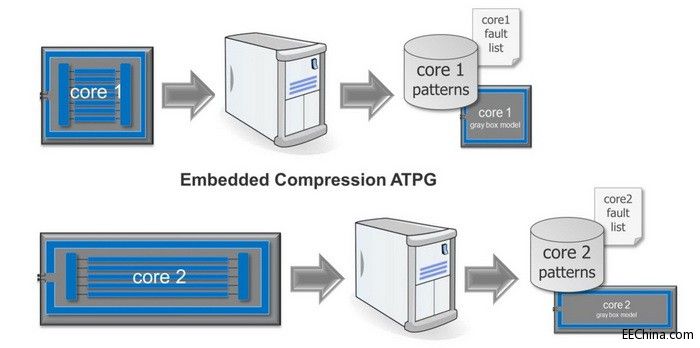

一旦包装器链、内部扫描链和嵌入式压缩被插入一个内核,那么它随时可进行ATPG。如前所述,分层 DFT 的优点是,内核 DFT 和 ATPG 的进行能够完全独立于其他内核(图2)。即便 IO 值未知,包装器链也能使 ATPG 实现高覆盖率。 ATPG 工具只需要得到测试图形将重定向的指示,这样未知值就可以通过IO赋值,同时恰当的数据被存出来,这些恰当的数据包括需要在IC顶层验证的任何时钟或被约束引脚。

图2:利用分层测试方法,所有区块的 ATPG 工作可以在各内核上独立完成。

如果一个内核在设计中被数次使用,那么该内核的 ATPG 只需要完成一次。重定向步骤可以将该测试图案数据并行应用于所有 区块。使用这种方法,只要内核设计完成,内核级 DFT 逻辑和测试图案验证即可完成。

将内核测试图案重定向并整合到顶层

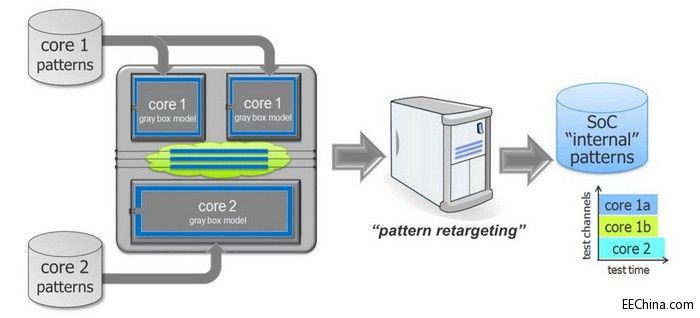

分层 DFT 方法可以便捷地实现顶层 IC 的测试图案整合。第一步是执行一些基本的 DFT 设计规则检查(DRC)。完成这一步只需要有顶层网表和所有内核的灰盒模型(图3)。分层 DFT 方法常常使用IC 层测试访问机制(TAM),将芯片的IO定向到需要测试的特殊区块或区块组。它既可以简单到只需要几个多路复用器,也可以复杂得多。复用的内核通常有并联广播到所有内核的输入信道,这样从一套输入信道就得到同样的测试。我们比较建议将TAM建立在 IJTAG 的基础上,因为IJTAG是一个非常广泛而灵活的标准,也最适用于即插即用。

图3:模式重定向需要独立生成的内核测试图案,并对其进行重新定向,使之可以从IC层执行。这张图显示了被重定向并整合的三个内核测试图案,使其并行执行。对于一个典型的 IC来讲,会有一些区块的测试图案被整合,而另一部分区块需要被放到另一阶段进行测试。

具有TAM和内核灰盒的设计图要比完整的网表小得多,但它已经能够提供足够多的与内核 IO 和 DFT 逻辑相关的信息,可以进行完整的设计规则检查。一旦完成设计规则检查,内核测试图案可以自动重新定向,使之得以在IC层执行。尽管内核层测试图案是独立生成的,测试图案重定向可以整合并应用它们,只要 TAM 允许对区块进行并行访问,它们就可以并行执行,。

分层方法的最后一步是生成测试各内核之间互连的IC层测试图案。灰盒模型在这里被应用。它是设计后期的 ATPG 步骤,因为所有内核设计和 TAM 首先必须在此之前完成。然而,它是一个很简单的电路,ATPG 应该是快速而简单的。

下一步是什么?

分层 DFT的扫描和包装器插入、灰盒生成和测试图案重定向等基本特性为许多设计提供了一个显著优势。但是选择哪些模块并行测试,哪些串行测试,使测试效率得到优化还需要很多做很多工作。有效的顶层规划要求一些内核测试图案信息必须是有效的。与帮助确定最佳压缩配置的压缩分析的功能类似,顶层 TAM 规划在内核设计可用时更为高效。针对这个问题正在开发的方法之一是将IC信道带宽动态分配给各个内核。这样的话,在设计TAM前就不需要知道内核测试图案的性质。此外,动态分配扫描信道将减少整个测试图案集的大小。

总而言之,分层DFT方法正在被许多设计所采用。因为 ATPG 只在内核级进行,它显著加快了 ATPG 的速度,降低了工作站的规模。这对于数亿门或以上的超大规模设计来说至关重要。分层 DFT 的另一大优点是它很大程度上改进了工序,带来了即插即用的便利。因此,只要内核设计完成,那么更多的 DFT 和 ATPG 工作可以在设计周期的更早阶段进行,这些都有利于降低风险、提高可预见性、以及后期的 ECO。

作者简介

Ron Press 是明导硅测试解决方案产品的的技术营销经理。他在测试和 DFT(可测性设计)行业有着25年的经验,曾多次出席全球各地的DFT和测试研讨会。他出版了数十篇与测试相关的论文,是国际测试会议 (ITC) 指导委员会的成员,IEEE 计算机学会 (IEEE Computer Society) 的 Golden Core 成员,IEEE 的高级会员。Ron拥有多项减少引脚数测试和无干扰时钟切换的专利。

- 内核层面的模式生成

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)

- 嵌入式系统实时性的问题(06-21)

- 嵌入式实时系统中的优先级反转问题(06-10)

- 嵌入式Linux系统中MMC卡驱动管理技术研究(06-10)

- FPGA的DSP性能揭秘(06-16)