多重图案微影技术的未来发展前景

时间:10-17

来源:互联网

点击:

作者:明导高级物理验证方法项目经理David Abercrombie

曾经,我花了大量时间谈论双重图案微影技术。我认为是时候开始展望多重图案微影的发展前景了(不要惊慌!)。正如您可能听过或者读过的一样,极紫外光微影(EUV Lithography)技术似乎赶不上10nm节点的进度,甚至无法达到7nm。这意味着为了保持行业向前发展,必须采用替代型方法来拓展现有的微影工具集。

20nm工艺节点首次向设计界推出了多重图案微影技术。活性层、接触层、过孔层和下面的金属层开始在这个节点利用双微影蚀刻(LELE)间距分割法双重图案微影(DP)工艺。这就是我的所有其它博客谈论的DP工艺流程。LELE需要将DP层分割(分离)成两个光罩进行生产制造。在一些晶圆厂,设计师需要形成这两个分离的光罩层,这是晶圆厂流片工艺的一部分。在其它晶圆厂,设计师无需进行分离,但是他们进行严格部署时必须进行专门的双重图案微影检查,确保当设计在晶圆厂流片时能够进行双层分离。无论哪种情况,设计师都必须进行与这些将要分离成两个光罩的层相关的任务,而之前的节点并不需要这些流程。

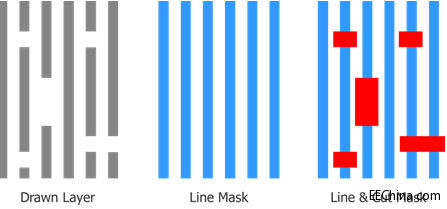

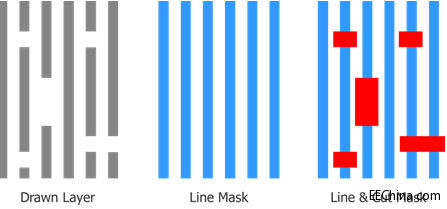

有趣的是20nm工艺节点的多晶硅(门)层也使用两个光罩,但是分离的方式与其它DP层所需的LELE流程不同。它使用一个线条/切割流程。多晶硅层必须严格包含单向运行线路。这些线条全部使用第一个“线条”光罩定义。无论线条里哪儿有空隙(间隔),则使用第二个“切割”光罩来定义这些空隙。图一是这个线条/切割双光罩分离流程的示例。

图1:线条/切割双光罩分离流程示例

这个工艺设计人员看不到,因为他们不画这两个光罩或者对这个流程进行任何类型的特殊分离检查。严格的分层设计规则确保在晶圆厂生成这两个光罩成为可能。因为这个双重图案微影设计师根本看不见,因此你很少听到有人谈及。

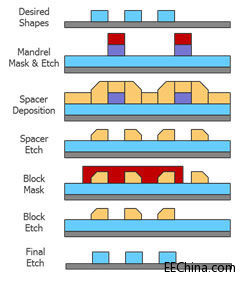

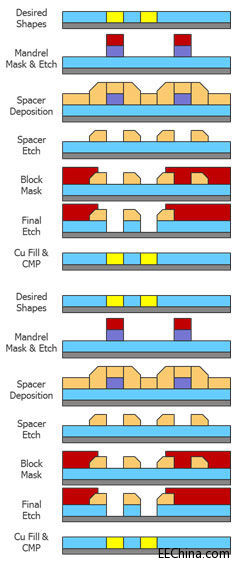

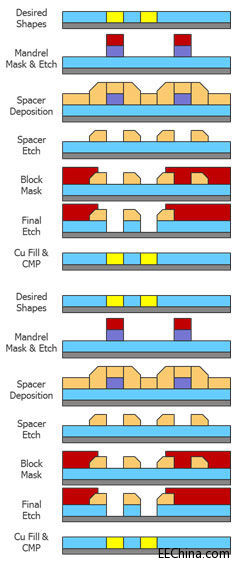

在多重图案微影方面,16/14nm技术节点的情况似乎与20nm节点非常相似。这种一致性主要由于这个节点并非从20nm真正缩至16/14nm。内部连接层跟20nm一样,因此相同的DP流程可以用于生产他们。唯一重要的变化是新的finFET晶体管,它不仅是一个新型的晶体管而且尺寸有所缩小。除了活性层和多晶硅层之外,这个晶体管需要一个全新的层(肋片层 )。肋片层本质上是一系列与多晶硅层垂直的平行线。事实证明这些线条的强度(线条/间隔)还需要一些DP类型进行生产。晶圆厂推出了一款新的DP工艺spacer-is-mask(简称“SIM”),它是一种自动校准双重图案微影技术。与LELE间距分割和线条/切割工艺类似,SIM也需要两个光罩进行生产,但是工艺与LELE或者线条/切割双重图案微影技术有很大不同。图2是SIM流程的一个示例。

图2:用于肋片层的SIM SADP工艺流程示例

正如你在工艺流程图上看到的一样,两个光罩(“心轴”和“遮挡”)看起来和作为设计师布局草图一部分的最终理想形状极为不同。这种差异是因为最终形状并不是直接由光罩形状界定。隔离层沉积和蚀刻之间的残差形成了最终的“光罩”模式。幸运的是,对于进行16/14nm布局的设计师而言,整个一代肋片层是隐藏的。设计师只需画出传统的主动区和非主动区(“栅极”)层。尽管在以前节点中没出现的这些层有其它限制,这些主动区层只能是不同长度的离散单元,这些限制根据传统的设计规则实施。这些严格受限的布局层限制确保了晶圆厂能够轻松导出完成新晶体管结构所需的相应肋片层。

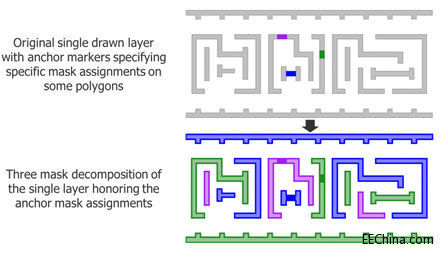

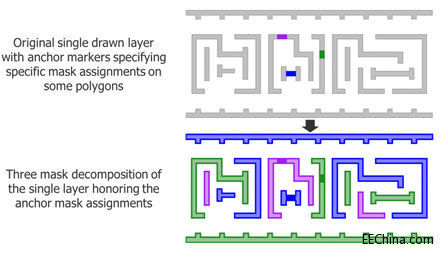

至于10nm工艺节点,多重图案的变化并不利于设计师。除了16/14nm中使用的所有技术,10nm节点带来了至少两个新的多重图案技术。第一个技术是三重双微影蚀刻间距分割法三重图案微影工艺。是的,两个不够的时候,为什么不用三个呢?这个工艺与20/16/14nm中使用的双微影蚀刻间距分割法工艺十分类似,除了三重图案微影工艺需要原始层在三个不同的光罩中分解这点。与双重图案微影工艺一样,当你结合三个光罩中的所有形状时,它看起来又像原始的单层了。三重图案微影工艺可用于接触、再分配互联和/或M1这样的层。图3显示了三重图案微影工艺分解示例。

图3:三个光罩三重图案微影工艺分解

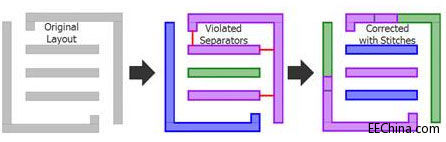

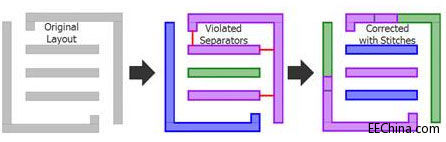

由于这个工艺类似于20/16/14nm双重图案微影工艺,设计师可能会发现很多类似之处,这会使转变到三重图案微影工艺更容易。即使是使用缝合这样的固定解决方案,对于这个工艺而言理论上也是可行的。图4显示了一个布局示例,这个布局在三个光罩中不能自然分解,但可以通过利用缝合成功分解。

图4:三重图案微影工艺分解错误利用缝合进行纠正

尽管三重图案微影和双重有相似之处,但也有很多不同,因此对设计师、代工厂和电子设计自动化工具而言带来了巨大的挑战。我将在今后的文章后详细介绍这些挑战。

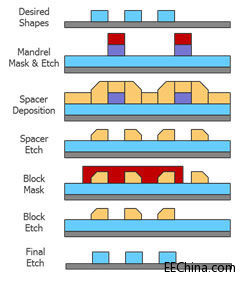

10nm工艺也带来了SID版SADP,这可用于部分金属互联层。正如SIM版SADP用于16/14nm工艺一样,这两个光罩和布局中原始草图形状不一样,但利用了隔离层沉积和蚀刻之间的残差来界定形状。但在SID版SADP中,隔离层并不界定行数,而是行数之间的间距。图5显示了利用SID版SADP的金属工艺示例。

图5:用于金属互联层的SID SADP工艺。

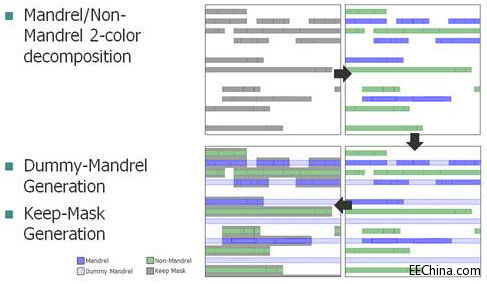

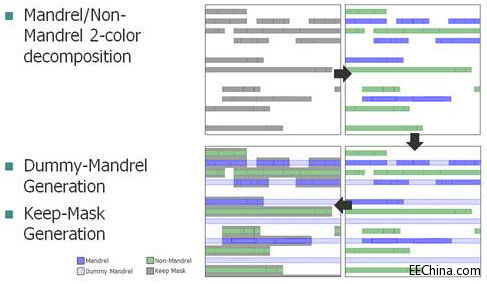

与用于16/14nm肋片层的SIM SADP工艺不同,更复杂的双向层(例如金属互联层)所采用的SID SADP工艺对于设计师而言是不容忽视的。这项工艺将需要设计师了解并适应一些新要求。此外也给晶圆代工和EDA工具带来了新的挑战。别担心——我在接下来的文章中将进一步讨论这些挑战。现在,让我们简单来看看一个金属布局示例以及它如何分解成两个光罩(图6)。

图6:金属布局分解成SID SADP的两个光罩。

从这个示例中可以看出光罩分解过程分为三个主要步骤:

原始的单层被拆分为两种“颜色”——心轴和无心轴。

新增的“虚拟心轴”多边形被分配给心轴颜色。最终的心轴和虚拟心轴形状组合形成第一个“心轴光罩”。

形成的保持层最终将倒转过来,形成最终的“遮挡光罩”。现在来看,心轴和遮挡光罩如何形成类似晶圆原始导出层的东西可能还不明显,但相信我,它可以的。我们将在另一篇文章中花更多时间来介绍这个过程。

我只想说,如果您想要着手进行任何10nm设计工作,您可能需要再学习一些有关多重图案微影的知识。很幸运,我可以为您排忧解难。至少,关于可预见的未来,我有很多想法可以与您分享!我期待帮助您完成这个学习的过程。现在,让我来简单概括一下多重图案微影领域每个工艺节点的相关知识。

●20nm:

用于多晶层的线条/切割双光罩工艺(对设计师无影响)

用于活性层、接触层、通孔层和金属层的LELE DP工艺(对设计师有影响)

●16nm:

用于肋片层的SIM SADP(对设计师无影响)

●10nm:

用于一些接触层和互联层的LELELE TP工艺(对设计师有影响)

用于一些金属互联层的SID SADP(对设计师有影响)

曾经,我花了大量时间谈论双重图案微影技术。我认为是时候开始展望多重图案微影的发展前景了(不要惊慌!)。正如您可能听过或者读过的一样,极紫外光微影(EUV Lithography)技术似乎赶不上10nm节点的进度,甚至无法达到7nm。这意味着为了保持行业向前发展,必须采用替代型方法来拓展现有的微影工具集。

20nm工艺节点首次向设计界推出了多重图案微影技术。活性层、接触层、过孔层和下面的金属层开始在这个节点利用双微影蚀刻(LELE)间距分割法双重图案微影(DP)工艺。这就是我的所有其它博客谈论的DP工艺流程。LELE需要将DP层分割(分离)成两个光罩进行生产制造。在一些晶圆厂,设计师需要形成这两个分离的光罩层,这是晶圆厂流片工艺的一部分。在其它晶圆厂,设计师无需进行分离,但是他们进行严格部署时必须进行专门的双重图案微影检查,确保当设计在晶圆厂流片时能够进行双层分离。无论哪种情况,设计师都必须进行与这些将要分离成两个光罩的层相关的任务,而之前的节点并不需要这些流程。

有趣的是20nm工艺节点的多晶硅(门)层也使用两个光罩,但是分离的方式与其它DP层所需的LELE流程不同。它使用一个线条/切割流程。多晶硅层必须严格包含单向运行线路。这些线条全部使用第一个“线条”光罩定义。无论线条里哪儿有空隙(间隔),则使用第二个“切割”光罩来定义这些空隙。图一是这个线条/切割双光罩分离流程的示例。

图1:线条/切割双光罩分离流程示例

这个工艺设计人员看不到,因为他们不画这两个光罩或者对这个流程进行任何类型的特殊分离检查。严格的分层设计规则确保在晶圆厂生成这两个光罩成为可能。因为这个双重图案微影设计师根本看不见,因此你很少听到有人谈及。

在多重图案微影方面,16/14nm技术节点的情况似乎与20nm节点非常相似。这种一致性主要由于这个节点并非从20nm真正缩至16/14nm。内部连接层跟20nm一样,因此相同的DP流程可以用于生产他们。唯一重要的变化是新的finFET晶体管,它不仅是一个新型的晶体管而且尺寸有所缩小。除了活性层和多晶硅层之外,这个晶体管需要一个全新的层(肋片层 )。肋片层本质上是一系列与多晶硅层垂直的平行线。事实证明这些线条的强度(线条/间隔)还需要一些DP类型进行生产。晶圆厂推出了一款新的DP工艺spacer-is-mask(简称“SIM”),它是一种自动校准双重图案微影技术。与LELE间距分割和线条/切割工艺类似,SIM也需要两个光罩进行生产,但是工艺与LELE或者线条/切割双重图案微影技术有很大不同。图2是SIM流程的一个示例。

图2:用于肋片层的SIM SADP工艺流程示例

正如你在工艺流程图上看到的一样,两个光罩(“心轴”和“遮挡”)看起来和作为设计师布局草图一部分的最终理想形状极为不同。这种差异是因为最终形状并不是直接由光罩形状界定。隔离层沉积和蚀刻之间的残差形成了最终的“光罩”模式。幸运的是,对于进行16/14nm布局的设计师而言,整个一代肋片层是隐藏的。设计师只需画出传统的主动区和非主动区(“栅极”)层。尽管在以前节点中没出现的这些层有其它限制,这些主动区层只能是不同长度的离散单元,这些限制根据传统的设计规则实施。这些严格受限的布局层限制确保了晶圆厂能够轻松导出完成新晶体管结构所需的相应肋片层。

至于10nm工艺节点,多重图案的变化并不利于设计师。除了16/14nm中使用的所有技术,10nm节点带来了至少两个新的多重图案技术。第一个技术是三重双微影蚀刻间距分割法三重图案微影工艺。是的,两个不够的时候,为什么不用三个呢?这个工艺与20/16/14nm中使用的双微影蚀刻间距分割法工艺十分类似,除了三重图案微影工艺需要原始层在三个不同的光罩中分解这点。与双重图案微影工艺一样,当你结合三个光罩中的所有形状时,它看起来又像原始的单层了。三重图案微影工艺可用于接触、再分配互联和/或M1这样的层。图3显示了三重图案微影工艺分解示例。

图3:三个光罩三重图案微影工艺分解

由于这个工艺类似于20/16/14nm双重图案微影工艺,设计师可能会发现很多类似之处,这会使转变到三重图案微影工艺更容易。即使是使用缝合这样的固定解决方案,对于这个工艺而言理论上也是可行的。图4显示了一个布局示例,这个布局在三个光罩中不能自然分解,但可以通过利用缝合成功分解。

图4:三重图案微影工艺分解错误利用缝合进行纠正

尽管三重图案微影和双重有相似之处,但也有很多不同,因此对设计师、代工厂和电子设计自动化工具而言带来了巨大的挑战。我将在今后的文章后详细介绍这些挑战。

10nm工艺也带来了SID版SADP,这可用于部分金属互联层。正如SIM版SADP用于16/14nm工艺一样,这两个光罩和布局中原始草图形状不一样,但利用了隔离层沉积和蚀刻之间的残差来界定形状。但在SID版SADP中,隔离层并不界定行数,而是行数之间的间距。图5显示了利用SID版SADP的金属工艺示例。

图5:用于金属互联层的SID SADP工艺。

与用于16/14nm肋片层的SIM SADP工艺不同,更复杂的双向层(例如金属互联层)所采用的SID SADP工艺对于设计师而言是不容忽视的。这项工艺将需要设计师了解并适应一些新要求。此外也给晶圆代工和EDA工具带来了新的挑战。别担心——我在接下来的文章中将进一步讨论这些挑战。现在,让我们简单来看看一个金属布局示例以及它如何分解成两个光罩(图6)。

图6:金属布局分解成SID SADP的两个光罩。

从这个示例中可以看出光罩分解过程分为三个主要步骤:

原始的单层被拆分为两种“颜色”——心轴和无心轴。

新增的“虚拟心轴”多边形被分配给心轴颜色。最终的心轴和虚拟心轴形状组合形成第一个“心轴光罩”。

形成的保持层最终将倒转过来,形成最终的“遮挡光罩”。现在来看,心轴和遮挡光罩如何形成类似晶圆原始导出层的东西可能还不明显,但相信我,它可以的。我们将在另一篇文章中花更多时间来介绍这个过程。

我只想说,如果您想要着手进行任何10nm设计工作,您可能需要再学习一些有关多重图案微影的知识。很幸运,我可以为您排忧解难。至少,关于可预见的未来,我有很多想法可以与您分享!我期待帮助您完成这个学习的过程。现在,让我来简单概括一下多重图案微影领域每个工艺节点的相关知识。

●20nm:

用于多晶层的线条/切割双光罩工艺(对设计师无影响)

用于活性层、接触层、通孔层和金属层的LELE DP工艺(对设计师有影响)

●16nm:

用于肋片层的SIM SADP(对设计师无影响)

●10nm:

用于一些接触层和互联层的LELELE TP工艺(对设计师有影响)

用于一些金属互联层的SID SADP(对设计师有影响)

- 电力电子装置控制系统的DSP设计方案(04-08)

- DSP和FPGA在汽车电子中的广泛应用 (04-08)

- 基于电力电子应用平台DSP通用板的设计 (04-26)

- μC/OS-II实时操作系统在混合动力整车控制器中的应用(05-22)

- 嵌入式实时操作系统设计及应用探讨(05-25)

- 基于TMS320VC5509A的超声波电子笔设计(06-11)