集成VCO的低成本PLL支持紧凑型LO解决方案

作者:James Lee,市场开发工程师;Paul Taylor,产品经理,ADI公司

新兴的PLL + VCO (集成电压控制振荡器的锁相环)技术能够针对蜂窝/4F、微波无线电及25 MHz到13.6 GHz的军事应用快速开发低相位噪声频率合成器解决方案。

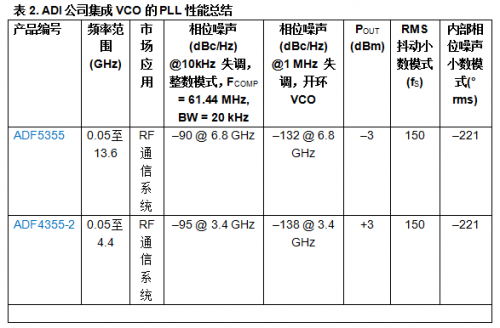

蜂窝/4G、微波无线电、测试设备和军事子系统应用的无线电设计人员依赖高质量本振(LO)来实现低BER(误码率)、低杂散输出和低相位噪声的系统级目标。 所有的RF和微波通信和传感器系统,无论是基于模拟还是数字调制,都需要干净的LO信号源;无线电的容量越高,对LO信号的要求就越高。 有许多不同架构可用,但产生稳定LO源的最常用方法之一是将低相位噪声电压控制振荡器(VCO)和稳定基准电压及锁相环(PLL)组合构成频率合成器。 不过,寻求最佳LO性能的设计人员必然会面临PLL/频率合成器、VCO、电荷泵及环路滤波器之间交互的诸多相关挑战,更不用说由于电路板布局和不良电源噪声所带来的问题。 ADI的核心专长是在频率生成元件方面,例如MMIC VCO、锁相振荡器(PLO)、低噪声预分频器、鉴频鉴相器(PFD)和一系列RF输入频率达13.6 GHz的双模式(小数/整数) PLL/频率合成器IC。 表1和2中列出了业界领先的ADI集成VCO的PLL产品。 这些集成VCO的PLL产品涵盖从25 MHz到13.6 GHz的RF和微波频率。

表1. ADI公司集成VCO的PLL性能总结

图1. ADI集成VCO的PLL产品功能框图和典型应用电路。

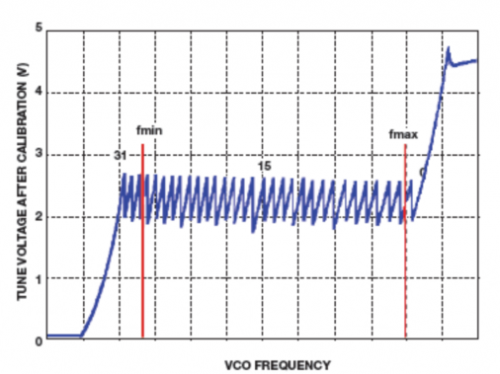

如图1的功能框图所示,这些产品采用标准5 mm × 5 mm和6 mm × 6 mm QFN塑料封装实现了高级小数-N频率合成器和超低噪声VCO;这种高水平的集成最大程度地减少了外部元件数。 设计针对超低相位噪声商业和军事应用,包括一个极低噪声鉴频鉴相器(PFD)、一个精密控制电荷泵和一个提供超精细频率步进的高级调制器设计。 架构具有超低近载波相位噪声和低杂散,可实现较宽环路带宽以及更快的跳频和低颤噪;杂散输出足够低,因此在许多应用中不再需要价格昂贵的直接数字频率合成(DDS)基准电压源。 适合RF市场应用的集成VCO的PLL 该系列的每一个产品都组合了高性能小数-N PLL/频率合成器和完全集成低噪声VCO的功能。 适合RF应用的集成VCO的PLL架构使得高性能VCO可实现五伏以下电压调谐(参见图2)。 环路滤波器中不再需要运算放大器,节省了成本和电路板空间,同时改善了性能。 集成VCO的PLL可以在一个极限温度下锁定,之后无需重新锁定或重新校准即可在整个温度范围内工作;该功能是高可靠性应用中所需要的,但是在一些竞争性解决方案中并未提供该功能。

图2. 集成VCO的PLL HMC830LP6GE的调谐电压与频率的关系。

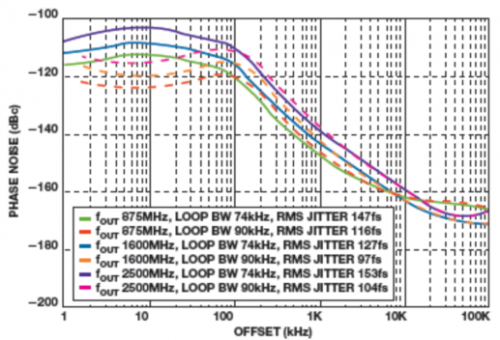

图3. 集成VCO的PLL HMC830LP6GE的SSB相位噪声与偏移频率的关系。

如图3所示,这些器件具有出色的相位噪声性能,无论就带内还是远离躁底而言通常都优于竞争性器件10 dB,而且全部无需在低杂散或低噪声模式间进行选择。 100 Hz至1 MHz范围内的集成噪声通常为–55 dBc,等效于0.1°的rms抖动,或者FOUT = 1 GHz时278 fs rms。

图4. 最差杂散,固定50 Mhz基准,输出频率= 2 GHz。

如图4所示,HMC830LP6GE与替代集成解决方案相比有明显改善。

HMC830LP6GE频带边沿处的温度范围性能稳定,确保不会出现"压差"。

例如,HMC830LP6GE在大于20 MHz的偏移频率下产生大约5 dB近载波相位噪声和7 dB相位躁底,与TI LMX2581相比,这两个值都比较低。 此外,HMC830LP6GE还提供优越的杂散性能,在整个频段的小数杂散低很多,整个频谱输出更干净。

ADF5355集成VCO的PLL涵盖同类最宽的频谱55 MHz至13.6 GHz,而ADF4355-2的频率范围是55 MHz至4.4 GHz。

ADF5355和ADF4355-2 采用新型VCO拓扑和架构,并在开发过程中利用ADI新近获得专利的先进SiGe-BiCMOS工艺,因而具有出色的VCO相位噪声性能。

两款器件都集成了超低相位噪声VCO,对于ADF4344-2而言在3.4 GHz下产生–138 dBc/Hz(1 MHz失调)相位噪声,而ADF5355在6.8 GHz下产生–132 dBc/Hz(1 MHz失调)相位噪声。 在超宽带宽RF和微波通信应用中,该超低相位噪声具有改善整体系统误码率并提升数据吞吐速率的优势,可提供更佳的抗噪能力和更宽的动态范围。 ADI最新的高性价比、超宽带宽PLL频率合成器IC还具有高达125 MHz相位比较器频率和38位分辨率,可降低抖动并允许极为精细的步进大小,而相比分立式GaAs部署方案,采用高级BiCMOS工艺的集成式PLL和VCO可大幅降低封装尺寸和功耗。 另外,由于单个PLL频率合成器的工作频率可在55 MHz至13.6 GHz范围内配置,因此设计人员可更为快速地对他们的系统设计

ADI PLL LO解决方案 集成VCO HMC764LP6CE 相关文章:

- ADI公司为下一代蜂窝与宽带无线应用提供直接变频接收机解决方案(08-17)

- ADI ADRF6655 100-2500 MHz有源混频方案(08-30)

- ADI ADL5354高性能RF混频方案(09-07)

- Anadigics AWT6241 TD-SCDMA手机线性功率放大方案(07-26)

- ADI ADF4150HV 4.4 GHz频率合成方案(09-07)

- 射频收发器为航空航天和防务应用提供突破性的SWaP解决方案(10-23)