MEMS时钟振荡器在射频系统中的应用

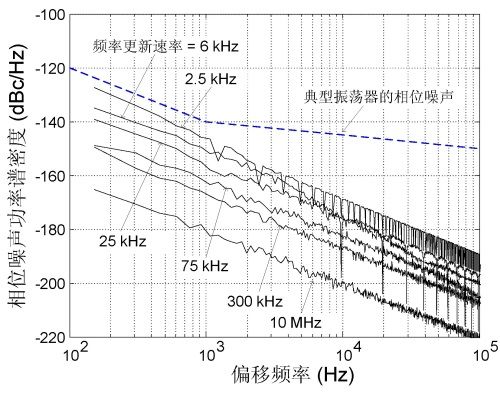

率、频率更新速率和更新延迟,以尽量减少频率更新引起的量化相位噪声。通过提高频率更新速率和频率分 辨率,量化噪声可以降至振荡器本征相位噪声水平以下。图2是不同频率分辨率调整下的10MHz DCXO相位噪声, 频率更新速率每秒25,000次。图中数据显示,如果DCXO频率调整的分辨率高于10ppb,频率更新引入的量化噪声可降至低于振荡器本征相位噪声的水 平,使得频率调整不会影响性能。频率更新速率也是非常重要的设计参数,因为更新速率太低会导致DCXO在相对长的时间累积较大的频率相位误差,从而导致较 大的频率调整数值和增加量化相位噪声。但是,对于一个能以1ppb分辨率调整的DCXO,即使是低至每秒2,500次的更新速率,也足以确保量化噪声不影响振荡器的性能(见图3)。

图3:频率更新速率对近载波相位噪声的影响,DCXO频率分辨率1 ppb

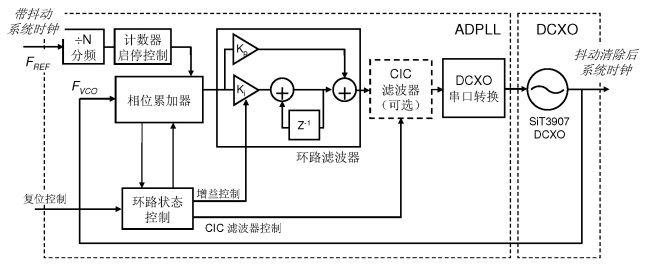

DCXO抖动清除电路实现

应用于抖动清除锁相环路的DCXO应具有足够高的频率更新速率,极高的频率分 辨率,低相位噪声性能和适合系统要求的频率牵引范围。图4是一个基于DCXO和FPGA的全数字锁相环路125MHz时钟的抖动清除电路。该设计选择的 SiT3907 DCXO可以提供最高每秒25,000次的频率更新速率,1ppb的高频率分辨率,小于1 ps RMS(12kHz~20MHz)的积分相位抖动特性和最高达±1600ppm的线性牵引范围。全数字锁相环电路包括输入时钟分频器,相位累加器、环路滤 波器,环路状态控制电路,可选的CIC滤波器,以及驱动DCXO芯片的串行通信接口。

图4:基于DCXO和ADPLL的抖动清除电路框图

相位累加器是一个启停计数器,由反馈的DCXO时钟驱动。计数器周期的启动和结束由输入时钟分频脉冲触发。输入时钟预分频值N决定了相位累加器的采样率。环路滤波器需要保持低带宽,一般不大于相位累加器采样率的十分之一。环路状态控制电路在检测到锁定状态之后可降低环路增益,进一步提高噪声抑制能力。

图4的数字锁相环电路还包括两个附加功能,可以降低相位噪声和抖动。第一个功能是环路状态控制电路的更新或复位信号,可最小化相位误差的积累。第二个功能是可选的CIC滤波器,可降低开环增益。没有打开CIC滤波器的开环增益H(s)为:

其中,N是系统时钟与相位比较器采样频率之间的比率。当环路滤波器增益在锁定过程中的两个值之间交替时,CIC滤波器可减轻增益变化对输出的影响。另外,调节增益Kp和Ki之间的比例可以增加稳定性、提高性能。

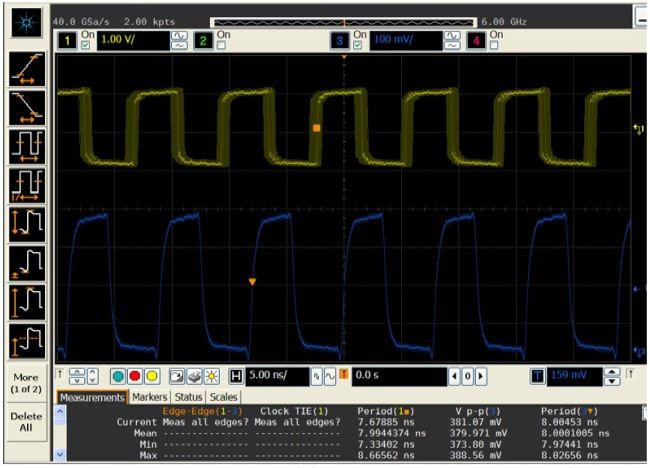

实验测量该设计的相位噪声、相位抖动和抖动衰减的有效性。测量数据显示对正弦信号调制抖动的衰减可高达60dB,并导致综合相位抖动显著降低。图5显示抖动 清除电路对时钟信号的影响;从一个能观察到明显抖动的125MHz系统时钟开始,将宽带相位抖动从157 ps RMS降至3.5 ps RMS,产生了一个适合通信和网络应用的高性能、低抖动的输出时钟。

图5:比较带抖动的125 MHz系统时钟输入(黄色,顶部)与抖动清除后的输出时钟

- ST:MEMS加速度传感器五大功能简化用户设计(05-22)

- 一种90°分布式MEMS 移相器的设计(02-25)

- 低压驱动RF MEMS开关设计(09-29)

- 半导体所在微机电射频谐振器件研究(11-27)

- 基于MEMS技术的移动电话射频设计(11-21)

- 基于MEMS技术移动电话射频设计 (01-10)