通过实时改变使用率研究FPGA功耗行为

时间:01-12

来源:互联网

点击:

完美匹配XPE

我们在很多具有可变因素的不同设计方案中对我们的设计进行了测试,以确保其精确性和可靠性。同时,还在测量值的示意图中绘出XPE 的估计结果,从而将功耗估计值与实际测量值进行比较。

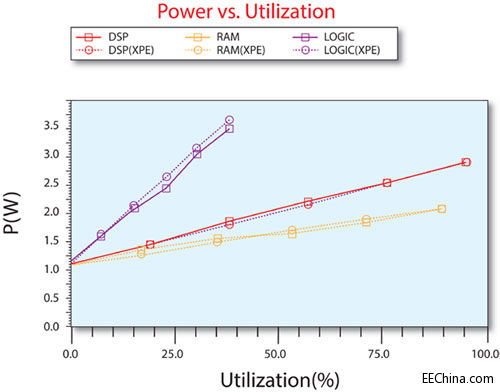

通过最初将资源使用率从零至设计最大值扫描的设计实现可观察Kintex-7 器件的功耗行为。图3 给出了扫描一种资源类型的使用率过程中功耗的变化情况。直线和虚线分别代表实际功耗测量值和XPE 的估计值。我们可以看到即使在使用率和功耗处于高值时两条曲线依然靠得非常紧密。

图3 – 在这个功耗与使用率关系图中,直线代表实际的功耗测量值,虚线代表XPE的估计值。

这些结果表明赛灵思功耗估计器计算值与实际测量值一致,可以准确地预测功耗。此外,我们还可以断定我们推荐的方法能够起到预期效果,并且可以作为XPE 的替代方案。更好的选择是将两种方法结合使用。同时采用XPE 和我们的方法来测试设计可对结果进行双重检查,确保您在XPE中修改数字时不会犯任何错误。例如,如果您没有在XPE 中正确输入时钟的平均扇出数字,或者误解了一个概念并错误填写对话框,那么得到的示意图就无法重合,即表明有错误存在,这样您就可以校正输入值,防止出现误导性的估算结果。

FPGA 开发板的额定规范,例如最大功耗或允许的内核温度范围,总是包含在开发板的数据手册中。不过,具有较高资源使用率和时钟频率的设计会超出这些额定值。因此,必须确认功率调节器能为器件提供足够的电流,而且散热系统足以将温度保持在FPGA 设计的临界值以内。我们的方法可通过增加资源使用和时钟频率来测试开发板的可靠性能否满足高性能要求。这种测试有助于确定开发板上实现的设计所具备的最高信号处理速率。此外,我们还可以了解是否需要升级开发板的功能和系统的冷却机制。

测试结果表明了我们的方法能够可靠地控制资源使用和评估功耗,因此工程师在设计前期阶段就多了一种电源管理选项。在采取进一步功能改进后,例如增加JTAG 接口、完全独立于器件的VHDL 代码以及通用的电流感应系统,这项设计将会成为FPGA 项目的关键工具。

电源管理 FPGA 赛灵思 电子 仿真 VHDL DSP 电流 电压 PWM 传感器 ADC 德州仪器 总线 集成电路 电路 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 高效地驱动LED(04-23)

- 电源SOC:或许好用的“疯狂”创意(07-24)

- 实现智能太阳能管理的微型逆变器应运而生(05-06)