深入研究DDR电源

时间:09-25

来源:互联网

点击:

DDR存储器的发展历程

由于几乎在所有要求快速处理大量数据(可能是计算机、服务器或游戏系统)的应用中都要求具有RAM(随机存储器),因而DDR存储器也变得日益重要,其应用也更加广泛。自问世以来,RAM就已经变得至关重要,主要因为它是一种能够保存易失性信息的存储器,并且可以以一种更快速、更直接的方式存取信息。当在数据计算的世界里谈及系统速度和效率时,这一点显得尤为重要。

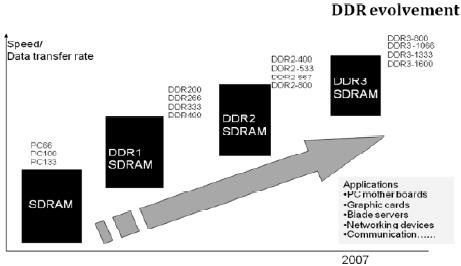

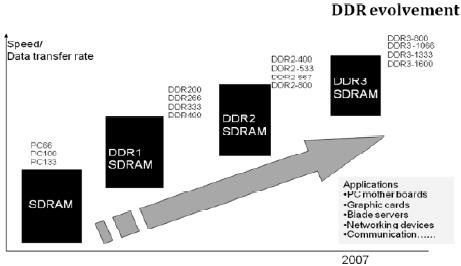

DDR SDRAM(双数据速率同步动态随机存储器),其可以通过在时钟周期的上升和下降沿上分别提取数据而使数据率加倍,现在看来它正发展成为最先进的RAM芯片集。这与以往的SDR SDRAM大不相同,因为后者仅能在时钟周期的一个边沿上提取数据。从图1可以看出,DRAM正在向着速度和数据传输率都不断提高的方向发展。

近些年来,CPU时钟频率经历了指数增长,从而为RAM存储器的时钟频率增长提供了动力。

在1997年,SD RAM在市场亮相,它可以取代DRAM和SRAM两种存储器并提供更快的时钟速率。这主要源于SDRAM具有更简捷的通信协议;所有指令、地址和数据都由一个单独的时钟信号控制并且工作在突发模式,可以在66MHz的时钟频率下突发一系列数据字。在1998年,SD RAM频率已经增长到100MHz 的突发脉冲速率。

在1999年,英特尔和AMD间的企业竞争升级,在CPU时钟速度方面也不例外。处理器行业的蓬勃发展进一步加大了CPU时钟速度与其它系统组件间的差距。在此期间,尽管存储器总线速度已经全力达到了133MHz,但却仍然远远落后于CPU所能完成的速度,因此,总的来说,这也成为提高整体应用速度的瓶颈。

为了解决这个问题,DDR RAM(双数据速率传输)的设计应运而生。DDR RAM允许分别在时钟的上升沿和下降沿上提取数据,从而加倍了时钟的有效传输速率。例如,一个100MHz的DDR时钟能够达到相当于200MHz时钟频率的峰值传输速率。这就是DDR1技术,其速度可高达400MHz。

下一代DDR,即我们所说的DDR2。DDR2技术将数据传输速率从400MHz提升到800MHz,数据总线为64位(8字节)。它不能与前一代DDR1存储器实现物理兼容,这种二代存储器现在已经是由RAM存储器厂商普遍生产的产品。

DDR3技术在2006年年底就已经投放使用,并补充了DDR2的不足(达到800Mbps的带宽),将速度提升到1.6 Gbps。

除了众所周知的PC应用,DDR存储器还广泛用于高速并对存储器提出高要求的应用中,如:图形卡、刀片式服务器、网络装置和通信装置等。

在市场细分中,对速度和更低工作电压都有苛刻要求的一个领域是便携式消费领域。举例来说,我们已注意到越来越多的电子元器件都能提供图形和动态图片(视频)能力,从而满足了我们对于更多DRAM存储器的高需求。像PSP(便携式游戏机)游戏系统、智能电话、数码相机或GPS(全球定位服务)装置等产品都会采用某种DRAM,而且都将要求尽可能低的功耗,以使电池的运行时间更长。

由于DDR存储器数据速率随着技术的发展而不断提高,那么工作电压也在随之变化。目前用于驱动DDR3 SDRAM的DDR3标准电压为1.5V(图2)。因此我们注意到随着标准的升级,新的技术正在推动电压变得越来越低。

表1显示了RAM存储器芯片集在时钟和转换速率方面的简要对比,这些芯片集主要用于当今的PC电脑,其中包括SDR、DDR1、DDR2和最新推出的DDR3模块。

DDR标准

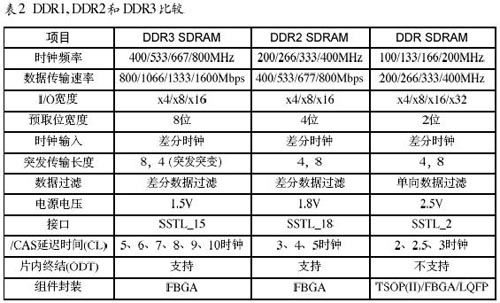

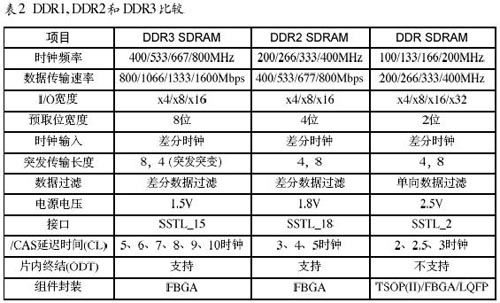

为了对DDR1、DDR2和DDR3 SDRAM间的差异进行比较,参考表2。

先将运行时钟频率或速度放在一边,单从工作电压这一点来看,我们能够看出DDR1、DDR2和DDR3存储器分别由2.8,1.8和1.5V的电压来供电。因此,与使用3.3V电压的SDRAM标准芯片集相比,这些存储器在产生更少热量同时还实现了更高的效率。DDR3通过采用 1.5V的工作电压,消耗的功率比DDR2(采用1.8V)更少——较DDR2降低了16.3%。DDR2和DDR3存储器都具有节能的特性,如采用了更小的页面尺寸和有效的掉电模式。而且,DDR存储器接口采用新的串联端接逻辑(SSTL)拓朴,旨在提高抗噪性、增加电源抑制并通过更低的电源电压来降低功耗(针对可比的速度)。另外值得注意的一点是,DDR3和DDR2 SDRAM支持片内端接,而DDR1 SDRAM不支持。

这些特性和功耗优势使它们特别适合用于笔记本电脑, 服务器和低功率移动应用。

这里,我们总结了不同的DDR SDRAM的电源管理系统需求。SDRAM和目前正在应用的DDR SDRAM相比的主要差别是:

对于电源电压,DDR SDRAM系统要求三个电源,分别为表3所列的VDDQ、VTT和VREF。

我们将深入研究需要这些电压的原因。

尽管DDR存储器在无需加倍时钟频率的情况下使数据传输率加倍,避免了PC板设计和布局的复杂性,但它要求有更严格的dc稳压、更高的电流和对端电源电压(VTT)和存储总线电压(VDD)紧密的跟踪。新型串联端接逻辑(SSTL)拓朴的引入是用于提高抗噪性、增加电源抑制并使用更低的电源电压以降低功耗。

JEDEC标准JESD8-9A(用于SSTL_2)和JESD8-15(用于SSTL_18)定义了VDDQ、VTT和VERF以及驱动器/接收器规格以分别满足在VDDQ= 2.5 V (用于 DDR1) 和VDDQ = 1.8 V (用于 DDR2)时的噪声容限。下面,我们看看这种接口以更好的理解VREF和VTT的需要。

由于几乎在所有要求快速处理大量数据(可能是计算机、服务器或游戏系统)的应用中都要求具有RAM(随机存储器),因而DDR存储器也变得日益重要,其应用也更加广泛。自问世以来,RAM就已经变得至关重要,主要因为它是一种能够保存易失性信息的存储器,并且可以以一种更快速、更直接的方式存取信息。当在数据计算的世界里谈及系统速度和效率时,这一点显得尤为重要。

DDR SDRAM(双数据速率同步动态随机存储器),其可以通过在时钟周期的上升和下降沿上分别提取数据而使数据率加倍,现在看来它正发展成为最先进的RAM芯片集。这与以往的SDR SDRAM大不相同,因为后者仅能在时钟周期的一个边沿上提取数据。从图1可以看出,DRAM正在向着速度和数据传输率都不断提高的方向发展。

近些年来,CPU时钟频率经历了指数增长,从而为RAM存储器的时钟频率增长提供了动力。

在1997年,SD RAM在市场亮相,它可以取代DRAM和SRAM两种存储器并提供更快的时钟速率。这主要源于SDRAM具有更简捷的通信协议;所有指令、地址和数据都由一个单独的时钟信号控制并且工作在突发模式,可以在66MHz的时钟频率下突发一系列数据字。在1998年,SD RAM频率已经增长到100MHz 的突发脉冲速率。

在1999年,英特尔和AMD间的企业竞争升级,在CPU时钟速度方面也不例外。处理器行业的蓬勃发展进一步加大了CPU时钟速度与其它系统组件间的差距。在此期间,尽管存储器总线速度已经全力达到了133MHz,但却仍然远远落后于CPU所能完成的速度,因此,总的来说,这也成为提高整体应用速度的瓶颈。

为了解决这个问题,DDR RAM(双数据速率传输)的设计应运而生。DDR RAM允许分别在时钟的上升沿和下降沿上提取数据,从而加倍了时钟的有效传输速率。例如,一个100MHz的DDR时钟能够达到相当于200MHz时钟频率的峰值传输速率。这就是DDR1技术,其速度可高达400MHz。

下一代DDR,即我们所说的DDR2。DDR2技术将数据传输速率从400MHz提升到800MHz,数据总线为64位(8字节)。它不能与前一代DDR1存储器实现物理兼容,这种二代存储器现在已经是由RAM存储器厂商普遍生产的产品。

DDR3技术在2006年年底就已经投放使用,并补充了DDR2的不足(达到800Mbps的带宽),将速度提升到1.6 Gbps。

除了众所周知的PC应用,DDR存储器还广泛用于高速并对存储器提出高要求的应用中,如:图形卡、刀片式服务器、网络装置和通信装置等。

在市场细分中,对速度和更低工作电压都有苛刻要求的一个领域是便携式消费领域。举例来说,我们已注意到越来越多的电子元器件都能提供图形和动态图片(视频)能力,从而满足了我们对于更多DRAM存储器的高需求。像PSP(便携式游戏机)游戏系统、智能电话、数码相机或GPS(全球定位服务)装置等产品都会采用某种DRAM,而且都将要求尽可能低的功耗,以使电池的运行时间更长。

由于DDR存储器数据速率随着技术的发展而不断提高,那么工作电压也在随之变化。目前用于驱动DDR3 SDRAM的DDR3标准电压为1.5V(图2)。因此我们注意到随着标准的升级,新的技术正在推动电压变得越来越低。

表1显示了RAM存储器芯片集在时钟和转换速率方面的简要对比,这些芯片集主要用于当今的PC电脑,其中包括SDR、DDR1、DDR2和最新推出的DDR3模块。

DDR标准

为了对DDR1、DDR2和DDR3 SDRAM间的差异进行比较,参考表2。

先将运行时钟频率或速度放在一边,单从工作电压这一点来看,我们能够看出DDR1、DDR2和DDR3存储器分别由2.8,1.8和1.5V的电压来供电。因此,与使用3.3V电压的SDRAM标准芯片集相比,这些存储器在产生更少热量同时还实现了更高的效率。DDR3通过采用 1.5V的工作电压,消耗的功率比DDR2(采用1.8V)更少——较DDR2降低了16.3%。DDR2和DDR3存储器都具有节能的特性,如采用了更小的页面尺寸和有效的掉电模式。而且,DDR存储器接口采用新的串联端接逻辑(SSTL)拓朴,旨在提高抗噪性、增加电源抑制并通过更低的电源电压来降低功耗(针对可比的速度)。另外值得注意的一点是,DDR3和DDR2 SDRAM支持片内端接,而DDR1 SDRAM不支持。

这些特性和功耗优势使它们特别适合用于笔记本电脑, 服务器和低功率移动应用。

这里,我们总结了不同的DDR SDRAM的电源管理系统需求。SDRAM和目前正在应用的DDR SDRAM相比的主要差别是:

- 电源电压;

- 接口;

- 数据传输频率。

对于电源电压,DDR SDRAM系统要求三个电源,分别为表3所列的VDDQ、VTT和VREF。

我们将深入研究需要这些电压的原因。

尽管DDR存储器在无需加倍时钟频率的情况下使数据传输率加倍,避免了PC板设计和布局的复杂性,但它要求有更严格的dc稳压、更高的电流和对端电源电压(VTT)和存储总线电压(VDD)紧密的跟踪。新型串联端接逻辑(SSTL)拓朴的引入是用于提高抗噪性、增加电源抑制并使用更低的电源电压以降低功耗。

JEDEC标准JESD8-9A(用于SSTL_2)和JESD8-15(用于SSTL_18)定义了VDDQ、VTT和VERF以及驱动器/接收器规格以分别满足在VDDQ= 2.5 V (用于 DDR1) 和VDDQ = 1.8 V (用于 DDR2)时的噪声容限。下面,我们看看这种接口以更好的理解VREF和VTT的需要。

总线 电压 电子 GPS 电源管理 电流 电阻 开关电源 比较器 飞思卡尔 MCU 电感 电容 相关文章:

- 低功耗嵌入式实现的方方面面(04-30)

- 主动“ORing”方案降低了功率损耗和设备尺寸(06-24)

- S3C2440A嵌入式手持终端电源管理系统设计(01-11)

- 几种实用的低电压冗余电源方案设计(01-26)

- 基于CAN通信的电源监控系统的设计(04-06)

- 基于CAN总线的低压智能断路器的设计(04-06)