基于FPGA的三相SPWM的设计及其优化

时间:08-29

来源:互联网

点击:

3 结语

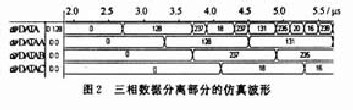

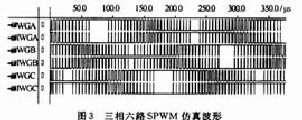

由以上分析及仿真可知,采用一个1/4周期的正弦表实现三相正弦数据的查询是可行的。这将极大的节省所用FPGA的门数,提高其利用率,极大地降低编程的劳动量,且输出的三相正弦波与不利用分时复用和正弦波对称性时相比,精度不受任何影响,每个正弦周期还是由256个点组成,只是正弦波的频率有所降低,这是由于系统的速度和占用面积之间本来就是一种矛盾。图3是本次设计产生的三相六路SPWM,系统仿真的时钟周期为200ns,由于FPGA的系统时钟频率可以达到很高,所以不会对输出的SPWM频率产生影响。

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 高效地驱动LED(04-23)

- 适合高效能模拟应用的线性电压稳压器(07-19)

- 低功耗嵌入式实现的方方面面(04-30)

- 电源设计小贴士5:降压-升压电源设计中降压控制器的使用(03-18)