一种DC-DC芯片内建可测性设计

时间:07-29

来源:互联网

点击:

在便携式电子和消费电子产品中,对基于电池供电的电源管理的指标要求越来越高,其中高效率和低成本是最主要的两项指标。开关型集成DC-DC转换器由于具有很高的效率使其在很多场合成为首选的电源管理方案。然而,DC-DC的设计变得日益复杂,为了满足不同的应用需要,要求可以在PWM和PFM之间选择工作方式,可以在工作状态和休眠状态之间自动切换;为了提高可靠性,要求具有过电压、过电流和过温等各种保护功能;为了实现低噪声,有些需将LDO线性稳压器集成在内部,有些需增加抗振荡(anti-ring)电路;为了实现更高的精度和输出电压的编程,还会将小规模的EPROM集成在内部。另外,DC-DC的电路规模也越来越大,经常需要设计多个内部电压基准、电流基准和低失调比较器等,而内部的数字逻辑电路和大功率器件又会给其他电路造成各种影响,所有这些都对DC-DC的设计带来严峻的挑战。

为了简化DC-DC的设计过程,满足日益变化的新需求,进行合理的可测性设计就显得越来越重要。一方面,由于电路复杂度的提高,一次投片成功的可能性越来越小,往往存在一个故障分析和调试过程,而这个过程所占的时间越来越长,已成为限制设计进程的一个重要因素。如果可以将电路内部的关键指标进行方便的测量,就可以提供更多的信息帮助分析判断电路故障,调试就会比较容易;另一方面,由于工艺存在的离散性,电路量产时,需要根据电路内部的关键参数确定具体的修正(trimming)方案,以保证足够高的成品率,这也要求对内部参数进行方便的测量。

对于典型的单节锂/锂离子电池供电的BUCK型DC-DC(见图1)来说,通常只有电源(VCC)、地(GND)、开关输出(SW)、反馈(VFB)、使能控制(EN)和模式控制(MODE)六个引脚。为了减小体积通常采用SOT-23-6封装,没有多余的引脚可以专门用来测量内部参数,这给可测性设计带来了困难。针对这种情况,本文中提出了一种引脚复用技术,可以实现芯片内部参数的测量。

基本原理

引脚复用技术多用在数字电路中,一般是指电 路在不同状态或不同时刻时,使芯片引脚代表不同意义的信息,比如分别代表地址信息和数据信息,来实现引脚复用,达到减少引脚或扩展功能的目的。对于典型的DC-DC来说,电源、地、输出、反馈四个引脚的信号均为模拟信号,正常工作中它们出现任何电平都是有意义的,没有多余状态可以利用,而使能控制(EN)和模式控制(MODE)两个引脚为高低电平控制信号,可以将这些引脚电平分为多个电平档段从而使每个引脚电平可以表达多于两个信息的信息量。本文中对使能控制引脚采用这种方法控制芯片进入测试状态,实现对芯片内部各个参数的测量。

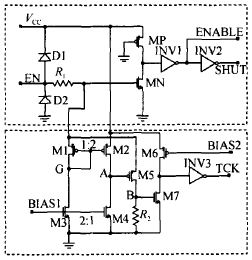

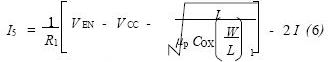

图1中,MODE控制芯片工作在PWM模式还是PFM模式,EN引脚作为电路的使能控制,当VEN>115V时,电路处于工作状态,当VEN1是ESD保护部分,防止器件在储运和焊接过程中的高压静电损坏芯片。MP为一沟道长度远大于沟道宽度(LmW)的PMOS,作为MN的负载,起到一个大电阻的作用。INV1和INV2为两个反相器,缓冲驱动正反相的使能信号ENABLE和SHUT去控制其他电路。可以看出,电路工作时,VEN必须小于VCC+VD1,否则D1会导通,大电流会通过D1由EN流向VCC,时间长了会导致芯片损坏。在实际应用中,要求VEN的最高电平不能超过VCC+0.3V,通常EN的高电平直接采用VCC电平。本文中提出的方法,就是利用VEN在VCC到VCC+VD1之间的电压范围实现额外的功能,当芯片内部电路检测到VEN>VCC+0.3V时控制芯片进入测试状态,而正常工作时由于VENCC+0.3V而不受任何影响。

图1BUCK型DC-DC典型应用电路

图2使能控制和测试状态检测电路

电路实现

为了完成芯片内部参数的测试,需要在芯片内部添加一定的测试电路,它需要完成的功能有:进入和退出测试状态的控制;测试序列的生成;测试结果的输出以及合适的外围控制电路等,下面分别介绍各种功能实现。

测试状态的检测

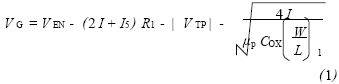

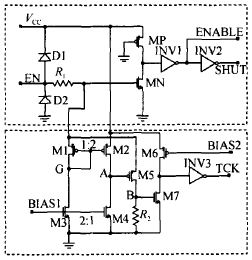

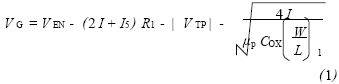

电路测试时,首先要退出正常工作状态而进入测试状态,图2下半部分的电路为进入测试状态的检测电路,M3和M4为2∶1的电流源,当它们工作在饱和区时,电流分别为I3=2I,I4=I(式中In指Mn的电流,以下类同),I由偏置信号BIAS1决定,M1和M2共栅,其栅极电压VG为:

如果M2工作在饱和区,则其电流为:

(1)式代入(2)式,考虑到(W/L)2=2(W/L)1可得:

当VEN≤VCC时,

I 2,sat>4I=4I4 (4)

所以M2不会工作在饱和区,而是进入深线性区,A点被抬升为高电平,即

VA≈VCC (5)

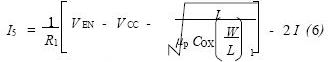

M5截止,I5=0,M7截止,输出TCK为低电平。当VEN>VCC且逐渐升高时,VG电平逐渐升高,M2逐渐由线性区进入饱和区,M1~M5构成了一个负反馈电路,在平衡状态时,M2和M4均处于饱和区 且电流相等,由此可以得到M5中的电流为:

当

,即当VEN满足(7)式时,TCK输出高电平,控制进入测试状态。

设计中VEN的选取既要保证VENCC+VD1,防止ESD二极管D1(见图2)导通,又要保证一定的噪声容限,防止EN接VCC正常工作时噪声引起两者的差别使电路进入测试状态,一般可选取(VEN-VCC)等于0.3~0.4V,由(7)式可知,可以通过调整R2达到设计要求。

为了简化DC-DC的设计过程,满足日益变化的新需求,进行合理的可测性设计就显得越来越重要。一方面,由于电路复杂度的提高,一次投片成功的可能性越来越小,往往存在一个故障分析和调试过程,而这个过程所占的时间越来越长,已成为限制设计进程的一个重要因素。如果可以将电路内部的关键指标进行方便的测量,就可以提供更多的信息帮助分析判断电路故障,调试就会比较容易;另一方面,由于工艺存在的离散性,电路量产时,需要根据电路内部的关键参数确定具体的修正(trimming)方案,以保证足够高的成品率,这也要求对内部参数进行方便的测量。

对于典型的单节锂/锂离子电池供电的BUCK型DC-DC(见图1)来说,通常只有电源(VCC)、地(GND)、开关输出(SW)、反馈(VFB)、使能控制(EN)和模式控制(MODE)六个引脚。为了减小体积通常采用SOT-23-6封装,没有多余的引脚可以专门用来测量内部参数,这给可测性设计带来了困难。针对这种情况,本文中提出了一种引脚复用技术,可以实现芯片内部参数的测量。

基本原理

引脚复用技术多用在数字电路中,一般是指电 路在不同状态或不同时刻时,使芯片引脚代表不同意义的信息,比如分别代表地址信息和数据信息,来实现引脚复用,达到减少引脚或扩展功能的目的。对于典型的DC-DC来说,电源、地、输出、反馈四个引脚的信号均为模拟信号,正常工作中它们出现任何电平都是有意义的,没有多余状态可以利用,而使能控制(EN)和模式控制(MODE)两个引脚为高低电平控制信号,可以将这些引脚电平分为多个电平档段从而使每个引脚电平可以表达多于两个信息的信息量。本文中对使能控制引脚采用这种方法控制芯片进入测试状态,实现对芯片内部各个参数的测量。

图1中,MODE控制芯片工作在PWM模式还是PFM模式,EN引脚作为电路的使能控制,当VEN>115V时,电路处于工作状态,当VEN1是ESD保护部分,防止器件在储运和焊接过程中的高压静电损坏芯片。MP为一沟道长度远大于沟道宽度(LmW)的PMOS,作为MN的负载,起到一个大电阻的作用。INV1和INV2为两个反相器,缓冲驱动正反相的使能信号ENABLE和SHUT去控制其他电路。可以看出,电路工作时,VEN必须小于VCC+VD1,否则D1会导通,大电流会通过D1由EN流向VCC,时间长了会导致芯片损坏。在实际应用中,要求VEN的最高电平不能超过VCC+0.3V,通常EN的高电平直接采用VCC电平。本文中提出的方法,就是利用VEN在VCC到VCC+VD1之间的电压范围实现额外的功能,当芯片内部电路检测到VEN>VCC+0.3V时控制芯片进入测试状态,而正常工作时由于VENCC+0.3V而不受任何影响。

图1BUCK型DC-DC典型应用电路

图2使能控制和测试状态检测电路

电路实现

为了完成芯片内部参数的测试,需要在芯片内部添加一定的测试电路,它需要完成的功能有:进入和退出测试状态的控制;测试序列的生成;测试结果的输出以及合适的外围控制电路等,下面分别介绍各种功能实现。

测试状态的检测

电路测试时,首先要退出正常工作状态而进入测试状态,图2下半部分的电路为进入测试状态的检测电路,M3和M4为2∶1的电流源,当它们工作在饱和区时,电流分别为I3=2I,I4=I(式中In指Mn的电流,以下类同),I由偏置信号BIAS1决定,M1和M2共栅,其栅极电压VG为:

如果M2工作在饱和区,则其电流为:

(1)式代入(2)式,考虑到(W/L)2=2(W/L)1可得:

当VEN≤VCC时,

I 2,sat>4I=4I4 (4)

所以M2不会工作在饱和区,而是进入深线性区,A点被抬升为高电平,即

VA≈VCC (5)

M5截止,I5=0,M7截止,输出TCK为低电平。当VEN>VCC且逐渐升高时,VG电平逐渐升高,M2逐渐由线性区进入饱和区,M1~M5构成了一个负反馈电路,在平衡状态时,M2和M4均处于饱和区 且电流相等,由此可以得到M5中的电流为:

当

,即当VEN满足(7)式时,TCK输出高电平,控制进入测试状态。

设计中VEN的选取既要保证VENCC+VD1,防止ESD二极管D1(见图2)导通,又要保证一定的噪声容限,防止EN接VCC正常工作时噪声引起两者的差别使电路进入测试状态,一般可选取(VEN-VCC)等于0.3~0.4V,由(7)式可知,可以通过调整R2达到设计要求。

电子 电源管理 PWM 电压 电流 LDO 电路 比较器 电阻 二极管 放大器 运算放大器 振荡器 CMOS 相关文章:

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 高效地驱动LED(04-23)

- 适合高效能模拟应用的线性电压稳压器(07-19)

- 低功耗嵌入式实现的方方面面(04-30)

- 电源设计小贴士5:降压-升压电源设计中降压控制器的使用(03-18)