一种极具成本效益的磁卡读卡器设计

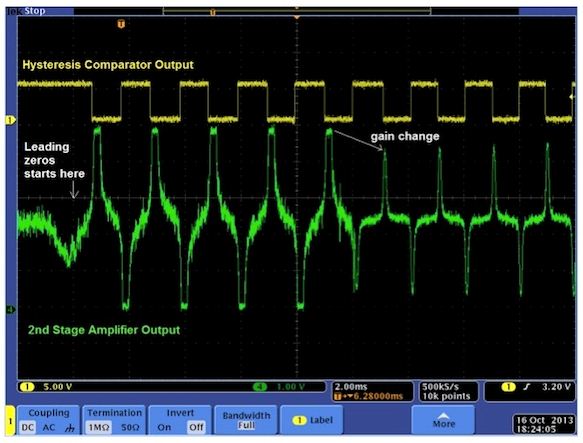

到最佳。第 二级放大器的输出送到峰值检测器/磁滞比较器电路进行峰值检测。来自检测器的脉冲输出被馈送至定时器进行时间差测量,然后由CPU解码出1和0。 至 此仍然存在增益更新之前是否有数据丢失的问题。为了避免这个问题,磁卡的两头会用前导零进行编码以实现同步(这样可以支持双向划卡)。这样做的目的是使解 码器同步于划卡速度。举例来说,在磁道1中,共有约62个前导零。磁道1具有210个比特的数据密度。因此我们可以估算出划卡速度为5 IPS时前导零将持续约60ms时间,划卡速度为50 IPS时前导零将持续6ms。对另外两个磁道来说或多或少是相同的,如图7所示。在人为划卡时一开始就是50 IPS的划卡速度是不可能,因此系统具有比6ms长得多的时间来测量峰值并调整增益。图8显示了增益控制过程。 需要注意的是,CPU在划卡期间可能会持续精细调整增益以适应变化的幅度。正常情况下,顺着划卡的方向,划卡速度会增加,从而增加信号幅度。注意,在使用以恒定速度划卡的自动划卡机时这个观点是不正确的。

图6:磁卡读卡器框图。

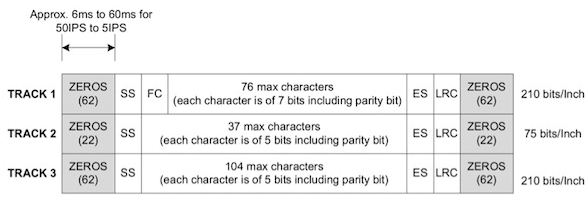

图7:磁卡中三个磁道的内容。

图8:增益改变过程。

实现磁卡读卡器

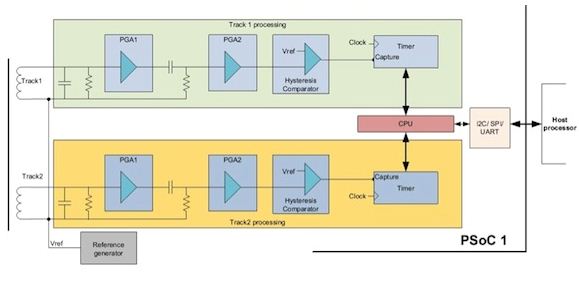

图9显示了基于赛普拉斯PSoC 1的双磁道磁卡读卡器实现方案。PSoC 1处理器具有与8位处理器内核集成在一起的可配置模拟和数字块,在单颗芯片上集成了所有的功能。需要注意的是,图中所示的无源器件是在处理器的外部。

图9:PSoC 1磁卡读卡器

由于传感器信号可能是负的,因此必须用直流进行偏置。在PSoC 1中,模拟信号可以以不同于电源地的地为参考。这个地被称为模拟地(AGND),输入信号被钳位到这个模拟地。信号随后用可编程增益放大器(PGA)进行两级放大。PGA是用连续时间模拟模块实现的。它具有一个电阻阵列,当配置为放大器时用于改变增益。增益可以被配置为1至48之间18个选项之一。CY8C28243 PSoC 1集成了一个最大采样速率为150ksps的10位SAR ADC。

CPU读取ADC,然后控制放大器增益。放大后的信号送到磁滞比较器产生边沿接近信号峰值的数字信号。CPU随后必须调整放大器增益,使其阈值接近峰值但不超过 峰值。这有助于避免磁卡发生抖动时出现定时误差。磁滞比较器输出则送到定时器进行脉冲宽度测量。CPU读取定时器输出,并解码为逻辑1或0的数据。当划卡 结束时,CPU打包数据比特,检查是否有错误,然后通过I2C、SPI或UART接口将数据送给主机。

- 无线传感器网络简介(08-19)

- 功率计和功率传感器工作原理(12-24)

- 基于EM250技术的ZigBee无线传感器网络解决方案(12-22)

- 微波传感器的应用领域(01-06)

- 高能效UV紫外线指数传感器抢占可穿戴市场商机(07-22)

- TI高精度毫米波传感器制胜绝技 - CMOS技术详解(06-13)