基于NiosⅡ的U盘安全控制器设计

时间:11-10

来源:互联网

点击:

目前,U盘等USB移动存储载体由于其容量大、价格低、携带方便、可靠性高等优点,得到了越来越广泛的应用,在生活、工作中随处可见。然而,USB移动存储载体的便利性及其自身安全脆弱性的矛盾十分突出。

本文针对U盘的安全隐患,分析目前较为常见的解决方法,利用SoPC技术,设计实现了一款基于NiosⅡ处理器的U盘安全控制器。该控制器位于PC机和U盘之间,通过对U盘进行扇区级的加解密操作,将普通U盘升级为安全U盘,保证U盘中数据的安全性。控制器遵循USB MassStorage类协议,无需专用驱动,即插即用,具有灵活方便、安全性高等优点[1]。

1 安全控制器的整体设计

1.1 安全U盘解决方案分析

U盘最为突出的安全问题是其内部所存储的数据都以明文形式存储,任何人得到该存储载体,即可对其中的数据进行任意的操作。因此,普通U盘一旦丢失,其存储的数据则毫无安全性可言。针对这一问题,目前已经有多种解决方法,其中较为常见、安全性较高的是采用专用安全U盘的方法。

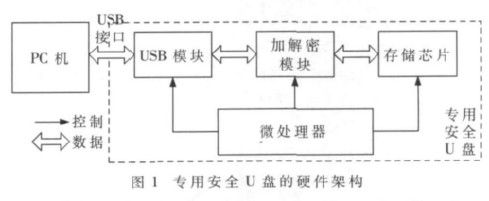

专用安全U盘的硬件架构如图1所示,主要由微处理器、存储芯片(NandFlash)、USB模块及加解密模块等组成[2]。当U盘和PC机进行数据传输时,加解密模块在微处理器的控制下对数据流进行加解密操作,使得U盘存储芯片中的数据都以密文形式存在。当PC机对数据进行读写时,首先需要进行身份认证,若认证不通过,则读写操作不能进行,即使攻击者将安全U盘物理分解,直接读取存储芯片,而由于存储芯片中的数据是以密文形式存在的,攻击者也只能获得数据的密文。安全U盘通过加解密和认证相结合的方法,保证其存储数据的安全性。

专用安全U盘由于保密性高的优势,在一些特殊场合得到了广泛的应用。然而安全U盘也有自身的不足,主要表现在:

(1)成本高。与普通U盘相比,安全U盘硬件构造复杂,成本通常为普通U盘的数倍乃至数十倍。

(2)开发难度大。安全U盘开发涉及USB协议、加解密算法、密钥保护方案、NandFlash读写等,其涉及面广、开发周期长、工作量大。

(3)密钥、算法、数据保存在同一载体中。若安全U盘丢失,则直接导致密钥、算法和数据一起丢失,不但增大了数据被破解的可能性,而且有可能导致密码算法的丢失。

1.2 U盘安全控制器的系统设计

本文借鉴安全U盘的优缺点,按照方便快捷、安全性高的原则,利用SoPC技术,设计实现了U盘安全控制器。片上可编程系统SoPC技术是基于可编程编辑器件PLD解决方案的片上系统(SoC)。SoPC是PLD和ASIC技术融合的结果,是一种软硬件协同设计技术。SoPC可以方便地将硬件系统(包括处理器、存储器、外设和自定义逻辑电路等)和固件集成到一个PLD器件上,构建成一个可编程的片上系统,具有设计灵活、可裁剪、易升级、可编程等优点,同时还有丰富的IP核资源可供使用[3]。

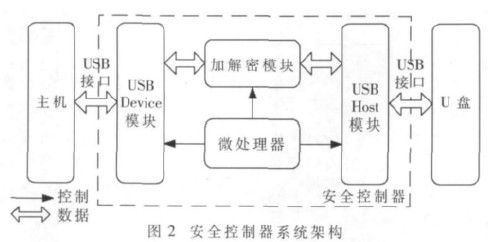

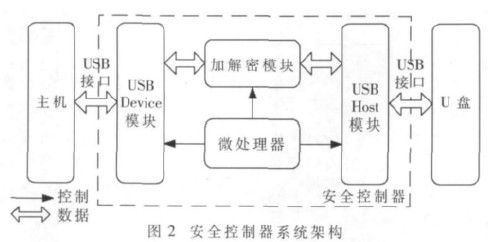

本文所设计的安全控制器系统架构如图2所示,安全控制器位于PC机和U盘之间,主要由USB Device模块、USB Host模块、微处理器、缓冲区、加解密模块等组成。控制器对于PC机表现为一个USB大容量存储(MassStorage)类设备,而对于U盘,则表现为一个USB Host。USB Device模块负责接收PC机的命令和数据,USB Host模块负责向U盘等USB发送命令和数据,加解密模块则完成数据的加解密,整个系统在微处理器的控制下工作。

2 安全控制器硬件架构的设计实现

本设计采用USB接口芯片+FPGA的方案来实现安全控制器的硬件架构,通过微处理器器对USB接口芯片的控制即可实现USB通信。采用USB接口芯片有助于降低开发费用,缩短系统的开发周期。

2.1 USB接口芯片选型

本设计中,安全控制器既要实现USB Host的功能,又要实现USB Device的功能。因此,若能采用一片USB接口芯片实现两者的功能,则有助于降低硬件系统的复杂性。综合USB芯片的功能需求、价格、硬件复杂性等因素,本设计选用NXP公司的ISP1761作为USB接口芯片。

ISP1761是一个单芯片的高速USB OTG 控制器,在其单芯片上集成了一个OTG控制器、一个主机控制器和一个外设控制器,主机和外设控制器兼容USB2.0协议,并支持480 Mb/s的高速传输。ISP1761有3个USB接口,接口1可以被配置为Host接口、Device接口或者OTG接口,接口2、3只能被配置为Host接口。在OTG模式下,ISP1761的接口1可通过跳线灵活配置成Host接口或Device接口。ISP1761可以直接与目前市场上的大多数带寻址功能的微处理器直接连接,微处理器通过读写ISP1761内部的寄存器或存储器即可实现USB通信功能。ISP1761支持DMA传输,可以提高数据的吞吐率[4]。

2.2 控制器整体硬件架构

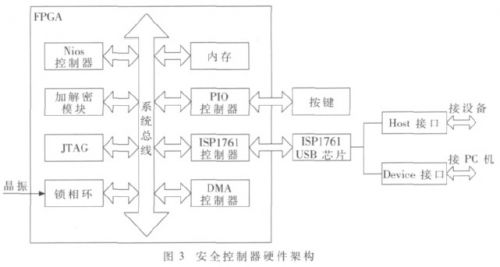

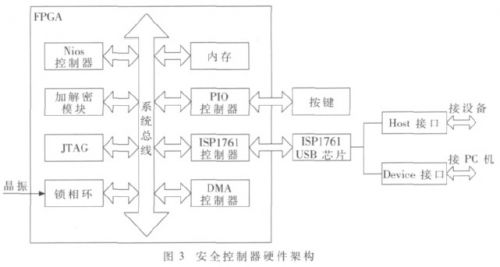

安全控制器整体硬件架构如图3所示,由SoPC模块和ISP1761芯片及按键组成。SoPC模块使用Altera公司提供的开发工具SoPC Builder生成,主要由NiosⅡ控制器、内存、加解密模块、JTAG、ISP1761控制器、锁相环、PIO控制器和DMA控制器组成。

NiosⅡ控制器作为整个系统的核心,完成对各个模块的调度和控制;锁相环为系统各个模块提供所需要的时钟;加解密模块完成数据流的加解密功能;ISP1761控制器则用来连接NiosⅡ控制器和ISP1761芯片,通过该控制器,NiosⅡ处理器可以访问ISP1761芯片内部的寄存器和存储器;DMA控制器负责PC机到控制器、控制器到U盘的数据传输,提高数据传输速率。ISP1761芯片分别连接主机和U盘,在NiosⅡ的控制下实现USB Host接口和USB Device接口的功能。

本文针对U盘的安全隐患,分析目前较为常见的解决方法,利用SoPC技术,设计实现了一款基于NiosⅡ处理器的U盘安全控制器。该控制器位于PC机和U盘之间,通过对U盘进行扇区级的加解密操作,将普通U盘升级为安全U盘,保证U盘中数据的安全性。控制器遵循USB MassStorage类协议,无需专用驱动,即插即用,具有灵活方便、安全性高等优点[1]。

1 安全控制器的整体设计

1.1 安全U盘解决方案分析

U盘最为突出的安全问题是其内部所存储的数据都以明文形式存储,任何人得到该存储载体,即可对其中的数据进行任意的操作。因此,普通U盘一旦丢失,其存储的数据则毫无安全性可言。针对这一问题,目前已经有多种解决方法,其中较为常见、安全性较高的是采用专用安全U盘的方法。

专用安全U盘的硬件架构如图1所示,主要由微处理器、存储芯片(NandFlash)、USB模块及加解密模块等组成[2]。当U盘和PC机进行数据传输时,加解密模块在微处理器的控制下对数据流进行加解密操作,使得U盘存储芯片中的数据都以密文形式存在。当PC机对数据进行读写时,首先需要进行身份认证,若认证不通过,则读写操作不能进行,即使攻击者将安全U盘物理分解,直接读取存储芯片,而由于存储芯片中的数据是以密文形式存在的,攻击者也只能获得数据的密文。安全U盘通过加解密和认证相结合的方法,保证其存储数据的安全性。

专用安全U盘由于保密性高的优势,在一些特殊场合得到了广泛的应用。然而安全U盘也有自身的不足,主要表现在:

(1)成本高。与普通U盘相比,安全U盘硬件构造复杂,成本通常为普通U盘的数倍乃至数十倍。

(2)开发难度大。安全U盘开发涉及USB协议、加解密算法、密钥保护方案、NandFlash读写等,其涉及面广、开发周期长、工作量大。

(3)密钥、算法、数据保存在同一载体中。若安全U盘丢失,则直接导致密钥、算法和数据一起丢失,不但增大了数据被破解的可能性,而且有可能导致密码算法的丢失。

1.2 U盘安全控制器的系统设计

本文借鉴安全U盘的优缺点,按照方便快捷、安全性高的原则,利用SoPC技术,设计实现了U盘安全控制器。片上可编程系统SoPC技术是基于可编程编辑器件PLD解决方案的片上系统(SoC)。SoPC是PLD和ASIC技术融合的结果,是一种软硬件协同设计技术。SoPC可以方便地将硬件系统(包括处理器、存储器、外设和自定义逻辑电路等)和固件集成到一个PLD器件上,构建成一个可编程的片上系统,具有设计灵活、可裁剪、易升级、可编程等优点,同时还有丰富的IP核资源可供使用[3]。

本文所设计的安全控制器系统架构如图2所示,安全控制器位于PC机和U盘之间,主要由USB Device模块、USB Host模块、微处理器、缓冲区、加解密模块等组成。控制器对于PC机表现为一个USB大容量存储(MassStorage)类设备,而对于U盘,则表现为一个USB Host。USB Device模块负责接收PC机的命令和数据,USB Host模块负责向U盘等USB发送命令和数据,加解密模块则完成数据的加解密,整个系统在微处理器的控制下工作。

2 安全控制器硬件架构的设计实现

本设计采用USB接口芯片+FPGA的方案来实现安全控制器的硬件架构,通过微处理器器对USB接口芯片的控制即可实现USB通信。采用USB接口芯片有助于降低开发费用,缩短系统的开发周期。

2.1 USB接口芯片选型

本设计中,安全控制器既要实现USB Host的功能,又要实现USB Device的功能。因此,若能采用一片USB接口芯片实现两者的功能,则有助于降低硬件系统的复杂性。综合USB芯片的功能需求、价格、硬件复杂性等因素,本设计选用NXP公司的ISP1761作为USB接口芯片。

ISP1761是一个单芯片的高速USB OTG 控制器,在其单芯片上集成了一个OTG控制器、一个主机控制器和一个外设控制器,主机和外设控制器兼容USB2.0协议,并支持480 Mb/s的高速传输。ISP1761有3个USB接口,接口1可以被配置为Host接口、Device接口或者OTG接口,接口2、3只能被配置为Host接口。在OTG模式下,ISP1761的接口1可通过跳线灵活配置成Host接口或Device接口。ISP1761可以直接与目前市场上的大多数带寻址功能的微处理器直接连接,微处理器通过读写ISP1761内部的寄存器或存储器即可实现USB通信功能。ISP1761支持DMA传输,可以提高数据的吞吐率[4]。

2.2 控制器整体硬件架构

安全控制器整体硬件架构如图3所示,由SoPC模块和ISP1761芯片及按键组成。SoPC模块使用Altera公司提供的开发工具SoPC Builder生成,主要由NiosⅡ控制器、内存、加解密模块、JTAG、ISP1761控制器、锁相环、PIO控制器和DMA控制器组成。

NiosⅡ控制器作为整个系统的核心,完成对各个模块的调度和控制;锁相环为系统各个模块提供所需要的时钟;加解密模块完成数据流的加解密功能;ISP1761控制器则用来连接NiosⅡ控制器和ISP1761芯片,通过该控制器,NiosⅡ处理器可以访问ISP1761芯片内部的寄存器和存储器;DMA控制器负责PC机到控制器、控制器到U盘的数据传输,提高数据传输速率。ISP1761芯片分别连接主机和U盘,在NiosⅡ的控制下实现USB Host接口和USB Device接口的功能。

USB SoC 电路 FPGA NXP Altera 相关文章:

- 用电子技术最大化太阳能电池板输出功率(05-18)

- 2009视频监控:网络化及其推动的几大趋势(06-03)

- 与MSP430 USI端口配合使用ADS8361(06-18)

- 辰汉电子推出低成本快速量产视频监控方案+4路输入方案(06-24)

- 用于风力发电设备的连接器的简易安装与维护(06-21)

- 解读USB-IF电池充电规范(10-27)