基于FPGA的IIR数字滤波器的设计方案

1.引言

数字滤波器在通信、自动控制、雷达、军事、航空航天、医疗、家用电器等众多领域得到了广泛的应用。其中IIR数字滤波器和FIR数字滤波器是目前人们使用较多的两种。数字滤波器通常采用计算机软件、专用数字滤波器、DSP器件或可编程逻辑器件(如FPGA)实现。因为,用FPGA实现数字滤波器具有实时性强、灵活性高、处理速度快以及小批量生产成本低等优点,所以得到了较为广泛的应用。本文以巴特沃思数字带通滤波器为例,较为详细地介绍了其设计和实现方法。给定巴特沃兹数字带通滤波器的抽样频率为500Hz,上、下边带截止频率分别为150Hz和30Hz.

2.滤波器的系统模型

双线性变换法是在低通滤波器的基础上采用频率变换法把低通滤波器转换成所需要滤波器的。据此方法,我们得到如下滤波器的系统模型:

3.Matlab仿真

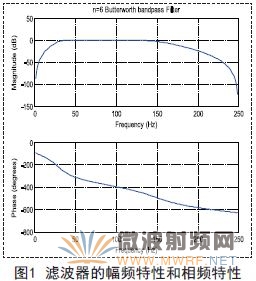

针对式(1)所描述的系统模型,利用Matlab软件工具箱函数freqz(b,a,N,Fs)绘制出其幅频特性和相频特性,以检验参数的正确性。该滤波器的幅相频率特性如图1所示。

由图1可见,系统的上、下边带分别为150Hz和30Hz,满足系统设计要求。

4.FPGA设计

4.1 滤波器的结构

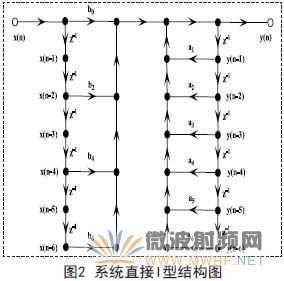

同一系统函数的IIR滤波器可以用不同的结构来实现,如直接I型、直接II型(典范型)、级联型和并联型。不同的结构有不同的特点,为便于硬件实现及容易确定数据位数,本文选用直接I型这一结构形式。

系统的直接I型结构如图2所示。

4.2 FPGA主要模块

(1)D触发器模块

使用D触发器来实现图2中所需的延时功能。每当时钟上升沿到来时,便对输入的数据进行锁存。D触发器可以利用Quartus II软件中LPM宏模块定制实现。

(2)乘累加模块

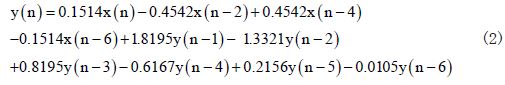

由式(1)所描述的滤波器的系统模型,可得所对应的差分方程如下:

乘累加模块承担式(2)中乘累加的计算工作。

5.系统框图及实验波形图

利用数字滤波器实现模拟信号滤波的系统结构框图如图3所示。

模拟输入信号经A/D转换器转换为数字信号,用FPGA数字滤波器进行滤波处理,再经D/A转换器转换为模拟输出信号,完成模拟信号的滤波处理。FPGA芯片采用的是Cyclone II系列EP2C5T144C8型FPGA.A/D和D/A转换器采用的康芯高速ADC/DAC模块。

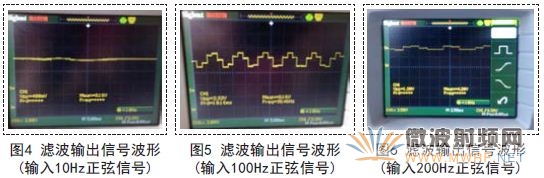

输入峰峰值为5V的正弦信号,周期分别为10Hz、100Hz和200Hz,经滤波系统处理后所得输出信号波形分别如图4、5、6所示,输出信号幅度分别为400mV、2.32V、1.2V.

6.结语

本方案利用FPGA实现了巴特沃兹IIR数字带通滤波器,并给出较为详细的方案设计过程。实验结果证明了所设计的滤波器完全满足预定设计要求,从而也证实了本方案的有效性、可行性。

- 可以连续改变截止频率的电压控制通用滤波器(05-26)

- 用Multisim分析二阶低通滤波器电路(09-08)

- 选择RF和微波滤波器的八大窍门(04-28)

- 滤波器功率最大而灵敏度却最低(11-14)

- 微波滤波器的实现(11-02)

- 网络综合法得到的低通原型滤波器(03-10)