一种适用于射频集成电路的抗击穿LDMOS设计

阱结构可以是一个无任何介质的深槽,深槽的作用主要是从物理结构上改变器件的电场强度分布,减弱栅极末端的电场集中。为了进一步改善器件的电场分布,可在 阱结构中填充低介电常数的绝缘介质。阱中低介电常数的介质一方面截断器件的曲面结,消除电场集中:另一方面抑制了平面工艺的横向扩散,可承受更高的峰值电 场。

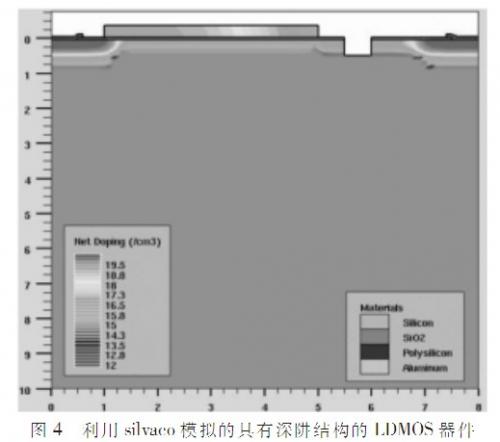

Si、SiC、SiO2、GaAs的相对介电常数分别为11.6、10.0、3.9、13.1。相对而言,SiO2具有低的介电常数,适合填充在LDMOS的深阱结构中。

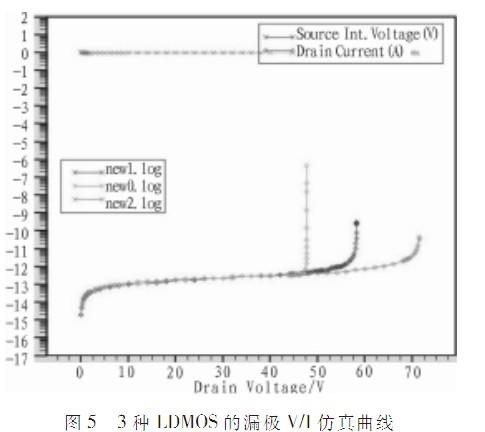

保持LDMOS器件掺杂浓度、栅长、阱宽等参数不变,如图5所示。new0.Log、new1.Log、new2.Log分别代表基本LDMOS、有深槽 的LDMOS以及完全填入SiO2的深阱的LDMOS漏极V/I仿真曲线。本文采用的深阱结构其阱宽和阱深都为0.5μm,从图5中可以看出,由于深槽的 作用,LDMOS击穿电压提高了10 V,当进一步在深槽中填入SiO2时,其击穿电压可再次提高12 V。通过对比分析可以说明,采用阱结构技术可以明显提高器件的抗击穿能力。

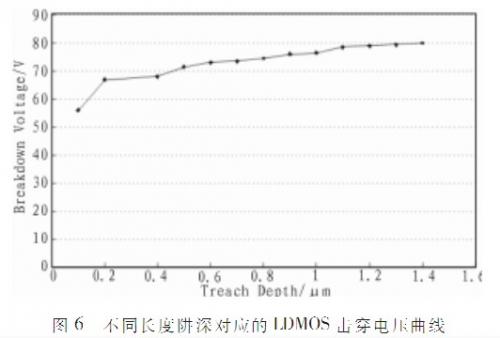

通过进一步仿真实验发现,器件耐压性能与阱宽及阱深的尺寸有关。保持漂移区长度不变,阱宽为固定值0.5μm,图6为不同长度阱深对应的器件击穿电压曲 线。从图6中可以看出,随着阱深的加大,器件的抗击穿能力加强,这是由于阱深越大,耗尽区俞难越过阱区,且体硅中承受的最大电场的范围越大,LDMOS的 耐压就越高。

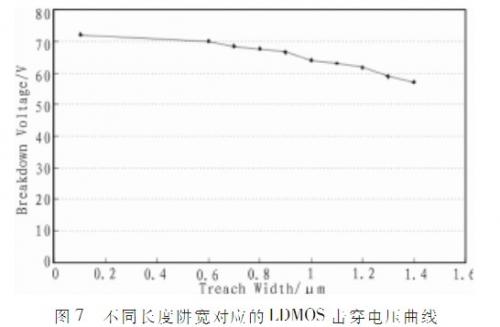

同样,保持漂移区长度不变,阱深为固定值0.5μm,图7为不同长度阱宽对应的器件击穿电压曲线。击穿电压随着阱宽的增加反而减小,这是因为阱宽的增加使得漂移区长度减小,总的耐压也就随之减小。

选择适当的阱宽及阱深,在阱中掺杂低介电常数介质,如SiO2,通过优化器件的结构参数可以得到击穿电压的最大值。

采用此深阱结构最大的优点是工艺方法简单有效,并且可利用深阱的宽度和深度以及深阱中填入何种介质或填入介质的多少来控制LDMOS的击穿电压,在实际工艺操作过程中可控性强。

3 结论

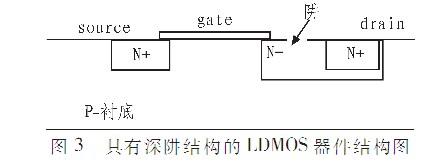

LDMOS击穿电压易发生在栅极末端,器件衬底上添加埋层可以降低沟道附近的等位线曲率从而提高其击穿电压。漂移区将漏区与沟道隔离,抑制了器件的沟道调 制,在一定掺杂范围内,漂移区浓度越低,击穿电压越高。衬底浓度越低,雪崩击穿越容易发生,击穿电压就越低。本文采用的深阱结构主要为了减小栅极末端的电 场强度,消除电场集中,进而提高其抗击穿能力。

另外,由于栅极界面存在电荷,栅末端的峰值电场随栅长的增加而增加,为了抑制峰值电场集中导致器件的击穿,栅长不宜较长。漂移区长度可适当加大,阱深可尽量取较大值,结合器件掺杂浓度,最终可使射频LDMOS的抗击穿能力达到最优。

文中设计的LDMOS器件主要是在耐压特性上做了改进,相对于RESURF技术、漂移区变掺杂、加电阻场极板、内场限环等技术而言,具有工艺简单,可控性 强的优点。其较高的抗击穿能力可适用于射频集成电路,如移动通信基站。当然,若将此器件应用于基站,还需要考虑射频LDMOS的其它电学特性,使器件的各 个参数达到作为基站功率放大器的要求。

- 射频/无线芯片测试基础(12-07)

- 什么是射频?(01-09)

- 降低CDMA/WCDMA蜂窝电话的射频功耗(03-18)

- 浅谈蓝牙射频技术(04-18)

- 射频单位的相互转换(09-14)

- 微波射频系列图书(书评)(12-07)