多通道高精度数据采集电路设计

时间:12-14

来源:互联网

点击:

5 数据采集的软件设计

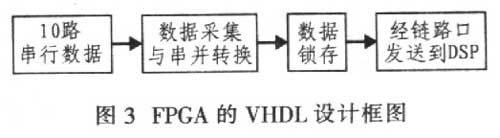

软件部分包括TSl01软件设计和FPGA软件设计,FPGA软件设计采用VHDL实现。其结构如图3所示。

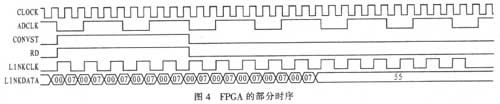

FPGA的主要操作是将5个ADS8361的10路串行采集数据转换成20个8 bit数据,再将数据锁存,同时产生链路时钟,将锁存后的数据发送到TSl01链路口。需要实现的时序如图4所示,其中CLOCK是TSlOl外部时钟,ADCLK是ADS8361的工作时钟,是CLDCK的5分频,占空比为60%,CONVST与RD相连接,LINKCLK是链路时钟,LINKDATA是链路数据。

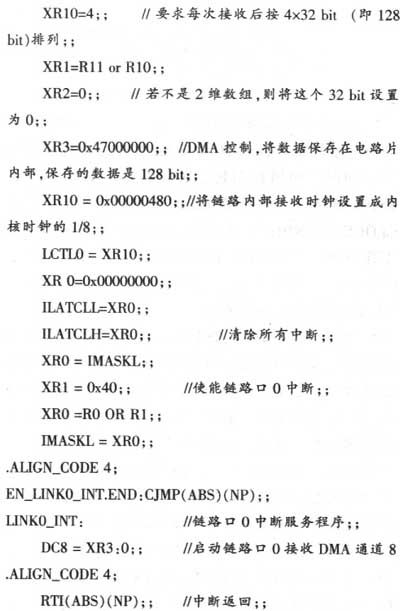

使用链路传输时,TSl01在链路时钟的上升沿和下降沿都锁存数据,20个8 bit数据需要lO个链路脉冲,而链路口每次至少需要传输128 bit的数据,即至少需要8个脉冲,且发送数据需要的脉冲数必须为8的倍数。所以设计中每次通过链路发送数据的脉冲数为16个,前10个传输A/D转换器采集到的数据,其后的6个脉冲发送0x55。发送到链路的数据是A/D转换器上次转换的结果。TSl01可以设置链路口工作时钟为内核时钟的2、3、4、8分频,设计中TSl01外部时钟CLOCK是50MHz,内核时钟是CLOCK的5倍频即250 MHz,链路口接收数据时FPGA给TSIOI的链路时钟LINKCLK是25 MHz TSl01链路口工作时钟应尽量接近链路时钟LINKCLK,所以设置TSl01链路口工作时钟为内核时钟的8分频即31.25 MHz。

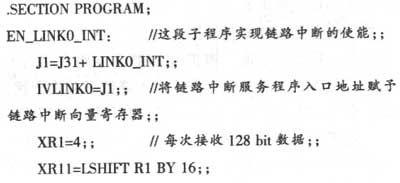

系统采用链路中断方式接收FPGA送来的数据,链路中断方式数据接收的程序如下:

6 A/D转换器电路的设计和使用

设计高精度A/D转换器的关键是保证有效位数,ADS8361的输入动态范围为:±2.5 V,每个量化单位对应0.076 mV,因此应设法降低噪声和干扰。噪声和干扰的来源主要有二种:一种是A/D转换器自身的噪声如量化噪声等,另一种是周围电路产生的噪声干扰。前者是A/D转换器固有的,后者的大小远远超过前者,特别是电源、模拟/电路数字电路之间的干扰。ADS8361的差分输入方式大大降低了共模干扰。设计中主要考虑如何在电路中减少其他噪声和干扰。

电源设计是抑制噪声的关键,本文介绍的设计具有多种电压(模拟5 V、-5 V和数字3.3 V、1.2V等)并且是混合模拟和数字信号的板级设计,选择合适的电源电路,合理地进行电源层和地层的切割是很重要的。开关电源具有体积小、效率高、输出稳定等优点,同时能够很好地解决TSlOl的上电次序问题,但纹波明显。开关频率越高输出电压纹波越小,电路中选用的电感器在10μH"200 μH为宜,电路中可以使用ESR小、容值大的电容器构成去耦电路,同时在板上放置多种电容器进行滤波。

减少数字信号干扰也可以有效提高A/D转换器的精度,布板和布线时要使ADS8361模拟差分信号输入区域尽量远离数字信号,FPGA设计中尽量避免多个信号电平同时翻转,同时给A/D转换器提供良好的工作时钟,应使用串联终端法,串联1只小电阻器可以很好减少时基抖动,时钟信号进入A/D转换器的布线越短越好,同时不要离数字信号太近,也不要靠近模拟区,否则会增加模拟区的噪声。同时要注意单点共地,在共地的点上串接1个磁珠。设计中使用了多层板布局,在轻载情况下可以将输出电压纹波减到4mV。

7 结束语

笔者设计一种通过TSl01链路口进行多A/D转换器多通道高精度数据采集的实现方法,在DSP信号采集处理系统中可以不占用总线,实现并行数据传输和处理,有更高的实时性,同时探讨了如何提高A/D转换器精度的问题。该设计方法已经应用于多种并行和串行A/D转换电路中,具有通用性。

DSP 总线 ADI FPGA 电压 电路 ADC VHDL 开关电源 电感 电容 电容器 电阻 相关文章:

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 智能视频多媒体技术的应用(05-31)

- 提高实时系统数据采集质量的研究(04-09)

- 2009视频监控:网络化及其推动的几大趋势(06-03)

- 高清化:视频监控领域的下一个里程碑(06-04)