一种时钟与功耗管理控制器的硬件实现

时间:12-08

来源:互联网

点击:

时钟分频选择模块

时钟分频选择模块负责选择和产生整个系统工作所需的时钟信号。时钟的可选范围和时钟切换的稳定,对于 PMC和整个芯片都十分重要。本文采用2MHz"5MHz的主晶振时钟和经过DPLL倍频后的100MHz"300MHz时钟作为时钟源,再经过多种倍率的可选分频,最终获得一个比较宽的可选时钟范围。为了提高时钟切换的稳定性,还专门设计了一种无毛刺时钟切换电路GCM(专利电路),可以在三个周期之内平稳切换两路各种周期差异的时钟,并同时改善输出时钟的质量。在本设计中,GCM用以实现晶振和DPLL两路时钟的平稳切换。

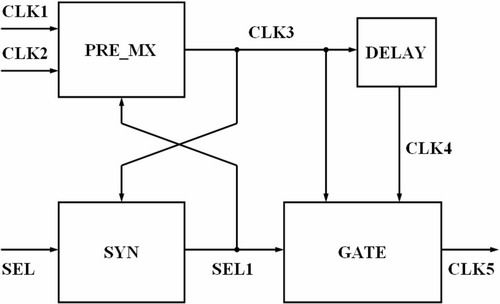

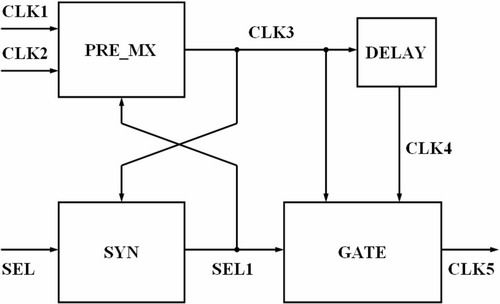

GCM的原理框图如图3所示。用普通二选一电路(PRE_MX)初步切换得到的时钟CLK3同步外界输入的时钟选择信号SEL;得到的同步选择信号SEL1实际控制时钟的切换,同时SEL1再经过进一步同步得到屏蔽残缺周期的门控信号;最后用门控信号去除时钟切换中的不稳定部分,得到平稳的时钟输出。

图3 GCM无毛刺切换电路结构框图

复位信号控制模块

复位信号控制模块负责接收外部复位信号和软件复位信号,并按照工作时序的需要,分别向芯片的各个功能模块发出复位信号。可以向某些对复位有特定时序和顺序要求的模块单独发送复位信号。并且可以区分软、硬件复位,对不同的模块集合进行复位。

系统时钟唤醒模块

系统时钟唤醒模块负责恢复关闭的系统时钟,并保证时钟稳定可用。在系统从节能模式(IDLE或SLEEP)恢复到正常工作模式(NORMAL或SLOW)的过程中,系统必须将已关闭的时钟恢复到正常稳定的状态。当系统从IDLE模式下唤醒时,需要恢复内核的时钟。本模块可以接收外部的唤醒信号形成一个唤醒中断,提交到中断控制器,这与其他所有模块产生的内部中断一样,可以唤醒内核时钟,使系统恢复正常工作。当系统从SLEEP模式下唤醒时,需要恢复整个系统的时钟。本模块可以接收外部唤醒信号或者RTC的定时唤醒信号,并稳定开启和恢复系统时钟,最终切换到正常的工作模式下。

AMBA总线接口模块

RISC的内核通过APB总线读写PMC时钟功耗管理单元的寄存器,这些寄存器映射到统一的地址空间。另外,输出到各个模块的时钟信号也通过这个模块进行开关控制。PMC的主要控制寄存器描述如表1所示。

仿真结果及流片

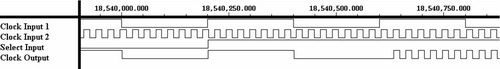

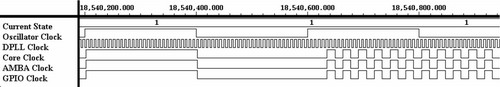

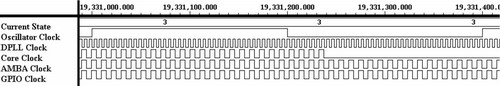

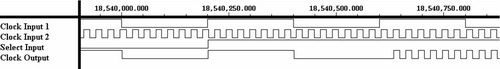

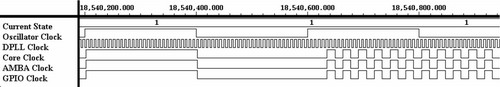

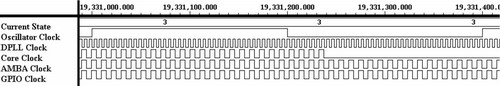

PMC时钟功耗管理控制器采用RTL级的Verilog HDL进行描述。使用A720T内核仿真模型、AMBA总线和中断控制器等功能模块的RTL级Verilog代码,以及本设计的源代码,共同组成完整的仿真环境。其中A720T内核是ARM公司设计的一款ARM7系列内核,在ARM7TDMI基础上增加了虚拟地址与物理地址转换器MMU、指令Cache和数据Cache。A720T内核仿真模型是ARM公司提供给授权开发机构用以完成仿真的功能模型,它不能被综合,只能用于功能验证。使用Synopsys公司的EDA工具VCS对本设计的功能进行仿真和验证。其中GCM模块还使用HSIM进行了SPICE晶体管级的模型仿真。GCM时钟切换的仿真结果如图4所示,PMC时钟变频和工作模式切换的仿真结果如图5所示,PMC进入IDLE节能模式的仿真波形如图6所示。从仿真结果可以看出,PMC能够正常完成预计功能,可以稳定地改变时钟频率,并根据工作模式开关时钟。

图4 GCM时钟切换仿真波形图

图5 PMC时钟变频和工作模式切换仿真波形图

图6 PMC进入IDLE节能模式仿真波形图

PMC时钟功耗管理控制器已成功应用于东南大学ASIC工程中心自主开发的基于ARM7的嵌入式处理器Garfield4Plus中。通过该芯片的实际流片,PMC获得实片测试的机会。测试结果表明,PMC能够正常稳定地完成预计功能,包括工作频率的实时配置、工作模式的切换以及芯片的节能和唤醒。

结语

本文描述的PMC设计的特点在于工作时钟的统一和时钟结构的清晰简洁。GCM无毛刺时钟切换电路,使得多个时钟源(包括每个时钟源的各种不同的频率配置)在真正提供给系统使用之前就得到了很好的统一。这种时钟结构可以带来更好的系统稳定性和时序上的余量,也就代表着可以使用更高的系统时钟频率。

今后对PMC的优化应当重点关注以下两点。一方面,应当使PMC在针对不同系统的具体特点时,能够对功耗的实时管理进行更灵活的配置。既要保证最大限度的节能,又要增加PMC本身的可移植性。另一方面,应当进一步探索更科学的结构,使提供给系统的时钟在更灵活的配置方式下,仍然能够保证安全和稳定。

时钟分频选择模块负责选择和产生整个系统工作所需的时钟信号。时钟的可选范围和时钟切换的稳定,对于 PMC和整个芯片都十分重要。本文采用2MHz"5MHz的主晶振时钟和经过DPLL倍频后的100MHz"300MHz时钟作为时钟源,再经过多种倍率的可选分频,最终获得一个比较宽的可选时钟范围。为了提高时钟切换的稳定性,还专门设计了一种无毛刺时钟切换电路GCM(专利电路),可以在三个周期之内平稳切换两路各种周期差异的时钟,并同时改善输出时钟的质量。在本设计中,GCM用以实现晶振和DPLL两路时钟的平稳切换。

GCM的原理框图如图3所示。用普通二选一电路(PRE_MX)初步切换得到的时钟CLK3同步外界输入的时钟选择信号SEL;得到的同步选择信号SEL1实际控制时钟的切换,同时SEL1再经过进一步同步得到屏蔽残缺周期的门控信号;最后用门控信号去除时钟切换中的不稳定部分,得到平稳的时钟输出。

图3 GCM无毛刺切换电路结构框图

复位信号控制模块

复位信号控制模块负责接收外部复位信号和软件复位信号,并按照工作时序的需要,分别向芯片的各个功能模块发出复位信号。可以向某些对复位有特定时序和顺序要求的模块单独发送复位信号。并且可以区分软、硬件复位,对不同的模块集合进行复位。

系统时钟唤醒模块

系统时钟唤醒模块负责恢复关闭的系统时钟,并保证时钟稳定可用。在系统从节能模式(IDLE或SLEEP)恢复到正常工作模式(NORMAL或SLOW)的过程中,系统必须将已关闭的时钟恢复到正常稳定的状态。当系统从IDLE模式下唤醒时,需要恢复内核的时钟。本模块可以接收外部的唤醒信号形成一个唤醒中断,提交到中断控制器,这与其他所有模块产生的内部中断一样,可以唤醒内核时钟,使系统恢复正常工作。当系统从SLEEP模式下唤醒时,需要恢复整个系统的时钟。本模块可以接收外部唤醒信号或者RTC的定时唤醒信号,并稳定开启和恢复系统时钟,最终切换到正常的工作模式下。

AMBA总线接口模块

RISC的内核通过APB总线读写PMC时钟功耗管理单元的寄存器,这些寄存器映射到统一的地址空间。另外,输出到各个模块的时钟信号也通过这个模块进行开关控制。PMC的主要控制寄存器描述如表1所示。

仿真结果及流片

PMC时钟功耗管理控制器采用RTL级的Verilog HDL进行描述。使用A720T内核仿真模型、AMBA总线和中断控制器等功能模块的RTL级Verilog代码,以及本设计的源代码,共同组成完整的仿真环境。其中A720T内核是ARM公司设计的一款ARM7系列内核,在ARM7TDMI基础上增加了虚拟地址与物理地址转换器MMU、指令Cache和数据Cache。A720T内核仿真模型是ARM公司提供给授权开发机构用以完成仿真的功能模型,它不能被综合,只能用于功能验证。使用Synopsys公司的EDA工具VCS对本设计的功能进行仿真和验证。其中GCM模块还使用HSIM进行了SPICE晶体管级的模型仿真。GCM时钟切换的仿真结果如图4所示,PMC时钟变频和工作模式切换的仿真结果如图5所示,PMC进入IDLE节能模式的仿真波形如图6所示。从仿真结果可以看出,PMC能够正常完成预计功能,可以稳定地改变时钟频率,并根据工作模式开关时钟。

图4 GCM时钟切换仿真波形图

图5 PMC时钟变频和工作模式切换仿真波形图

图6 PMC进入IDLE节能模式仿真波形图

PMC时钟功耗管理控制器已成功应用于东南大学ASIC工程中心自主开发的基于ARM7的嵌入式处理器Garfield4Plus中。通过该芯片的实际流片,PMC获得实片测试的机会。测试结果表明,PMC能够正常稳定地完成预计功能,包括工作频率的实时配置、工作模式的切换以及芯片的节能和唤醒。

结语

本文描述的PMC设计的特点在于工作时钟的统一和时钟结构的清晰简洁。GCM无毛刺时钟切换电路,使得多个时钟源(包括每个时钟源的各种不同的频率配置)在真正提供给系统使用之前就得到了很好的统一。这种时钟结构可以带来更好的系统稳定性和时序上的余量,也就代表着可以使用更高的系统时钟频率。

今后对PMC的优化应当重点关注以下两点。一方面,应当使PMC在针对不同系统的具体特点时,能够对功耗的实时管理进行更灵活的配置。既要保证最大限度的节能,又要增加PMC本身的可移植性。另一方面,应当进一步探索更科学的结构,使提供给系统的时钟在更灵活的配置方式下,仍然能够保证安全和稳定。

EDA 仿真 嵌入式 SoC 电路 总线 Verilog ARM PIC 相关文章:

- 基于SOPC的简易误码率测试仪设计技术(04-13)

- 基于FPGA的可编程PWM电路设计(05-19)

- 多芯片组件技术的发展及应用(06-07)

- 基于PCI的遥测解调及遥控注入测试卡的设计与实现(06-12)

- 高速数字系统中信号完整性及实施方案(06-28)

- 三种常用SoC片上总线的分析与比较(07-12)