一种高效实用的发动机片上爆震检测解决方案

1 发动机爆震及控制

现代发动机管理系统(EMS) 中,爆震控制是核心算法之一。由于频繁爆震会损坏发动机,ECU必须采取措施制止爆震。为避免爆震,可以保守地设置点火提前角。但这以牺牲最佳点火时机为代价,使动力和燃油效率性能降低。增加爆震控制功能,发动机就可以实时调节点火时间。它可以逐渐加快点火正时,以提供更大的动力。当监测到爆震时,点火正时才后跳几度来消除爆震,一般来说,爆震系统能提升约3%的动力性和5%的燃油经济性。

爆震控制算法的最大挑战是实现有效的爆震检测。因为要快速准确地(如千分之一秒内)从发动机的正常噪音中分辨出爆震绝非易事,通常用专门的ASIC来完成。但MCU的功能日益强大,在系统设计中,要求MCU在控制发动机的同时完成精准的爆震检测,目的是降低成本并提高系统可靠性。典型的MCU如飞思卡尔的Copperhead(MPC5554),其内核强大的数字信号处理能力可以胜任各种爆震检测算法。

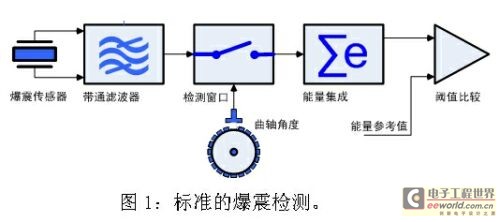

2 爆震检测的标准方法

爆震发生在做功冲程刚开始的时间里(压缩冲程活塞运动到最高点(TDC)稍后的时间里)。我们不仅知道爆震共鸣声的大致频率(约为7K及其谐波),还知道爆震发生的大致曲轴角度范围。图1是根据该原理的一个标准的爆震检测框图。常用的爆震传感器内部封装一个压电陶瓷,将监听到的发动机运行声音转换为电信号。来自爆震传感器的电信号通过一个带通滤波器。带通滤波器将所需要的频率信号提取出来。根据曲轴角度信号产生一个角度窗口,这个窗口覆盖了爆震可能发生的时段。这样,从检测窗口输出的信号就是在时域和频域都做了选择的,我们感兴趣的爆震信号。为了判断爆震的强度,最直接的方法就是将信号绝对值加起来,即能量集成。将能量集成后的数据与预先设定的爆震能量参考值进行比较,就可以判断出爆震是否发生。

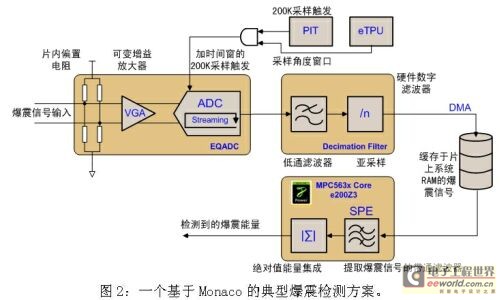

3 基于Monaco的片上爆震检测方案

飞思卡尔推出了第一款90纳米技术的专门针对中低端EMS应用的微处理器系列Monaco(MPC563xM)。 Monaco是基于Power Architecture架构的32位微处理器,其许多片上外设的及联动逻辑设计充分考虑了爆震检测的需要。把这些外设有效的配置运作起来就能够高效地实现各种爆震检测方案。对于相对简单的爆震算法,一旦CPU将这些外设初始化好,它们甚至可以自治地运作,不再需要CPU的实时干预。即使对比较复杂的爆震算法,这些外设也能够完成绝大部分的工作,极大降低了CPU的运算负荷。图2是基于Monaco的一个比较典型的片上爆震检测方案结构图。图中展示了所有与爆震功能有关的外设及逻辑连接。ADC的输入端有可配置阻值的4个偏置电阻和一个可变增益放大器(VGA),用于使动态范围最大化以及补偿发动机传感器输出信号幅度的变化。

4 爆震信号的采样

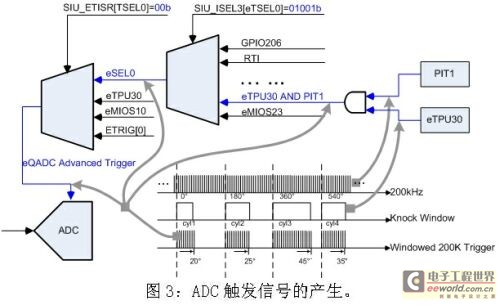

Monaco的ADC支持高达1MHz的采样频率及8、 10或12位的采样精度。Monaco上周期中断定时器(PIT)的一个特性是:不仅能够配置成周期中断,还能够配置成周期地直接触发片上的EQADC。本例将PIT周期置为5us并触发AD转换,于是得到一个精确的200kHz的AD转换触发信号。

爆震只在特定角度窗内(TDC稍后的一段时间)才可能发生,故只需让ADC在恰当的窗口内工作。这个窗口由eTPU产生。eTPU是一个独立于内核以外的 RISC引擎,在Monaco中eTPU与32个定时通道紧密组合在一起,专注于复杂、高实时性的定时逻辑。其最重要的功能是根据输入的曲轴和凸轮轴的脉冲信号来产生发动机工作的角度基准。这样使EMS的控制算法可基于角度空间,eTPU还同时提供基于角度的喷油和点火控制功能。飞思卡尔提供了完备的 eTPU微码和全面的库函数以便用户使用。其中包括爆震窗口的产生:在不同的发动机转速下对于不同的汽缸都能实时给出所期望的基于角度的窗口。

Monaco 片上外设间的联动逻辑允许ADC支持高级外部触发模式。图3描述了在MCU内部如何产生AD触发信号及相关信号的波形。Monaco的EQADC集成了一个并行接口(PSI),爆震数字信号可以通过PSI直接输送到片上的硬件数字滤波器(Decimation Filter)。使用PSI的一个显著好处是:在滤波过程中不需要CPU的干预。

5 硬件数字滤波器

硬件数字滤波器的核心是硬件乘加器(MAC)。缺省输入样点的精度为16位。通过软件可以将硬件数字滤波器设置成8阶的有限冲击相应滤波器(8th FIR)或4阶的无限冲击滤波器(4th IIR)。硬件数字滤波器有9个24位的系数寄存器,分别存放8个滤波器系数和1个常数项。MAC单元的累加结果精度达51位。在本例中我们将Decimation Filter设计为一个4th IIR低通滤波器,截止频率为16kHz。硬件数字滤波器还支持对滤波后的信号亚采样,亚采样率从2:1到16:1。目的是降低后续CPU处理的负荷。在本例中选择4:1,截止频率为16kHz的信号用50k的样点率就足够了,不需要高到200k。

MCU 飞思卡尔 555 传感器 滤波器 ADC 电阻 放大器 低通滤波器 DSP 相关文章:

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于nRF2401智能小区无线抄表系统集中器设计(04-30)

- 新型锁相环芯片全面提升红外无线麦克风产品性能(05-04)

- 基于nRF2401智能无线火灾监控系统设计(04-01)

- 安森美90W太阳能LED街灯高能效解决方案(05-18)

- 武器系统中的微处理器(06-04)