一种3dB带状线耦合电桥的研究与设计

1 引言

随着现代无线通信系统的发展,无源器件以其环保无污染、低功耗和高可靠性的优点而被广泛使用。3 dB电桥在无源系统中是十分常见的器件。常用于信号的合路、分路及功率合成,近来随着POI(多系统合路平台)市场的不断扩大,对其性能提出了更高的要求。众所周知带状线电桥具有插入损耗低、方向性好等优点,但是在实现宽带3 dB电桥中会发现结构形式难以达到体积小、结构紧凑等要求,这将不利于与其他有源或无源电路的连接或集成。针对这一问题,本文提出了一种新型结构的3 dB电桥设计方案,这种电桥比一般的电桥带宽更宽,可达到4GHz,可以承受比较大的功率容量,而且体积小,使用新式结构可以实现低插损、高方向性和宽频带的要求,并且具有易于生产、调试等优点。

2 耦合器的原理

电桥是一种分路元件,属于四端口网络,在电路中起着功率分配及改变信号相位的作用。通常,由一个单独的耦合器来实现电桥的功能。

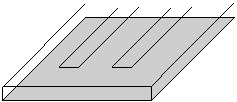

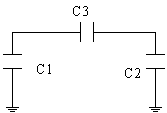

耦合先的电特性完全可以由线之间的等效电容和波在线上的传播速度来表示。下面图1给出了两个微带导体之间耦合关系,其中C1、C2表示微带线与地面之间的电容,C3为两个微带之间的电容。C1、C2、得大小由微带线与地面之间的距离觉得的,C3的大小是两微带线之间的间隙以及微带宽度决定的。

图1 微带线耦合及其等效电路

在分析耦合传输线时主要采用的是奇偶模法,由于线间同时存在的电耦合和磁耦合,可以分别研究奇模线和偶模线的特性,然后叠加便可以得到耦合线特性。这样可以将耦合线四端口网络简化成二端口网络。

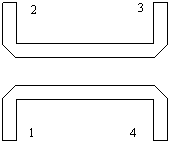

图2 耦合线端口激励示意图

如图3-7所示,对称耦合微带结构的端口激励示意图,其中端口1和端口2的激励V1和V2可以用一对奇偶模激励电压Vo和Ve的组成来进行分解。

由上式可以得到:

一般条件情况下可以选择奇偶模的大小,实现不同的耦合。我们在实际设计中常将端口一设为激励端口。4端口为直通端,3端口为隔离端,2端口为耦合端口。理想条件下V2=0,奇模偶模相等均为V1/2。得到耦合器及其等效电路如下图所示。

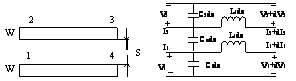

图3 耦合线及等效电路图

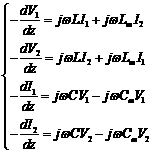

图中Lm和Cm表示单位长度的耦合电感和耦合电容,L1和C1表示第二条微带的作用分布电容和电感。在时谐变化的电压电流工作下我们可以得到:

上式是耦合传输线的基本方程,其中L1=L为耦合单元长度的总电感,C1+Cm=C为总电容。

3 耦合器的设计

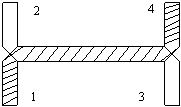

单个λ/4带状线耦合器。如下图4说是信号由1口输入时,2口为隔离端口,3口为耦合端口,4口为直通端口。这种结构由于直通端和耦合输出端在同一个方向,方便连接和实现级联。在带状线耦合器设计中已经得到广泛的采用。

图4 单个λ/4带状线耦合器

采用该方法一共需要用三块材料相同的介质基片和两层金属微带线。分别将它们按照一定的结构叠起来。从下往上依次是:下接地板、介质层、金属微带层、介质层、金属微带层、介质层和上接地板。在实际设计中我们可以通过调节λ/4带状线重叠部分的大小来调节耦合度。

本次设计的指标如下

| 频率 | 10GHz±1GHz |

| 驻波 | ≤1.5 |

| 隔离 | ≥20dB |

| 插入损耗 | ≤1dB |

| 带内幅度起伏 | ≤0.5dB |

| 相位起伏 | ≤5° |

| 介质板 | Rogers 5880 h=0.254mm |

| 接口形式 | SMA |

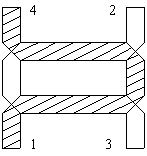

通过HFSS电磁仿真软件对耦合器进行仿真,由于单个λ/4带状线耦合器在两条微带线完全重叠实现最大耦合度的条件下很难实现3dB的要求。为了完成上述设计指标选择采用两个λ/4耦合线宽边耦合器级联来实现该电桥,如图3所示。

图5 级联耦合器

4 仿真及结果

综上所述,本设计在设计中考虑微带线结构的耦合性较差,且封装时需要占用空间大等原因。故而采用了带状线结构,如下图6所示为HFSS仿真模型图,由于为了实现3dB电桥耦合度的要求,采用了级联的结构。仿真过程中研究了介质板厚度对耦合度的影响。上下底面的厚度越厚耦合度变好,中间层越厚耦合度越小,隔离性变好。为了方便加工将上下底面的介质板厚度设为相同。厚度为0.254mm,中间隔离介质层厚度也为0.25

- 检测无源 RFID 电子标签谐振频率的耦合器之关键技术研究(11-01)

- 基于LOC11X线性光耦合器的隔离放大器(08-05)

- 710 MHz LTE天线的去耦合分析(07-18)

- 提高RFID系统中耦合器定向性设计(10-16)

- 微带滤波器与耦合器电路的设计,制作与测量(07-12)

- 基于小型化微带双分支定向耦合器的设计方案(10-26)