基于射频功率放大器驱动器的无线系统设计

动器的输出级(EDMOS)合并。

为确保输出级之前的两个RF路径的布局对称,所有逆变器(从M0到M3)都采用了统一的PMOS-to-NMOS晶体管尺寸比。所有CMOS级中每个加宽晶体管(M0级的总宽度可达4,032μm)的布局被分割成若干个单位晶体管布局参数化单元(P-cell),并通过优化实现最高频率。每个P-cell都包含一个版图不对称的多指晶体管(具有最小栅长)、护圈和所有与顶层内部金属的互连。每个晶体管的布局均可充分扩展。

此外,该驱动器还包含大尺寸的片上交流耦合和交流退耦平行板交指型金属边电容器。电容器Cin与两个DC输入偏压线路(BIASa,b)一起实现直流电平位移。使用片上电容器Cout可实现DC耦合或AC耦合两种方式的输出。AC耦合可驱动需要负栅偏压的功率晶体管(如GaN)。将四条宽粗的电源线(VSS0,1和VDD0,1)布线于位于两块更厚的金属顶部上的芯片内。采用电容器C0、C1、C2和C3对内部电源线进行退耦。此外还增加了专用的ESD保护电路以保护CMOS芯片。

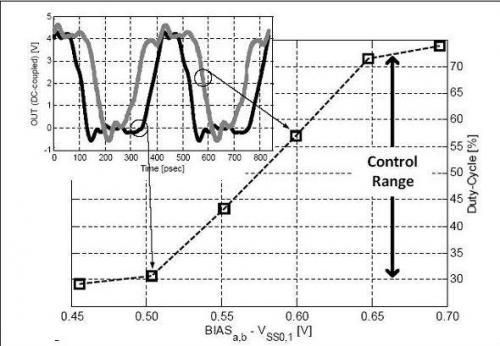

CMOS驱动器的总体芯片面积为1.99mm2,而工作面积(EDMOS和缓冲器)仅为0.16mm2.将原型裸片安装于PCB上以便于测试,并在50Ω的负载环境下进行测量。使用高速数字采样示波器可捕捉时域信号。图2显示了在3V、5V、7V和9V的供电电压下,且输入正弦波为2.1GHz时,驱动器DC耦合输出的时域波形。在50Ω负载和9V电源下所测量的最大摆幅为8.04Vpp.测量到的驱动器导通电阻低至4.6Ω。图3显示了测量到的脉冲宽度(以占空比表示)控制范围,以DC偏置电平(即BIASa,b-VSS0,1)的函数表示。该图还显示了不同占空比条件下的两种时域波形。在2.4GHz频率和5V电源下可观察到占空比控制范围为30.7%至71.5%.在高达3.6GHz的频率下,RF驱动器将其脉冲波形保持为8Vpp.在2.4GHz下进行的另一项测量表明,在5V和9V电源下连续工作24小时后,性能并未发生下降。

图2:2.1GHz时,多种电压下监测到的时域波形(VDD1- VSS0= 3V, 5V, 7V, 9V)。

图3:2.4GHz时测量到的占空比。

与之前最先进的CMOS器件相比,上述驱动器实现了更大的输出电压摆幅和更高的工作频率。此外,该CMOS驱动器具有与SiGe-BiCMOS等效电路相近的性能。相比之前所有HV驱动器,本文介绍的芯片具有带RF控制功能的附加脉冲以提升SMPA系统性能。

本文小结

本文主要描述了采用1.2V基线65nm CMOS技术实现8.04Vpp和3.6GHz工作频率的首款宽带PWM控制RF SMPA驱动器。该CMOS驱动器连接了数字CMOS电路与高功率晶体管,可充当面向无线基础设施系统的下一代可重新配置多频多模发射器的主要构建模块。

射频功率放大器驱动器 无线系统 CMOS驱动器 相关文章:

- 无线系统设计的关键步骤(11-12)

- 安捷伦和Lime Microsystems合作开发先进无线系统测量(11-15)

- RFS新型室内用全向吸顶天线提供端到端分布式无线系统解决方案(06-02)

- 基于射频功率放大器驱动器的无线系统实现(01-15)