如何灵活使用飞思卡尔i.MX应用处理器的GPIO

时间:08-01

来源:互联网

点击:

从事i.MX应用处理器的应用设计客户支持工作几年以来,经常会收到GPIO使用或者与其直接相关的问题。而且问题不仅仅来自于初次使用i.MX处理器的客户,也有很多是来自从事产品开发多年的工程师。由于i.MX应用处理器具有较高的复杂性,导致硬件设计和软件开发是由不同的人/团队来负责的,从而使一些软件硬件衔接部分成了一个类似于三不管的灰色地带。硬件设计者认为是软件去使用所以不太关心,而软件人员对硬件相关的知识基础弱,比较难于深入理解怎样使用。但其在设计中的重要性是不容忽视的,否则会导致很多潜在的问题。

通常GPIO会占到芯片超过一半的管脚数量,在此分享一些飞思卡尔i.MX应用处理器GPIO的功能点的使用经验,希望能帮助设计人员避免问题,优化设计,让设计成为一件快乐的事。

电平转换速度(slew rate)

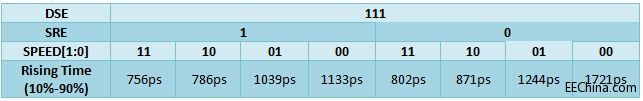

对于这个功能的详细描述一直没有出现在飞思卡尔官方发布的文档中,经应用团队的努力下,在最新的IMX6DQRM Rev2版已经加入。通过文档大家可以了解到电平转换速度依赖于三个寄存器(DSE,SRE和SPEED)的配置,电平转换速率的输出结果有四级。

顾名思义,这是一个可以调整高低电平切换上升和下降时间速度的设置项,在一般的应用中使用芯片默认的设置就可以了。在需要微调SI或EMI性能时可以尝试修改配置。

由于这个功能并没有设计成可以精确的控制转换时间,只是以四种不同源驱动工作频率的形式体现的(四种源驱动频率分别为50MHz,100MHz,150MHz和200MHz)。由此可知我们只能以一种对比趋势的定性方式使用它。下面使用飞思卡尔官方提供的IBIS模型结合Mentor Graphic公司的HyperLynx9.1仿真工具得到一组近似结果供大家参考。

仿真模型:GPIO单端输出 外加5pF负载

工作电压:1.8V

需要注意的是对于一些高速的工作模式,例如SD口的HS104工作模式,IO的电平转换速率是已经被设定死的,不能调节了。

应用举例:降低并行显示接口所有IO的电平转换速度对改善该接口带来的EMI性能有一定的效果。

状态保存器(Keeper)

飞思卡尔i.MX应用处理器的GPIO包含输入和输出两组状态保存器。

使能输入状态保存器可以在IO供电NVCC_xxx关掉之后,使输入缓冲器的输出自动维持在关电之前的逻辑状态。其价值可以在低功耗的应用中得到体现。

使能输出状态保存器可以在内核供电关掉之后,使IO的输出自动维持在关电之前的逻辑状态(需要注意的是输出状态保存器不能与上下拉同时工作)。其价值同样可以体现在低功耗的应用中。

应用举例:输入状态保存器可以允许IO的供电由外部输入逻辑来控制,不必担心状态由于外部输入逻辑关电丢失,当外部电路没有状态变化时可以关闭电源达到节电的目的。而输出状态保存器则可以允许内核关电,不必担心输出逻辑丢失。

开漏(open-drain)

开漏(OD)是针对场效应管而言的,类似于三极管的集电极开路(OC)。I2C总线就是OD门电路的典型应用。

飞思卡尔i.MX应用处理器的大部分GPIO都支持开漏模式,这使得设计上可以很灵活的实现线与逻辑以及不同电压域的输出控制。

应用举例:当需要使用GPIO来控制外设时,工作电平不匹配也能不是没有办法了,只要将GPIO设置为开漏模式,外面增加上拉电阻连接到受控电路逻辑电平即可,不必担心电平不匹配带来的漏电流或者电路损坏。(当然一定要注意,外部逻辑电平不能高于GPIO本身的最大耐压值)

上下拉(pull-up/pull-down)

上下拉就是指上下拉电阻,所有飞思卡尔i.MX应用处理器的GPIO都包含这个功能。需要指出的是上下来是一个相对独立的功能,不受限于输出或输入设置。也就是说当GPIO作为输入时可以使能上拉或者下拉,作为输出时也可以使能上拉或下拉。

当对上拉下电路的电流驱动能力要求不高时,片内的上下拉可以代替电路板上的上下拉设计,达到简化电路和降成本的目的。

应用举例:由于上下拉的独立性,在系统调试的时候外部控制芯片的程序可能还没有准备好,可以通过控制上下拉来对某些IO进行进行逻辑或功能测试。

附注:该功能提供的上下拉电阻的阻值误差较大,请根据数据手册和具体应用来权衡。

后记:

由于i.MX应用处理器包含众多系列,本文介绍的功能是基于目前最新的i.MX6系列,其它系列会有不同,但万变不离其中,设计时留意下就好。

通常GPIO会占到芯片超过一半的管脚数量,在此分享一些飞思卡尔i.MX应用处理器GPIO的功能点的使用经验,希望能帮助设计人员避免问题,优化设计,让设计成为一件快乐的事。

电平转换速度(slew rate)

对于这个功能的详细描述一直没有出现在飞思卡尔官方发布的文档中,经应用团队的努力下,在最新的IMX6DQRM Rev2版已经加入。通过文档大家可以了解到电平转换速度依赖于三个寄存器(DSE,SRE和SPEED)的配置,电平转换速率的输出结果有四级。

顾名思义,这是一个可以调整高低电平切换上升和下降时间速度的设置项,在一般的应用中使用芯片默认的设置就可以了。在需要微调SI或EMI性能时可以尝试修改配置。

由于这个功能并没有设计成可以精确的控制转换时间,只是以四种不同源驱动工作频率的形式体现的(四种源驱动频率分别为50MHz,100MHz,150MHz和200MHz)。由此可知我们只能以一种对比趋势的定性方式使用它。下面使用飞思卡尔官方提供的IBIS模型结合Mentor Graphic公司的HyperLynx9.1仿真工具得到一组近似结果供大家参考。

仿真模型:GPIO单端输出 外加5pF负载

工作电压:1.8V

需要注意的是对于一些高速的工作模式,例如SD口的HS104工作模式,IO的电平转换速率是已经被设定死的,不能调节了。

应用举例:降低并行显示接口所有IO的电平转换速度对改善该接口带来的EMI性能有一定的效果。

状态保存器(Keeper)

飞思卡尔i.MX应用处理器的GPIO包含输入和输出两组状态保存器。

使能输入状态保存器可以在IO供电NVCC_xxx关掉之后,使输入缓冲器的输出自动维持在关电之前的逻辑状态。其价值可以在低功耗的应用中得到体现。

使能输出状态保存器可以在内核供电关掉之后,使IO的输出自动维持在关电之前的逻辑状态(需要注意的是输出状态保存器不能与上下拉同时工作)。其价值同样可以体现在低功耗的应用中。

应用举例:输入状态保存器可以允许IO的供电由外部输入逻辑来控制,不必担心状态由于外部输入逻辑关电丢失,当外部电路没有状态变化时可以关闭电源达到节电的目的。而输出状态保存器则可以允许内核关电,不必担心输出逻辑丢失。

开漏(open-drain)

开漏(OD)是针对场效应管而言的,类似于三极管的集电极开路(OC)。I2C总线就是OD门电路的典型应用。

飞思卡尔i.MX应用处理器的大部分GPIO都支持开漏模式,这使得设计上可以很灵活的实现线与逻辑以及不同电压域的输出控制。

应用举例:当需要使用GPIO来控制外设时,工作电平不匹配也能不是没有办法了,只要将GPIO设置为开漏模式,外面增加上拉电阻连接到受控电路逻辑电平即可,不必担心电平不匹配带来的漏电流或者电路损坏。(当然一定要注意,外部逻辑电平不能高于GPIO本身的最大耐压值)

上下拉(pull-up/pull-down)

上下拉就是指上下拉电阻,所有飞思卡尔i.MX应用处理器的GPIO都包含这个功能。需要指出的是上下来是一个相对独立的功能,不受限于输出或输入设置。也就是说当GPIO作为输入时可以使能上拉或者下拉,作为输出时也可以使能上拉或下拉。

当对上拉下电路的电流驱动能力要求不高时,片内的上下拉可以代替电路板上的上下拉设计,达到简化电路和降成本的目的。

应用举例:由于上下拉的独立性,在系统调试的时候外部控制芯片的程序可能还没有准备好,可以通过控制上下拉来对某些IO进行进行逻辑或功能测试。

附注:该功能提供的上下拉电阻的阻值误差较大,请根据数据手册和具体应用来权衡。

后记:

由于i.MX应用处理器包含众多系列,本文介绍的功能是基于目前最新的i.MX6系列,其它系列会有不同,但万变不离其中,设计时留意下就好。

飞思卡尔 Mentor 仿真 电压 电路 场效应管 三极管 总线 电阻 电流 相关文章:

- 飞思卡尔用超低功率8位微控制器简化绿色嵌入式设计(01-09)

- 飞思卡尔利用基于优化微控制器技术的先进电表参考设计(09-11)

- 飞思卡尔 i.MX 处理器助力 Sharp 的 NetWalker(08-12)

- 艾默生与飞思卡尔携手开发面向小型板卡的Power Architecture技术(02-03)

- 飞思卡尔嵌入式硅片为福特汽车下一代SYNC系统提供动力(01-08)

- 飞思卡尔半导体使用Tektronix IConnect软件为发射机建模 (04-01)