超低功耗技术的先驱:TI 采用新型“金刚狼”MCU 平台可使 MCU 总功耗锐减 50%

时间:10-24

来源:互联网

点击:

作者:Jacob Borgeson,德州仪器(TI)MSP430 产品市场工程师,MSP430 产品市场工作组

引言

德州仪器 (TI) 于上世纪 70 年代推出了微控制器 (MCU),并已在众多的平台中运用了此项技术,包括超低功耗 MSP430™ MCU 产品系列。MSP430 MCU 十多年来一直是业界超低功耗技术的领先者,而且每一代新型架构皆专注于创造全新的功耗与效率指标记录。

MSP430 架构业已提供了仅在需要时才唤醒的智能外设、允许 MCU 内部的模块以不同频率运作的灵活定时、以及先进的电源管理技术等,这些只是其诸多创新成果中的几个而已。虽然贵为业界领袖,但 TI 并未因此沾沾自喜固步自封,而是一如既往地投入巨资不断地开发最先进的超低功耗技术。

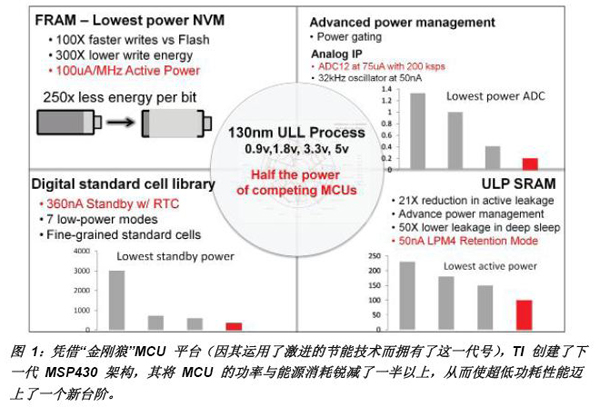

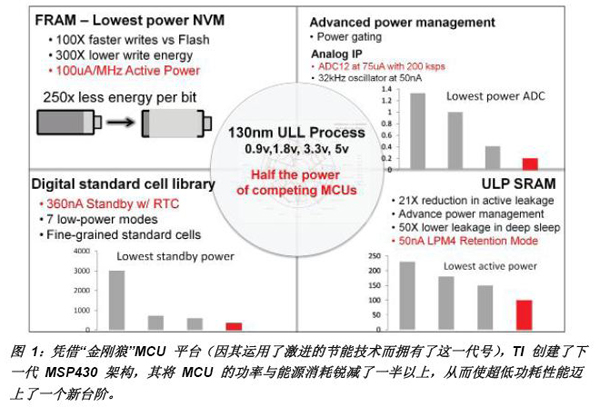

凭借“金刚狼 (Wolverine)”MCU 平台(因其运用了激进的节能技术而拥有了这一代号),TI 创立了下一代 MSP430 架构(见图 1)。这款新型平台将 MCU 的功率与能源消耗锐减了一半以上,从而使超低功耗性能迈上了一个新台阶。

* 据美国史密森研究所 (Smithsonian Institution) 提供的资料。

• 运行模式功耗低至 100μA/MHz

• 待机流耗低于 400 nA(RTC 和欠压保护模式)

• FRAM 每位能耗下降了 250 倍

• 可在不到 7μs 的时间里从待机模式唤醒至运行模式

TI“金刚狼”平台之所以实现了引人注目的功耗性能提升,凭借的是其新型 130 nm 超低漏电 (ULL) 工艺技术、集成型低功耗非易失性存储器以及利用先进的电源管理与高精度低功耗模拟组件得以增强的 MSP430 原生优势。

130 nm 超低漏电 (ULL) 工艺技术

鉴于超低功耗器件有 99.9% 的时间都处于待机模式,因此在较小的工艺几何尺寸下,漏电流便成为了决定功率效率的一个关键因素。低功耗设计的挑战源于晶体管漏电流的指数性增加(因栅极长度的不断缩减及栅极氧化物所致)。

漏电流基于电子在节点之间必须移动的距离,而随着这个距离的不断缩小,电子在节点之间的泄放越来越容易。以基于 25 nm 或 45 nm 工艺的 PC 用高性能微处理器 (MPU) 为例,其必须使用特殊的材料来控制漏电。对于 MCU,漏电流从 180 nm CMOS 工艺节点开始变成了一个重要的考虑因素。

通过其在 65 nm、45 nm 和 28 nm 工艺节点上设计的 GHz 智能手机处理器和数字信号处理器 (DSP),TI 对于较小工艺节点下的漏电流了如指掌,而且 TI 的工程师们把学到的有关这些较小工艺几何尺寸下的漏电流特性的知识,全部都应用到了“金刚狼”的 130 nm 工艺中。

历史上,MCU 设计人员往往将其创新的着重点放在提高性能和密度上。自 1965 年以来,摩尔定律 (Moore’s Law) 一直在推动着晶体管和芯片性能的提升。虽然这种改进的步伐在过去的 10 年间有所放缓,但工艺技术每 18 个月将性能提升一倍的历史,已经有 30 多年了。

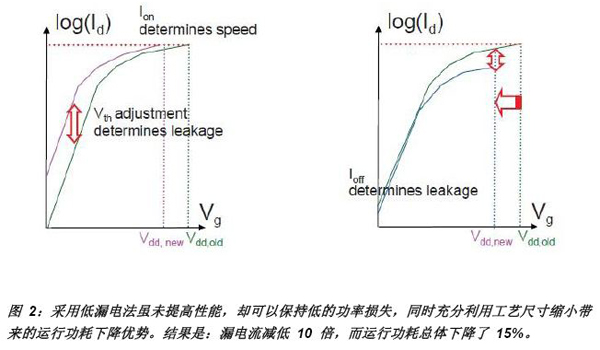

就 130 nm“金刚狼”平台而言,TI 通过专为提升功率效率而设计,并针对较低漏电流和其他硅工艺固有特性而优化的电路,恢复了摩尔定律在改善功耗(而非性能)指标方面的作用。尽管没有像采用传统方法时那样将性能提升一倍,但 TI 却代之以功耗的减半(也就是将功耗指标改善了一倍),同时保持了现今 MSP430 MCU 架构的高性能。

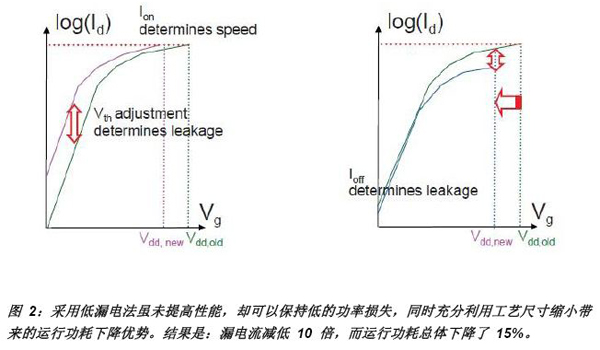

结果,与其他 130 nm CMOS 工艺相比,各个晶体管的最小漏电流将至少减低10 倍,而运行功耗则总体下降了 15%(图 2)。

超低功耗的基础

为了获得新型 130 nm 工艺技术的最大优势,TI 对其整个设计工具套件库进行了全面的重新设计,旨在将着重点集中在功率效率而非高性能上。这些工具套件(包括标准单元库、电容器、模拟组件和 I/O)基于基础级晶体管配置,其形成了用于设计当今复杂 MCU 的主要构件。

针对 130 nm 工艺的新型工具套件具有丰富的模拟组件,以实现诸如高精度模数转换器 (ADC) 等外设和用于大幅降低功耗的内部电源管理电路。例如:“金刚狼”模块产品组合包括一个每秒钟能完成 20 万次采样而流耗仅为 75μA 的高精度 12 位 ADC。同样,具有日历显示和报警功能的实时时钟 (RTC) 模块能够以仅仅 100 nA 的流耗运行。130 nm 的超低漏电工艺与丰富的混合信号集成相组合,有助实现业界最低的总系统功耗。

先进的电源管理

功率效率并非只适用于 CPU 的功耗。有功电流同样取决于系统执行定时的效率、高精度模拟外设和通信接口。如欲最大限度地降低各种不同工作负载条件下的功耗,运用先进的电源管理技术是必不可少的。

“金刚狼”架构提供了 MSP430 MCU 电源管理模块的一种增强型版本。除了支持 7 种操作模式之外,“金刚狼”电源管理模块还能提供先进的电源门控 (power gating),并采用了一个高响应性的自适应稳压器。在内部,MCU 被分割成了几个功率域,以使系统能够根据应用的特殊需求动态地管理器件的每个部分。

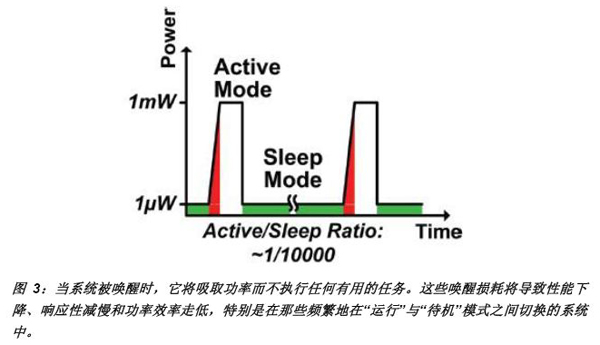

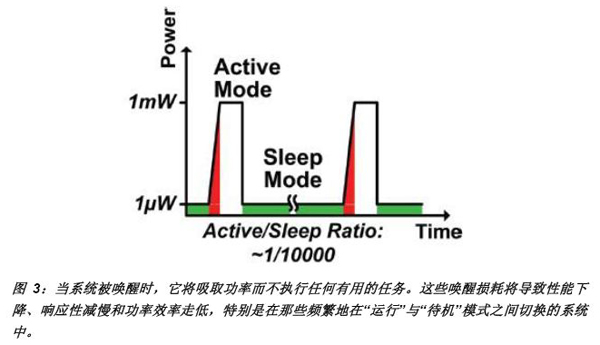

当使系统在尽可能长的时间里处于待机模式时,就最大限度地降低了总体系统功耗。然而,系统每次在待机模式与运行模式之间切换都会产生功耗。特别地,供应给电路的电压不但达到预期电平而且重新预置子系统或外设,以再度变至运作状态,都需要时间。在这段时间里,电路吸取的功率日益增大,却并未完成任何有用的工作(见图 3)。这些唤醒损耗将导致性能下降、响应性减慢和功率效率走低,特别是在那些频繁地在“运行”与“待机”模式之间切换的系统中。

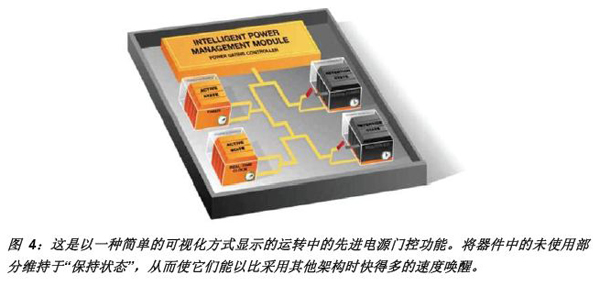

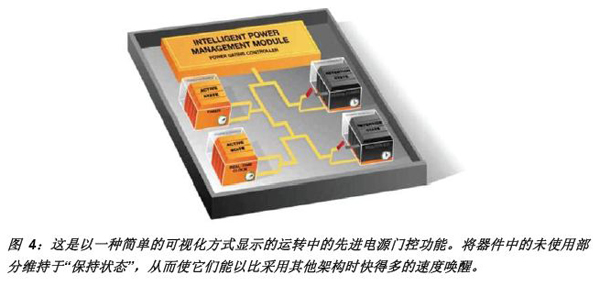

为了降低唤醒损耗,“金刚狼”采取了一种不同的方法。传统上,在不用的时候整个模块或外设都会被关断。通过采用电源门控控制器,使更多的模块或外设以一种“保持”模式运行,“金刚狼”改善了功率效率。在该模式中,对那些处于运行状态并请求时钟的模块保持全面供电。而对于那些处于空闲和未用状态的模块则施以“保持水平”的供电。这意味着将只对专门用于保持模块状态的逻辑电路供电。

电源门控可以在不牺牲性能的情况下实现显著的节能。设想一个在待机模式中处于使用状态的定时器。当此定时器主动请求一个时钟时,电源门控控制器检测到该请求并把定时器保持于一种全面运行的状态。然而,一旦定时器功能完成,则将其供电降至“保持水平”,同时维持配置状态以尽可能地降低功耗。当再次需要定时器时即可快速提供,从而最大限度地减少唤醒损耗。电源门控对于开发人员是透明的,可使他们充分利用业界领先的功率效率,而无须对每个模块或外设进行手动控制(见图 4)。

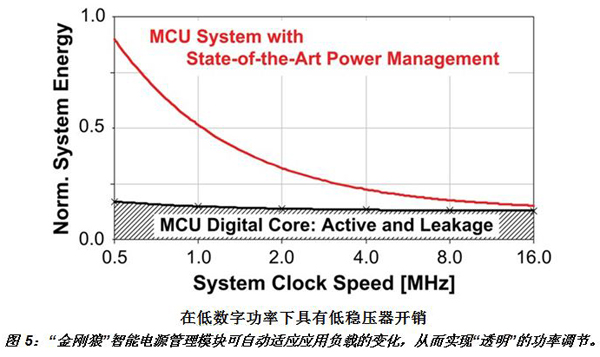

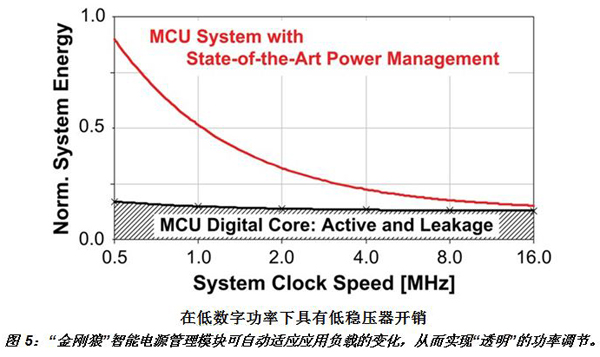

超低功耗 MCU需要具备的另一项重要功能是拥有对变化的应用负载做出快速响应的能力。利用可在不需要主 CPU 完整性能的情况下降低其供电功率的技术,即可实现大幅节能。然而,“金刚狼”平台中的智能电源模块可自动适应应用负载的变化(比如:当一个高频模块上电时),而不需要开发人员以手动的方式调节该功率(见下页上的图 5)。

操作速度根据以下条件进行调节:

• 应用要求

• 最大可用功率

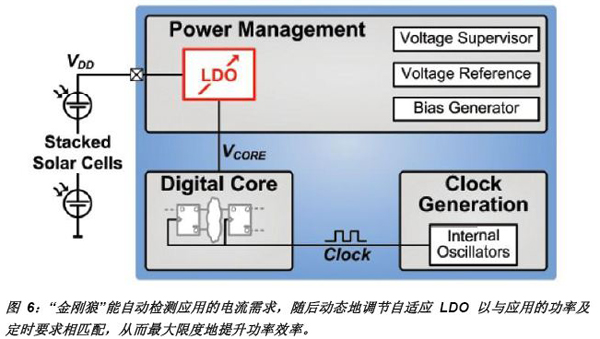

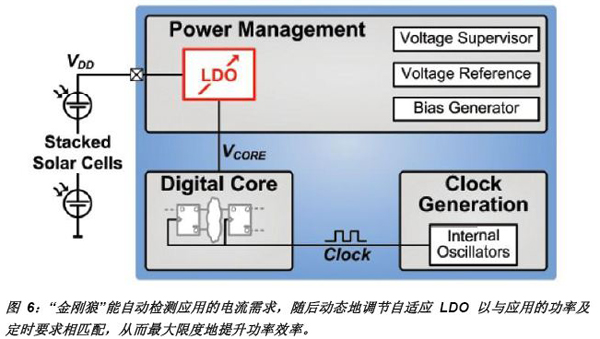

具体而言,负责为 MCU 的数字内核供电的自适应低压降稳压器 (LDO) 可根据需要增加其负载,从而对变化的功率要求做出响应。事实上,“金刚狼”能自动检测应用的电流需求并根据需要提供时钟与功率。

凭借很高的精细度,该 LDO 能够与各种各样的应用负载相匹配。另外,这种方法还免除了增设诸如缓冲电容器(其在从低负载电流切换至高负载电流时使用)等外部组件的需要。与电源门控一样,该节能技术同样以一种对开发人员“无缝且透明”的方式实现了电源管理的自动化。

引言

德州仪器 (TI) 于上世纪 70 年代推出了微控制器 (MCU),并已在众多的平台中运用了此项技术,包括超低功耗 MSP430™ MCU 产品系列。MSP430 MCU 十多年来一直是业界超低功耗技术的领先者,而且每一代新型架构皆专注于创造全新的功耗与效率指标记录。

MSP430 架构业已提供了仅在需要时才唤醒的智能外设、允许 MCU 内部的模块以不同频率运作的灵活定时、以及先进的电源管理技术等,这些只是其诸多创新成果中的几个而已。虽然贵为业界领袖,但 TI 并未因此沾沾自喜固步自封,而是一如既往地投入巨资不断地开发最先进的超低功耗技术。

凭借“金刚狼 (Wolverine)”MCU 平台(因其运用了激进的节能技术而拥有了这一代号),TI 创立了下一代 MSP430 架构(见图 1)。这款新型平台将 MCU 的功率与能源消耗锐减了一半以上,从而使超低功耗性能迈上了一个新台阶。

* 据美国史密森研究所 (Smithsonian Institution) 提供的资料。

• 运行模式功耗低至 100μA/MHz

• 待机流耗低于 400 nA(RTC 和欠压保护模式)

• FRAM 每位能耗下降了 250 倍

• 可在不到 7μs 的时间里从待机模式唤醒至运行模式

TI“金刚狼”平台之所以实现了引人注目的功耗性能提升,凭借的是其新型 130 nm 超低漏电 (ULL) 工艺技术、集成型低功耗非易失性存储器以及利用先进的电源管理与高精度低功耗模拟组件得以增强的 MSP430 原生优势。

130 nm 超低漏电 (ULL) 工艺技术

鉴于超低功耗器件有 99.9% 的时间都处于待机模式,因此在较小的工艺几何尺寸下,漏电流便成为了决定功率效率的一个关键因素。低功耗设计的挑战源于晶体管漏电流的指数性增加(因栅极长度的不断缩减及栅极氧化物所致)。

漏电流基于电子在节点之间必须移动的距离,而随着这个距离的不断缩小,电子在节点之间的泄放越来越容易。以基于 25 nm 或 45 nm 工艺的 PC 用高性能微处理器 (MPU) 为例,其必须使用特殊的材料来控制漏电。对于 MCU,漏电流从 180 nm CMOS 工艺节点开始变成了一个重要的考虑因素。

通过其在 65 nm、45 nm 和 28 nm 工艺节点上设计的 GHz 智能手机处理器和数字信号处理器 (DSP),TI 对于较小工艺节点下的漏电流了如指掌,而且 TI 的工程师们把学到的有关这些较小工艺几何尺寸下的漏电流特性的知识,全部都应用到了“金刚狼”的 130 nm 工艺中。

历史上,MCU 设计人员往往将其创新的着重点放在提高性能和密度上。自 1965 年以来,摩尔定律 (Moore’s Law) 一直在推动着晶体管和芯片性能的提升。虽然这种改进的步伐在过去的 10 年间有所放缓,但工艺技术每 18 个月将性能提升一倍的历史,已经有 30 多年了。

就 130 nm“金刚狼”平台而言,TI 通过专为提升功率效率而设计,并针对较低漏电流和其他硅工艺固有特性而优化的电路,恢复了摩尔定律在改善功耗(而非性能)指标方面的作用。尽管没有像采用传统方法时那样将性能提升一倍,但 TI 却代之以功耗的减半(也就是将功耗指标改善了一倍),同时保持了现今 MSP430 MCU 架构的高性能。

结果,与其他 130 nm CMOS 工艺相比,各个晶体管的最小漏电流将至少减低10 倍,而运行功耗则总体下降了 15%(图 2)。

超低功耗的基础

为了获得新型 130 nm 工艺技术的最大优势,TI 对其整个设计工具套件库进行了全面的重新设计,旨在将着重点集中在功率效率而非高性能上。这些工具套件(包括标准单元库、电容器、模拟组件和 I/O)基于基础级晶体管配置,其形成了用于设计当今复杂 MCU 的主要构件。

针对 130 nm 工艺的新型工具套件具有丰富的模拟组件,以实现诸如高精度模数转换器 (ADC) 等外设和用于大幅降低功耗的内部电源管理电路。例如:“金刚狼”模块产品组合包括一个每秒钟能完成 20 万次采样而流耗仅为 75μA 的高精度 12 位 ADC。同样,具有日历显示和报警功能的实时时钟 (RTC) 模块能够以仅仅 100 nA 的流耗运行。130 nm 的超低漏电工艺与丰富的混合信号集成相组合,有助实现业界最低的总系统功耗。

先进的电源管理

功率效率并非只适用于 CPU 的功耗。有功电流同样取决于系统执行定时的效率、高精度模拟外设和通信接口。如欲最大限度地降低各种不同工作负载条件下的功耗,运用先进的电源管理技术是必不可少的。

“金刚狼”架构提供了 MSP430 MCU 电源管理模块的一种增强型版本。除了支持 7 种操作模式之外,“金刚狼”电源管理模块还能提供先进的电源门控 (power gating),并采用了一个高响应性的自适应稳压器。在内部,MCU 被分割成了几个功率域,以使系统能够根据应用的特殊需求动态地管理器件的每个部分。

当使系统在尽可能长的时间里处于待机模式时,就最大限度地降低了总体系统功耗。然而,系统每次在待机模式与运行模式之间切换都会产生功耗。特别地,供应给电路的电压不但达到预期电平而且重新预置子系统或外设,以再度变至运作状态,都需要时间。在这段时间里,电路吸取的功率日益增大,却并未完成任何有用的工作(见图 3)。这些唤醒损耗将导致性能下降、响应性减慢和功率效率走低,特别是在那些频繁地在“运行”与“待机”模式之间切换的系统中。

为了降低唤醒损耗,“金刚狼”采取了一种不同的方法。传统上,在不用的时候整个模块或外设都会被关断。通过采用电源门控控制器,使更多的模块或外设以一种“保持”模式运行,“金刚狼”改善了功率效率。在该模式中,对那些处于运行状态并请求时钟的模块保持全面供电。而对于那些处于空闲和未用状态的模块则施以“保持水平”的供电。这意味着将只对专门用于保持模块状态的逻辑电路供电。

电源门控可以在不牺牲性能的情况下实现显著的节能。设想一个在待机模式中处于使用状态的定时器。当此定时器主动请求一个时钟时,电源门控控制器检测到该请求并把定时器保持于一种全面运行的状态。然而,一旦定时器功能完成,则将其供电降至“保持水平”,同时维持配置状态以尽可能地降低功耗。当再次需要定时器时即可快速提供,从而最大限度地减少唤醒损耗。电源门控对于开发人员是透明的,可使他们充分利用业界领先的功率效率,而无须对每个模块或外设进行手动控制(见图 4)。

超低功耗 MCU需要具备的另一项重要功能是拥有对变化的应用负载做出快速响应的能力。利用可在不需要主 CPU 完整性能的情况下降低其供电功率的技术,即可实现大幅节能。然而,“金刚狼”平台中的智能电源模块可自动适应应用负载的变化(比如:当一个高频模块上电时),而不需要开发人员以手动的方式调节该功率(见下页上的图 5)。

操作速度根据以下条件进行调节:

• 应用要求

• 最大可用功率

具体而言,负责为 MCU 的数字内核供电的自适应低压降稳压器 (LDO) 可根据需要增加其负载,从而对变化的功率要求做出响应。事实上,“金刚狼”能自动检测应用的电流需求并根据需要提供时钟与功率。

凭借很高的精细度,该 LDO 能够与各种各样的应用负载相匹配。另外,这种方法还免除了增设诸如缓冲电容器(其在从低负载电流切换至高负载电流时使用)等外部组件的需要。与电源门控一样,该节能技术同样以一种对开发人员“无缝且透明”的方式实现了电源管理的自动化。

德州仪器 MSP430 MCU 电源管理 电流 电子 CMOS DSP 电路 电容 ADC 电压 电源模块 LDO 电容器 自动化 嵌入式 GPS 相关文章:

- 德州仪器推出业界最广共模范围的70V 故障保护型 RS-485 收发器产品系列(11-04)

- 使用 TI KeyStone SoC 实现多标准无线基站(07-04)

- TI KeyStone 架构支持 L2 及传输处理(07-16)

- TMS320TCI6612/14 助力小型蜂窝基站实现高性能(08-15)

- 支持新一代工业检查系统的多核DSP(07-08)

- 多核DSP,军事应用的关键(08-12)