使用FPGA解决DSP设计难题

时间:10-08

来源:互联网

点击:

作者: Hardent公司Reg Zatrepalek

由于DSP能够迅速测量、过滤或压缩实时模拟信号,因此DSP在电子系统设计中非常重要。这样,DSP有助于实现数字世界与真实(模拟)世界的通信。但是随着电子系统变得越来越精细,需要处理多个模拟信号源,工程师们不得不作出艰难的决策。是使用多个DSP并使其功能与系统的其余部分同步,还是使用一个能够实现多个功能的带精细软件的高性能DSP更具优势?

由于现在的系统很复杂,在许多情况下,单DSP的实现方案的往往没有足够的处理能力。同时,系统架构也不能满足多芯片系统的成本、复杂性和功耗要求。

FPGA现已成为需要高性能DSP功能的系统的绝佳选择。事实上,与独立的数字信号处理器相比,FPGA技术一般可以为DSP难题提供更加简单的解决方案。要了解其中的原因,需要回顾一下DSP的起源和发展过程。

专用微处理器

在过去的二十多年里,传统的DSP架构一直在竭力跟上日益增长的性能要求的步伐。随着视频系统大踏步地迈进高清和3D时代,并且通信系统为实现更高带宽已经将现有技术发挥到极致,设计师们需要可替代的实现策略。用于实现数字信号处理算法的硬件不外乎以下三种基本器件之一:微处理器、逻辑电路和存储器。有些设计可能还需要额外硬件来实现模数转换(A/D)、数模转换(D/A)以及高速数字接口。

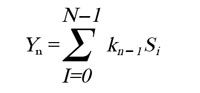

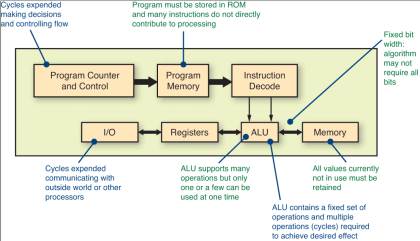

传统的数字信号处理器是设计用于实现专门目的的微处理器。这类处理器非常适合用于处理算法密集型任务,但是性能却受到时钟速率及其内部设计顺序性的限制。这限制了它们对输入数据采样每秒最多执行的运算次数。一般来讲,每执行一次算术逻辑单元(ALU)运算需要三或四个时钟周期。多核架构可以提高性能,但是提升幅度有限。因此,采用传统信号处理器的设计必须重复利用架构单元来实现算法。对于每次执行的加、减、乘或其他任何基本运算,不论是内部还是外部反馈,每次执行都必须循环通过ALU。

遗憾的是,在处理当今众多的高性能应用时,典型的DSP难以满足系统要求。过去已经提出过多种解决方案,包括在一个器件中使用多个ALU或者在一块板上使用多个DSP器件;不过这类方案往往会大大增加成本,并且只会将问题转移到另外一个领域。比如,用多个器件提高性能遵循指数曲线。要使性能提高一倍,需要用两个器件,若要再提高一倍,则需要用四个器件,依此类推。此外,程序员关注的重点往往会从信号处理功能转移到多个处理器和内核之间的任务调度上。这会产生大量的附加代码,而且这些代码会成为系统开销,而不是用于解决眼前的数字信号处理问题。

FPGA 技术的引进为解决DSP方案与日俱增的复杂性带来了福音。FPGA最初开发的目的是为了整合和集中分立的存储器和逻辑电路,以实现更高的集成度、更出色的性能和更高的灵活性。FPGA技术现已成为目前使用的几乎所有高性能系统的一个重要组成部分。相比传统DSP,FPGA是由可配置逻辑阵列(CLB)、存储器、DSP逻辑片(Slice)和一些其他元件组成的统一阵列构成的巨大并行结构。它们可以使用VHDL和Verilog等高级描述语言进行编程,或者在框图中使用系统生成器进行编程。FPGA还提供许多专用功能和IP核,用来以高度优化的方式直接完成实现方案。

FPGA内的数字信号处理器的主要优势是能够定制满足系统要求的方案。这意味着在多通道或高速系统中,用户可以充分利用器件内部的并行性,从而最大限度地提高性能,而对于低速系统,则可以更多地采用串行方式完成设计。因此,设计人员可以定制满足算法和系统要求的方案,而不是取期望的理想设计的折衷方案来迎合纯顺序器件的诸多局限。另外,超高速I/O通过最大限度地提高从捕捉经处理链再到最终输出的数据流,可进一步降低成本并减少瓶颈问题。

下面以一个同时使用传统DSP架构和FPGA架构的FIR滤波器实现方案为例,来说明每种解决方案的优劣。

数字FIR滤波器实例

有限脉冲响应(FIR)滤波器是一种使用最广的数字信号处理元件。设计人员使用滤波器来改变数字信号的幅度或频谱,通常用于隔离或突出样本数据频谱中的特定区域。从这个角度来讲,可以把滤波器视为信号的预处理方式。在典型的滤波器应用中,输入数据样本通过小心同步的数学运算与滤波器系数相结合(这取决于滤波器的类型和实现策略),随后数据样本进入下一个处理阶段。如果数据源和目的地都是模拟信号,则数据样本必须首先通过A/D转换器,而结果则必须馈送给D/A转换器。

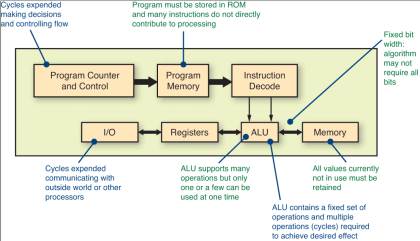

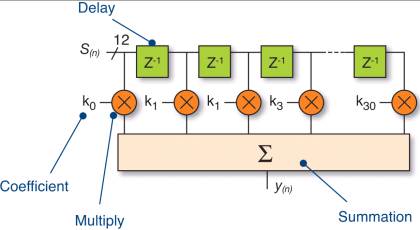

最简单的FIR滤波器是通过用一系列的延迟元件、乘法器和加法器树或加法器链来实现的。

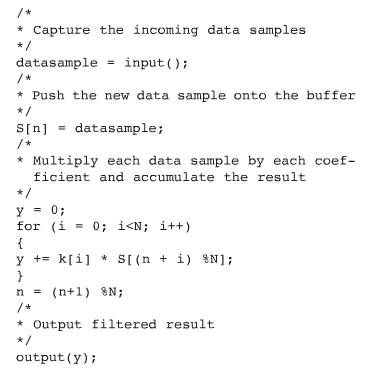

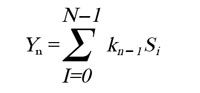

下面的等式是单通道FIR滤波器的数学表达式:

公式1

该等式中的各项分别表示输入样本、输出样本和系数。假设S为连续的输入样本流,Y为经滤波后产生的输出样本流,那么n和k则对应特定的瞬时时间。这样,若要计算时间n时的输出样本Y(n),则需要一组在N个不同时间点的样本,即:S(n)、S(n-1)、s(n-2)、…s(n-N+1)。将这组N个输入样本乘以N个系数并求和,便可得出最终结果Y。

图2是一个简单的31抽头FIR滤波器(长度N=31)的框图。

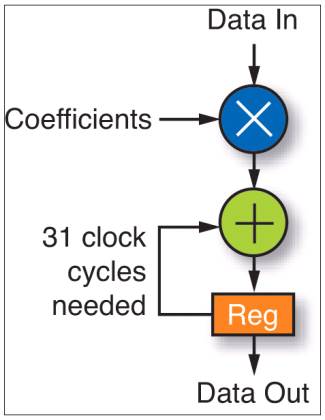

图1:传统的DSP架构

图2:长度为31抽头的FIR滤波器

在选择滤波器的理想长度和系数值时,有多种设计工具可供使用。其目的是通过选择适当的参数来实现所需的滤波器性能。参数选择最常用的设计工具是MATLAB。一旦选定了滤波器参数,就可以用数学等式实现。

实现FIR滤波器的基本步骤包括:

1. 对输入数据流采样;

2. 在缓冲区组织输入样本,以便让每个捕捉到的样本与每项滤波器系数相乘;

3. 让每个数据样本与每项系数相乘,并累加结果;

4. 输出滤波结果。

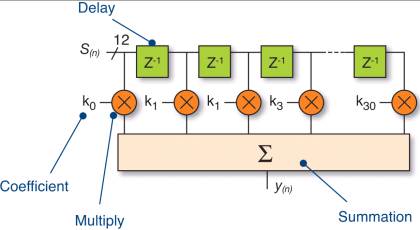

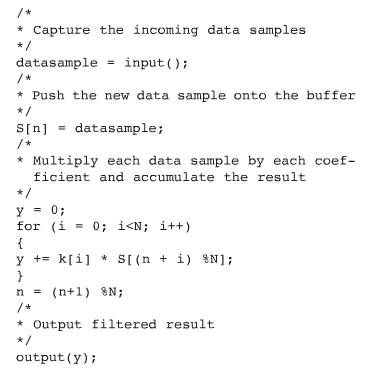

使用“相乘累加法”在处理器上实现FIR滤波器的典型C语言程序,如下列代码所示。

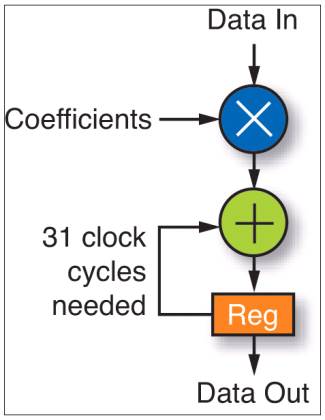

图3所示的实现方案被称为相乘累加或MAC型实现方案。这基本上就是用传统的DSP处理器实现滤波器的方法。采用内核时钟速率为1.2GHz的典型DSP处理器并以这种方式实现的31抽头FIR滤波器的最高性能约为9.68MHz,或最大的输入数据率为968MS/s。

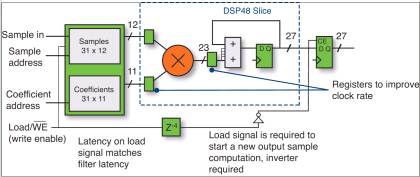

图3:传统DSP中的MAC实现方案

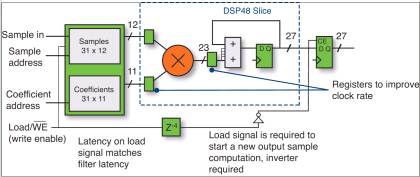

而FPGA提供了许多不同的实现和优化选择。如果需要高资源效率的实现,MAC引擎法则相当不错。还是以31抽头滤波器为例来说明滤波器规范对所需逻辑资源的影响,这种实现方案的框图如图4所示。

图4:FPGA中的MAC引擎FIR滤波器

这种设计需要存储器存储数据和系数,可以混合采用FPGA内部的RAM和ROM。RAM用于存储数据样本,故而采用循环的RAM缓冲器实现。字的数量与滤波器抽头数相等,位宽按样本大小设置。ROM用于存储系数。在最差情况下,字的数量与滤波器抽头的数量相等,但如果存在对称,则可以减少字的数量。位宽必须足以支持最大的系数。因为数据样本和系数数据都随每个周期改变,所以需要全乘法器。累加器负责将产生的结果累加起来。因为随着滤波器采集数据,累加器的输出会随每个时钟周期改变,所以需要捕捉寄存器。当全套N个样本完成累加后,输出寄存器负责捕捉最终结果。

如果采用MAC模式,DSP48则非常适合,因为DSP48Slice内含输入寄存器、输出寄存器和加法器单元。实现31抽头MAC引擎需要的资源包括一个DSP48、一个18kb块RAM和9个逻辑片。另外,还需要一些逻辑片用于采样、系数地址生成和控制。如果FPGA内置有600MHz的时钟,则在一个-3速度等级的Xilinx7系列器件中,该滤波器能够以19.35MHz或1,935MSps的输入采样速率运行。

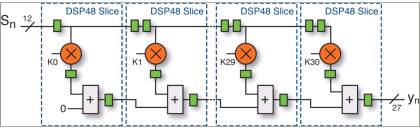

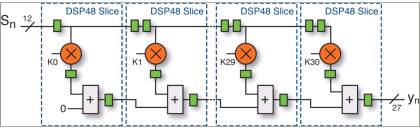

如果系统规范需要更高性能的FIR滤波器,则可采用并行结构来实现。图5显示了直接I型实现方案的框图。

图5:FPGA中的直接I型滤波器

直接I型滤波器结构能够在FPGA中实现最高性能。这种结构(通常也被称作脉动FIR滤波器)采用流水线和加法器链,使DSP48 Slice发挥出最高性能。输入馈送到用作数据样本缓冲器的级联寄存器;每个寄存器向DSP48提供一个样本,然后乘以对应的系数;加法器链存储部分乘积,然后依次相加,从而得到最终结果。

这种设计无需外部逻辑电路支持滤波器,并且该结构可扩展用于支持任意数量的系数。因为没有高扇出的输入信号,所以这种结构能够实现最高性能。实现31抽头FIR滤波器仅需要31个DSP48逻辑片。如果FPGA内置有600MHz的时钟,则在一个-3速度等级的Xilinx7系列器件中,该滤波器能够以600MHz或600MSps的输入采样速率运行。

从这个实例可以清晰地看出,FPGA不仅在性能上显著超越了传统的数字信号处理器,而且要求的时钟速率也显著降低(因此,功耗也显著降低)。

这个实例只反映了采用PFGA实现FIR滤波器的两种技术。为了充分利用数据采样率规范,可对该器件进行进一步定制,此时,数据采样率可在连续MAC运算极值和全并行运算极值之间。您还可考虑在包括对称系数、插值、抽取、多通道或多速率的资源利用与性能之间进行更多的权衡取舍。Xilinx CORE Generator?或System Generator(系统发生器)实用工具可以帮助用户充分利用这些设计变量和技术。

由于DSP能够迅速测量、过滤或压缩实时模拟信号,因此DSP在电子系统设计中非常重要。这样,DSP有助于实现数字世界与真实(模拟)世界的通信。但是随着电子系统变得越来越精细,需要处理多个模拟信号源,工程师们不得不作出艰难的决策。是使用多个DSP并使其功能与系统的其余部分同步,还是使用一个能够实现多个功能的带精细软件的高性能DSP更具优势?

由于现在的系统很复杂,在许多情况下,单DSP的实现方案的往往没有足够的处理能力。同时,系统架构也不能满足多芯片系统的成本、复杂性和功耗要求。

FPGA现已成为需要高性能DSP功能的系统的绝佳选择。事实上,与独立的数字信号处理器相比,FPGA技术一般可以为DSP难题提供更加简单的解决方案。要了解其中的原因,需要回顾一下DSP的起源和发展过程。

专用微处理器

在过去的二十多年里,传统的DSP架构一直在竭力跟上日益增长的性能要求的步伐。随着视频系统大踏步地迈进高清和3D时代,并且通信系统为实现更高带宽已经将现有技术发挥到极致,设计师们需要可替代的实现策略。用于实现数字信号处理算法的硬件不外乎以下三种基本器件之一:微处理器、逻辑电路和存储器。有些设计可能还需要额外硬件来实现模数转换(A/D)、数模转换(D/A)以及高速数字接口。

传统的数字信号处理器是设计用于实现专门目的的微处理器。这类处理器非常适合用于处理算法密集型任务,但是性能却受到时钟速率及其内部设计顺序性的限制。这限制了它们对输入数据采样每秒最多执行的运算次数。一般来讲,每执行一次算术逻辑单元(ALU)运算需要三或四个时钟周期。多核架构可以提高性能,但是提升幅度有限。因此,采用传统信号处理器的设计必须重复利用架构单元来实现算法。对于每次执行的加、减、乘或其他任何基本运算,不论是内部还是外部反馈,每次执行都必须循环通过ALU。

遗憾的是,在处理当今众多的高性能应用时,典型的DSP难以满足系统要求。过去已经提出过多种解决方案,包括在一个器件中使用多个ALU或者在一块板上使用多个DSP器件;不过这类方案往往会大大增加成本,并且只会将问题转移到另外一个领域。比如,用多个器件提高性能遵循指数曲线。要使性能提高一倍,需要用两个器件,若要再提高一倍,则需要用四个器件,依此类推。此外,程序员关注的重点往往会从信号处理功能转移到多个处理器和内核之间的任务调度上。这会产生大量的附加代码,而且这些代码会成为系统开销,而不是用于解决眼前的数字信号处理问题。

FPGA 技术的引进为解决DSP方案与日俱增的复杂性带来了福音。FPGA最初开发的目的是为了整合和集中分立的存储器和逻辑电路,以实现更高的集成度、更出色的性能和更高的灵活性。FPGA技术现已成为目前使用的几乎所有高性能系统的一个重要组成部分。相比传统DSP,FPGA是由可配置逻辑阵列(CLB)、存储器、DSP逻辑片(Slice)和一些其他元件组成的统一阵列构成的巨大并行结构。它们可以使用VHDL和Verilog等高级描述语言进行编程,或者在框图中使用系统生成器进行编程。FPGA还提供许多专用功能和IP核,用来以高度优化的方式直接完成实现方案。

FPGA内的数字信号处理器的主要优势是能够定制满足系统要求的方案。这意味着在多通道或高速系统中,用户可以充分利用器件内部的并行性,从而最大限度地提高性能,而对于低速系统,则可以更多地采用串行方式完成设计。因此,设计人员可以定制满足算法和系统要求的方案,而不是取期望的理想设计的折衷方案来迎合纯顺序器件的诸多局限。另外,超高速I/O通过最大限度地提高从捕捉经处理链再到最终输出的数据流,可进一步降低成本并减少瓶颈问题。

下面以一个同时使用传统DSP架构和FPGA架构的FIR滤波器实现方案为例,来说明每种解决方案的优劣。

数字FIR滤波器实例

有限脉冲响应(FIR)滤波器是一种使用最广的数字信号处理元件。设计人员使用滤波器来改变数字信号的幅度或频谱,通常用于隔离或突出样本数据频谱中的特定区域。从这个角度来讲,可以把滤波器视为信号的预处理方式。在典型的滤波器应用中,输入数据样本通过小心同步的数学运算与滤波器系数相结合(这取决于滤波器的类型和实现策略),随后数据样本进入下一个处理阶段。如果数据源和目的地都是模拟信号,则数据样本必须首先通过A/D转换器,而结果则必须馈送给D/A转换器。

最简单的FIR滤波器是通过用一系列的延迟元件、乘法器和加法器树或加法器链来实现的。

下面的等式是单通道FIR滤波器的数学表达式:

公式1

该等式中的各项分别表示输入样本、输出样本和系数。假设S为连续的输入样本流,Y为经滤波后产生的输出样本流,那么n和k则对应特定的瞬时时间。这样,若要计算时间n时的输出样本Y(n),则需要一组在N个不同时间点的样本,即:S(n)、S(n-1)、s(n-2)、…s(n-N+1)。将这组N个输入样本乘以N个系数并求和,便可得出最终结果Y。

图2是一个简单的31抽头FIR滤波器(长度N=31)的框图。

图1:传统的DSP架构

图2:长度为31抽头的FIR滤波器

在选择滤波器的理想长度和系数值时,有多种设计工具可供使用。其目的是通过选择适当的参数来实现所需的滤波器性能。参数选择最常用的设计工具是MATLAB。一旦选定了滤波器参数,就可以用数学等式实现。

实现FIR滤波器的基本步骤包括:

1. 对输入数据流采样;

2. 在缓冲区组织输入样本,以便让每个捕捉到的样本与每项滤波器系数相乘;

3. 让每个数据样本与每项系数相乘,并累加结果;

4. 输出滤波结果。

使用“相乘累加法”在处理器上实现FIR滤波器的典型C语言程序,如下列代码所示。

图3所示的实现方案被称为相乘累加或MAC型实现方案。这基本上就是用传统的DSP处理器实现滤波器的方法。采用内核时钟速率为1.2GHz的典型DSP处理器并以这种方式实现的31抽头FIR滤波器的最高性能约为9.68MHz,或最大的输入数据率为968MS/s。

图3:传统DSP中的MAC实现方案

而FPGA提供了许多不同的实现和优化选择。如果需要高资源效率的实现,MAC引擎法则相当不错。还是以31抽头滤波器为例来说明滤波器规范对所需逻辑资源的影响,这种实现方案的框图如图4所示。

图4:FPGA中的MAC引擎FIR滤波器

这种设计需要存储器存储数据和系数,可以混合采用FPGA内部的RAM和ROM。RAM用于存储数据样本,故而采用循环的RAM缓冲器实现。字的数量与滤波器抽头数相等,位宽按样本大小设置。ROM用于存储系数。在最差情况下,字的数量与滤波器抽头的数量相等,但如果存在对称,则可以减少字的数量。位宽必须足以支持最大的系数。因为数据样本和系数数据都随每个周期改变,所以需要全乘法器。累加器负责将产生的结果累加起来。因为随着滤波器采集数据,累加器的输出会随每个时钟周期改变,所以需要捕捉寄存器。当全套N个样本完成累加后,输出寄存器负责捕捉最终结果。

如果采用MAC模式,DSP48则非常适合,因为DSP48Slice内含输入寄存器、输出寄存器和加法器单元。实现31抽头MAC引擎需要的资源包括一个DSP48、一个18kb块RAM和9个逻辑片。另外,还需要一些逻辑片用于采样、系数地址生成和控制。如果FPGA内置有600MHz的时钟,则在一个-3速度等级的Xilinx7系列器件中,该滤波器能够以19.35MHz或1,935MSps的输入采样速率运行。

如果系统规范需要更高性能的FIR滤波器,则可采用并行结构来实现。图5显示了直接I型实现方案的框图。

图5:FPGA中的直接I型滤波器

直接I型滤波器结构能够在FPGA中实现最高性能。这种结构(通常也被称作脉动FIR滤波器)采用流水线和加法器链,使DSP48 Slice发挥出最高性能。输入馈送到用作数据样本缓冲器的级联寄存器;每个寄存器向DSP48提供一个样本,然后乘以对应的系数;加法器链存储部分乘积,然后依次相加,从而得到最终结果。

这种设计无需外部逻辑电路支持滤波器,并且该结构可扩展用于支持任意数量的系数。因为没有高扇出的输入信号,所以这种结构能够实现最高性能。实现31抽头FIR滤波器仅需要31个DSP48逻辑片。如果FPGA内置有600MHz的时钟,则在一个-3速度等级的Xilinx7系列器件中,该滤波器能够以600MHz或600MSps的输入采样速率运行。

从这个实例可以清晰地看出,FPGA不仅在性能上显著超越了传统的数字信号处理器,而且要求的时钟速率也显著降低(因此,功耗也显著降低)。

这个实例只反映了采用PFGA实现FIR滤波器的两种技术。为了充分利用数据采样率规范,可对该器件进行进一步定制,此时,数据采样率可在连续MAC运算极值和全并行运算极值之间。您还可考虑在包括对称系数、插值、抽取、多通道或多速率的资源利用与性能之间进行更多的权衡取舍。Xilinx CORE Generator?或System Generator(系统发生器)实用工具可以帮助用户充分利用这些设计变量和技术。

DSP 电子 FPGA 电路 VHDL Verilog 滤波器 C语言 Xilinx 总线 解码器 相关文章:

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)