利用SuPA(LM32XX)给手持设备射频功率放大器供电

入、出电容设计考虑:

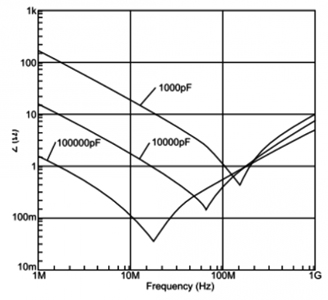

从图14 中可以看到输入电容为1nF 和10uF 组合,这样做的原因是可以滤除不同频率的噪音,输入端噪音可以来自两个部分:第一,来自于输入端电源总线上的噪音,比如总线还给其他负载供电,而这些负载的电源也是来自于DC-DC 变换器,因此在电源总线就会叠加非常丰富的噪音;第二,来自于LM3242的自身开关噪音,它的开关噪音同样会叠加在输入端,因此可能会干扰总线上的其它负载芯片,所以实际设计时,入口还会需要更多不同容值的电容才可以满足滤除不同噪音频率的要求,比如10pF 或者100pF的电容也会用到,不同容值的电容所针对的最佳滤除频率也是不一样的,对于大容量的电容来说它可以滤除的频率范围相对来说窄一些,因为它的拐点频率比较低,在拐点频率之内,电容的阻抗是呈下降趋势,也就是表现的是容性特质,但是拐点频率之上,阻抗是呈上升特性,则表现的是电感特性,因此不再具有滤波作用,这也就是需要搭配不同容值电容的原因所在,因为噪音频率非常丰富,一种容值的电容是不可能把宽频带的噪音全部滤除掉,另外还要注意同等容值、同等耐压的小尺寸的电容表现出来的容性带宽更宽一些,这主要是小尺寸的电容它的内部寄生电感量更小一些、同时它的有效容量更低一些,因此表现出来的特性就是滤除噪音的带宽更宽一些,从图中可以看出小容量但是尺寸更小的01005 封装的电容,它可以滤除的噪音频带更宽。

图15、电容阻抗和频率关系图

输出电感设计考虑:

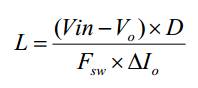

功率电感的计算,一般可以参照下面公式进行计算

Vo………………………..输出电压

D………………………….Vo/Vin

Fsw………………………开关频率,比如LM3242,开关频率是6MHz

ΔIo……………………….电感内部的纹波电流,可以取(0.2~0.5)Io

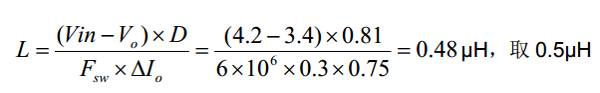

设计范例:

Vin=4.2V,Vo=3.4V,Io=0.75A,ΔIo=0.3*Io,Fsw=6MHz,D=3.4/4.2=0.81

则:

从公式中可以看出来,纹波电流越小则电感量就会越大,越小的纹波电流则在输出电容上产生的纹波电压就会越小(纹波电压=输出电容的ESR*纹波电流),但是电感的尺寸会变大,不利于小尺寸设计,因此在实际设计时,需要平衡电感量、纹波电流、电感尺寸之间的关系。在选择电感时,除了要满足电感量参数外,还要考虑电感的可以承受的最大电流,即IRMS 电流值,同时还要考虑电感的饱和电流值,即ISAT,如果流过电感的总电流ITOTAL=IDC+IRIPPLE 超过了ISAT,那就会使得电感饱和而失去了电感特性,即由电感变成了导线,从而造成变换器失效而损坏,通常来说,工程上快速评估可以采取1.5 倍的Io 做为一个合适的选取标准,比如输出负载电流为1A,那么选择电感的有效电流IRMS 为1.5A 为宜;还要注意的是,尽量选取带有屏蔽功能的电感,这样可以减少DC-DC 变换器工作时对外部环境造成的干扰。

10、SuPA 的PCB 设计和PCB 板叠层设计

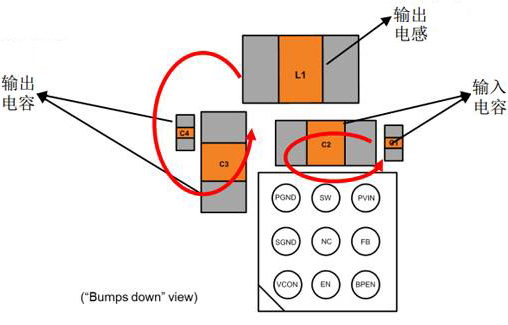

1. 功率器件的位置(输入、输出电容和电感)

如下图所示,

图16、LM3242布局示意图

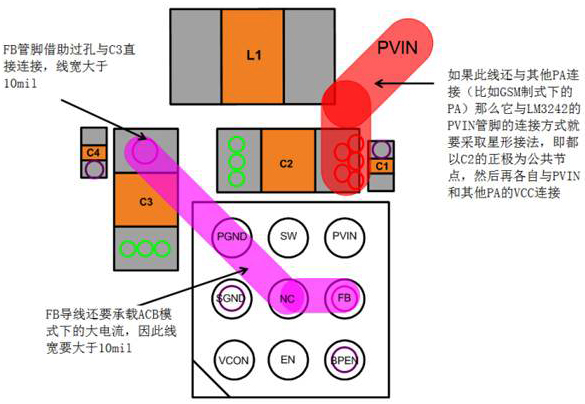

从图中可以看出入口电容C1和C2是放置在芯片PVIN管脚最近的位置,输出电容是放在距离电感输出端最近的位置,这样做的原因是保持输入端功率回路包含面积(芯片,C1和C2、地线组成的环路)以及输出端功率回路面积(输出电感、C3、C4、地线)最小,这样可以有效减小开关电源噪音对外部环境的干扰,这是在射频电路设计中需要仔细考虑的要点。

2. 功率器件与芯片间的连线和PCB板叠层定义

PCB 板叠层设计举例:

表层:用于连接流过大电流的连线,比如输入、输出电容、电感的电源线。

第二层:连接信号用的连线可以放置在此层,注意的是FB 管脚是被复用的(做为ACB 使用)会承载比较大的电流,因此需要使用10mil 以上的线宽连接。

第三层:连接SW 的连线可以放置此层,SW 是用来承载大于1A 以上的峰值电流,因此线宽需要大于15mil,在某些应用时甚至需要分配两层同时放置SW 铜线(两层叠加),用于减小寄生电感,尽可能降低在此铜线上的dv/dt,即SW 上的开关噪音振铃幅值。

第四层:系统地层,它需要一层完整的铜箔作为地层,它可以作为芯片SGND/PGND 的公共连接地层。

图17、LM3242布局表层连线示意图

图18、LM3242布局第二层连线示意图

图19、LM3242布局第三层连线示意图

图20、LM3242布局第四层连线示意图

11、结论和主流射频功放电源产品

当今的手

射频功率放大器 相关文章:

- 射频功率放大器实时检测的实现(03-29)

- 射频功率放大器简介(02-18)

- 录像机射频功率放大器工作原理简介(01-30)

- 射频功率放大器的自适应前馈线性化技术(03-12)

- 利用对数检波器实现射频功率放大器过驻波保护(08-12)

- 一种宽带射频功率放大器的匹配电路设计(05-13)