基于BF537的双冗余以太网的设计与实现

时间:11-28

来源:互联网

点击:

随着信息技术的高速发展,网络通信也显得越发重要,以太网也成为了各种控制系统接口互联的主要媒介。在金融机构、政府部门、军事应用等特殊应用场合对网络系统的稳定性要求非常高,为了提高系统的可靠性和抗毁性,常常采用双冗余的设计方式。双冗余网络的实现是以故障检测为基础,通过软件检查、交换机及网络节点的网卡协同处理共同完成的。冗余网络的构建方式通常是在每个网络节点采用双网卡,中间用两个HUB或交换机相连。这样当某个节点的一块网卡、网线或者HUB出现故障时,系统会马上启用另一块冗余网卡使得系统仍能够正常运行。本文基于BF537提出了两种冗余网络的构建方案和实现方法。

1 BF537结构特点

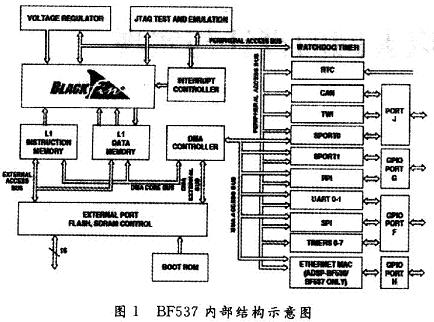

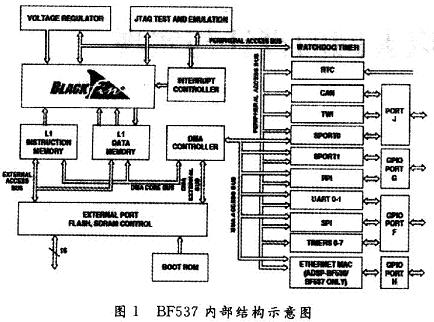

BF537是Blackfin家族的升级产品,其在标准Blackfin内核的基础上拥有更加丰富的接口,并在内部集成了一个以太网MAC控制器。BF537的内部结构如图1所示。

Blackfin内核包含2个乘/累加器(MAC),2个40位的ALU,4个视频专用8位ALU和1个40位移位器。运算单元处理来自寄存器组的8位、16位或者32位数据。每个MAC每周期可完成一个16位乘16位的乘法运算,并把结果累加到40位的累加器中,提供8位的精度扩展。ALU单元执行标准的算术和逻辑运算,由于2个ALU具备对16位或32位数据操作的能力,因此运算单元具备的灵活性可以满足各种应用中信号处理的要求。每个32位的输入寄存器可以作为2个16位的寄存器,因此每个ALU可以完成非常灵活的单16位算术运算。通过把寄存器当作2个16位的操作数使用,双16位或单32位操作可以在1个周期中完成。更好地利用第二个ALU,四个16位操作可以简单地完成,加速了每个周期的吞吐量。强大的40位移位器功能丰富,可以对数据进行移位、循环移位、归一化、提取和存储等操作。运算单元所使用的数据来自具有16个16位操作数或8个32位操作数的寄存器组。

同时BF537把存储器视为一个统一的4 GB的地址空间,使用32位地址并采用分级的存储器结构。Level(L1)存储器一般以全速运行,没有或只有很少的延迟。Level 2(L2)/Level 3(L3)分布在片内或片外,对它的访问会耗费多个处理器周期。在L1级,指令存储器只存放指令,2个数据存储器存放数据,一个专用的临时数据存储器存放堆栈和局部变量信息。在L2/L3级可以存放指令和数据。

2 双冗余以太网构建方案

从硬件角度看,以太网接口电路主要由MAC控制器和物理层接口(PHY)两大部分构成,本文从是否具备独立的MAC控制器出发提出了两种不同的构建双冗余以太网的方案。

2.1 基于独立MAC控制器的设计方案

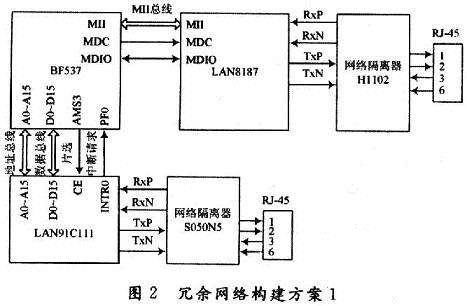

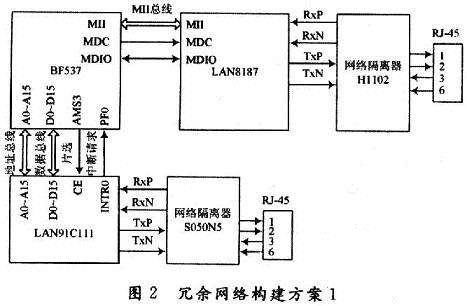

上文中提到,BF537在内部集成了一个支持IEEE802.3 MAC控制层协议的MAC控制器,只需要在外部外接一个以太网接口芯片,便可以形成一个完整的以太网通道。因此本文选择了SMSC公司的LAN8187,它提供了标准的MII总线接口,可以方便地与BF537相连接,连接方式如图2所示。其中在MII总线上进行数据的收发,MDC和MDIO则用来完成对接口芯片LAN8187寄存器的读写。本文在下面称由BF537的MAC控制器与物理层接口芯片LAN8187构成的以太网通道为主网络通道。

如果要求双冗余网络通道拥有独立的MAC控制器,则需在BF537外部扩展一个以太网控制器,见图2,选择同样来自于SMSC公司的LAN91C-111,通过BF537的外部总线与之相连。选择LAN91C111的16位总线工作方式,其A0~A15与BF537的地址总线相连,DO~D15与BF537的数据总线相连,并由BF537的AMS信号控制LAN91C111的片选,外部PF管脚来响应来自LAN91C111的中断请求。

具有独立MAC控制器的双冗余以太网的设计方案如图2所示。

2.2 基于共用MAC控制器的设计方案

从应用角度分析,即使系统拥有独立的MAC控制器,在实际应用中也需要要求两个MAC控制器拥有相同的物理地址,因为若MAC地址不同,冗余切换将引起协议层中ARP绑定表的变化,重新映射ARP表中物理地址和IP地址之间的关系将增加冗余切换的时间,影响到网络通信实时性。

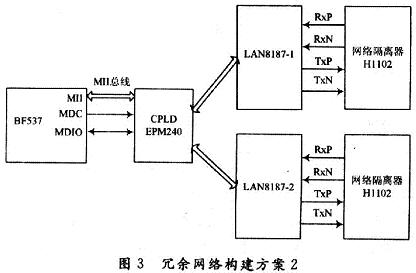

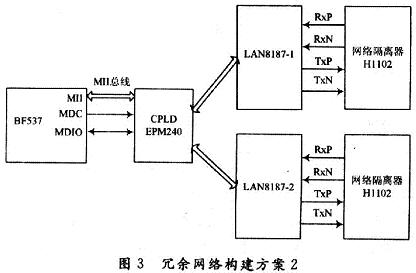

因此本文提出了一套MAC控制器,两个以太网接口芯片的方案。该设计方案通过一片CPLD将BF537的MII总线分别转接到两片LAN8187上,并由BF537来控制转接的时机,如图3所示。这样形成了两个以太网通信通道,大大简化了设计,提高了冗余切换的实时性。

3 冗余切换软件设计

3.1 网络状态监测

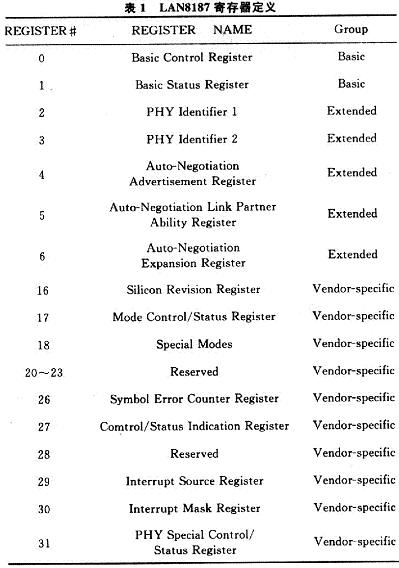

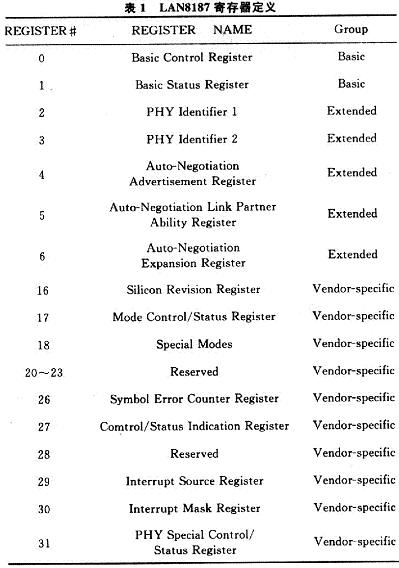

冗余切换的实现首先在于对网络实时在线监测,本文中检测的方法基于LAN8187的寄存器。LAN8187寄存器定义如表1所示。其中,Basic Control Register为基本控制寄存器,通过配置其各位,可以完成芯片软复位、lO/100 MHz选择、全双工/半双工选择、LookBack模式选择、自协商等功能。Basic Status Register为基本状态寄存器,对其查询可以得到自协商结果、网络物理连接状态等网络基本状态。PHY Identifier 1/PHY Identitier 2两个寄存器标识了芯片的Chip ID。

因此,对网络状态的实时监测实际上就是实时读取Basic Status Register,并对结果做出判断。

1 BF537结构特点

BF537是Blackfin家族的升级产品,其在标准Blackfin内核的基础上拥有更加丰富的接口,并在内部集成了一个以太网MAC控制器。BF537的内部结构如图1所示。

Blackfin内核包含2个乘/累加器(MAC),2个40位的ALU,4个视频专用8位ALU和1个40位移位器。运算单元处理来自寄存器组的8位、16位或者32位数据。每个MAC每周期可完成一个16位乘16位的乘法运算,并把结果累加到40位的累加器中,提供8位的精度扩展。ALU单元执行标准的算术和逻辑运算,由于2个ALU具备对16位或32位数据操作的能力,因此运算单元具备的灵活性可以满足各种应用中信号处理的要求。每个32位的输入寄存器可以作为2个16位的寄存器,因此每个ALU可以完成非常灵活的单16位算术运算。通过把寄存器当作2个16位的操作数使用,双16位或单32位操作可以在1个周期中完成。更好地利用第二个ALU,四个16位操作可以简单地完成,加速了每个周期的吞吐量。强大的40位移位器功能丰富,可以对数据进行移位、循环移位、归一化、提取和存储等操作。运算单元所使用的数据来自具有16个16位操作数或8个32位操作数的寄存器组。

同时BF537把存储器视为一个统一的4 GB的地址空间,使用32位地址并采用分级的存储器结构。Level(L1)存储器一般以全速运行,没有或只有很少的延迟。Level 2(L2)/Level 3(L3)分布在片内或片外,对它的访问会耗费多个处理器周期。在L1级,指令存储器只存放指令,2个数据存储器存放数据,一个专用的临时数据存储器存放堆栈和局部变量信息。在L2/L3级可以存放指令和数据。

2 双冗余以太网构建方案

从硬件角度看,以太网接口电路主要由MAC控制器和物理层接口(PHY)两大部分构成,本文从是否具备独立的MAC控制器出发提出了两种不同的构建双冗余以太网的方案。

2.1 基于独立MAC控制器的设计方案

上文中提到,BF537在内部集成了一个支持IEEE802.3 MAC控制层协议的MAC控制器,只需要在外部外接一个以太网接口芯片,便可以形成一个完整的以太网通道。因此本文选择了SMSC公司的LAN8187,它提供了标准的MII总线接口,可以方便地与BF537相连接,连接方式如图2所示。其中在MII总线上进行数据的收发,MDC和MDIO则用来完成对接口芯片LAN8187寄存器的读写。本文在下面称由BF537的MAC控制器与物理层接口芯片LAN8187构成的以太网通道为主网络通道。

如果要求双冗余网络通道拥有独立的MAC控制器,则需在BF537外部扩展一个以太网控制器,见图2,选择同样来自于SMSC公司的LAN91C-111,通过BF537的外部总线与之相连。选择LAN91C111的16位总线工作方式,其A0~A15与BF537的地址总线相连,DO~D15与BF537的数据总线相连,并由BF537的AMS信号控制LAN91C111的片选,外部PF管脚来响应来自LAN91C111的中断请求。

具有独立MAC控制器的双冗余以太网的设计方案如图2所示。

2.2 基于共用MAC控制器的设计方案

从应用角度分析,即使系统拥有独立的MAC控制器,在实际应用中也需要要求两个MAC控制器拥有相同的物理地址,因为若MAC地址不同,冗余切换将引起协议层中ARP绑定表的变化,重新映射ARP表中物理地址和IP地址之间的关系将增加冗余切换的时间,影响到网络通信实时性。

因此本文提出了一套MAC控制器,两个以太网接口芯片的方案。该设计方案通过一片CPLD将BF537的MII总线分别转接到两片LAN8187上,并由BF537来控制转接的时机,如图3所示。这样形成了两个以太网通信通道,大大简化了设计,提高了冗余切换的实时性。

3 冗余切换软件设计

3.1 网络状态监测

冗余切换的实现首先在于对网络实时在线监测,本文中检测的方法基于LAN8187的寄存器。LAN8187寄存器定义如表1所示。其中,Basic Control Register为基本控制寄存器,通过配置其各位,可以完成芯片软复位、lO/100 MHz选择、全双工/半双工选择、LookBack模式选择、自协商等功能。Basic Status Register为基本状态寄存器,对其查询可以得到自协商结果、网络物理连接状态等网络基本状态。PHY Identifier 1/PHY Identitier 2两个寄存器标识了芯片的Chip ID。

因此,对网络状态的实时监测实际上就是实时读取Basic Status Register,并对结果做出判断。

- 基于P89C61x2/ISP1581的USB接口电路的设计(02-13)

- 行波管关断方式对应用系统可靠性的影响(06-24)

- 基于VME总线的RDC接口电路设计(06-29)

- 单芯片集成电路优化自适应转向大灯系统的设计 (07-12)

- 单片机应用系统的抗干扰技术(08-07)

- 基于FPGA的线阵CCD驱动器设计(11-26)