基于DSP的高分辨SAR多普勒调频率的估算

时间:11-29

来源:互联网

点击:

雷达可以全天候、全天时、远距离对目标进行检测和定位,随着合成孔径雷达(SAR)技术的引入,可以通过SAR获得观测区域的高分辨图像,在国民经济和军事领域中有着十分重要的应用。为了获得高分辨,发射大时宽的宽频带信号,如线性调频信号等,可以在接收后进行脉冲压缩来实现。在实际处理中,脉冲压缩是通过快速傅里叶变换来实现的,对于场景大、分辨率高的情况,尤其是在实时成像中实际运算量也是十分的巨大。为此,采用由ADI公司的TS-201S高性能数字信号处理器搭建的平台来实现实时成像系统。文中分析了MD算法实际工程应用,并完成了多普勒调频率估计的快速估算。

1 基本原理

1.1 高分辨SAR成像计算流程

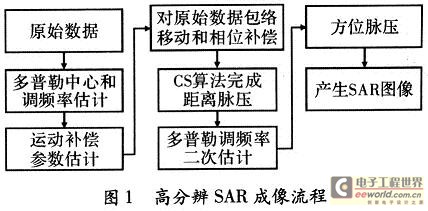

从图1中可以看出在整个实时成像系统中,多普勒调频率的准确而快速的计算尤为重要。其中在运动补偿中,运动补偿参数是由多普勒调频率推导出的。在方位脉冲压缩中,在用CS算法完成距离向的距离走动和距离弯曲矫正后,还需要对多普勒调频率做再次的估计,以便于精确的完成方位脉冲压缩,因此多普勒调频率的计算精度和速度对成像有很大的影响。

1.2 MD估计算法

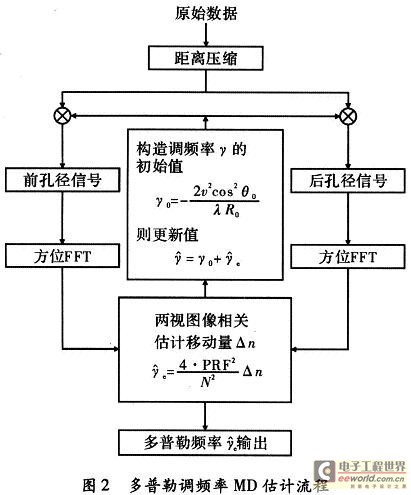

在实际应用中,MD估计算法是主要的多普勒调频率估计算法,由于二次相位是使图像产生模糊的主要相位项,且MD估计算法能稳健地估计二次相位。MD估计算法将全孔径时间分成不交叠的两个子孔径,在利用二次相位在前后两部分孔径中有不同的函数表述式子。每个子孔径可分解成常量、一次分量和二次分量,其中常量和二次分量相同,一次分量使两个子孔径像平移。MD估计算法就是通过估计两个子孔径之间的平移量,估计整个孔径的二次项系数,得到多普勒调频率的估计值。其具体流程,如图2所示。

2 DSP编程实现

在实测数据的Matlab处理中,MD算法流程实现如图3所示。为了使多普勒调频率估计精度满足实际的需要,通常需要用估计出的多普勒调频率作为调频率参考值从对距离脉压数据做方位脉压,然后重复子孔径相关等后面的步骤,得出更精确的调频率值。一般重复3次即可,次数越多越精确,但是考虑的成像效果以及实时性的要求,3次重复就可以得出满意的结果。这里n为所选取的最大的能量和数量,这里选64即可以满足要求。

文中选用ADI公司的TSs-20lS高性能数字信号处理器在运算能力、与外部通信能力及在大内存设计等方面都优于其它类型的处理芯片。其主要特点有:(1)内部时钟频率最高为600 MHz,指令周期1.67 ns(在此系统中内部核时钟采用500 MHz,指令周期为2 ns),24 MB的片内DRAM存储器,分为6个4 MB的存储器块,每个块包含128 000个32位字,每个块内存连接着交叉线通过它自身的缓冲和一个128 000 kB的4-Way缓冲器;(2)芯片内包含两个运算模块(X-ComputeBlocks,Y-Compute Blocks),每个模块包括一个整数ALU、一个乘法器、一个移位器和一个寄存器组(32-word)和一个通信逻辑单元。其中,ALU用于寻址和指针操作;(3)4条128 bit的总线提供高的带宽连接内部存储块。扩展端口包含主机端口、SDRAM控制器、静态管线接口、4个DMA通道。4个LVDS连接端口(每一个都连接2个DMA通道),支持8片DSP共享总线的片上仲裁,无需其它逻辑。IEEE 1149.1兼容的JTAG测试端口用于片上仿真。外部端口的DMA传输速率可达1 GB/s,每个链路口的DMA传输速率可达1 GB/s,共计5 GB/s的外部I/O能力。而且,ADSP-TFS201S的静态超标量结构使其每周期能够执行多达4条指令、24个16位定点运算和6个浮点运算;4条相互独立的内部数据总线(128位),每条连接到6个4 MB的内部存储器块。提供了4 bit的数据、指令I/O访问和33.6 GB/s的内部存储器带宽。因此运行在500 MHz时,ADSP-TS201S的可以提供48亿次40位的MAC运算或者12亿次的80位MAC运算。雷达成像中用到了大量的FFT运算,TS201在计算。FFT时速度很快。例如,运行在500 MHz时,做1 024点的FFT只需18.8μs。ADSP-TS201S有丰富的内部存储资源,而且也特别适合于并行计算,组成高速并行处理器。这对于高分辨SAR实时成像系统而言非常有利。

在此实时成像中的多普勒调频率估计中,数据块为512×4 096(方位向和距离向)个复数。分别按照并且需要计算16个调频率值,即按距离单元分为16个子数据块,每个块为512×256个复数。为保证计算精度,一个复数占2×32 bit的存储单元,即实部虚部各占一个4 bit单元。

由于数据从SDRAM读到内部存储器中需要很多机器周期,在此时计算块就会处于空闲状态,不利于提高运行速度和执行效率,所以在实际计算时,采用如图4所示的流程来提高效率。图4中,相同的箭头表示同时交换数据。当计算块在计算内部存储区1的数据时,内部存储区2通过TS-201S的DMA模块直接和SDRAM交换数据。当计算完内部存储区1的数据时,计算块就直接计算内部存储区2的数据,同时内部存储区1通过 TS-201S的DMA模块直接和SDRAM交换数据,此时计算块一直处于满负荷状态,不用为等待数据而变得空闲,这种运算方式即所谓的“乒乓”方式。在使用DSP实现算法流程时,按方位向求能量和、方位脉压及子孔径相关的运算量最大,重点在这几方面进行优化。

1 基本原理

1.1 高分辨SAR成像计算流程

从图1中可以看出在整个实时成像系统中,多普勒调频率的准确而快速的计算尤为重要。其中在运动补偿中,运动补偿参数是由多普勒调频率推导出的。在方位脉冲压缩中,在用CS算法完成距离向的距离走动和距离弯曲矫正后,还需要对多普勒调频率做再次的估计,以便于精确的完成方位脉冲压缩,因此多普勒调频率的计算精度和速度对成像有很大的影响。

1.2 MD估计算法

在实际应用中,MD估计算法是主要的多普勒调频率估计算法,由于二次相位是使图像产生模糊的主要相位项,且MD估计算法能稳健地估计二次相位。MD估计算法将全孔径时间分成不交叠的两个子孔径,在利用二次相位在前后两部分孔径中有不同的函数表述式子。每个子孔径可分解成常量、一次分量和二次分量,其中常量和二次分量相同,一次分量使两个子孔径像平移。MD估计算法就是通过估计两个子孔径之间的平移量,估计整个孔径的二次项系数,得到多普勒调频率的估计值。其具体流程,如图2所示。

2 DSP编程实现

在实测数据的Matlab处理中,MD算法流程实现如图3所示。为了使多普勒调频率估计精度满足实际的需要,通常需要用估计出的多普勒调频率作为调频率参考值从对距离脉压数据做方位脉压,然后重复子孔径相关等后面的步骤,得出更精确的调频率值。一般重复3次即可,次数越多越精确,但是考虑的成像效果以及实时性的要求,3次重复就可以得出满意的结果。这里n为所选取的最大的能量和数量,这里选64即可以满足要求。

文中选用ADI公司的TSs-20lS高性能数字信号处理器在运算能力、与外部通信能力及在大内存设计等方面都优于其它类型的处理芯片。其主要特点有:(1)内部时钟频率最高为600 MHz,指令周期1.67 ns(在此系统中内部核时钟采用500 MHz,指令周期为2 ns),24 MB的片内DRAM存储器,分为6个4 MB的存储器块,每个块包含128 000个32位字,每个块内存连接着交叉线通过它自身的缓冲和一个128 000 kB的4-Way缓冲器;(2)芯片内包含两个运算模块(X-ComputeBlocks,Y-Compute Blocks),每个模块包括一个整数ALU、一个乘法器、一个移位器和一个寄存器组(32-word)和一个通信逻辑单元。其中,ALU用于寻址和指针操作;(3)4条128 bit的总线提供高的带宽连接内部存储块。扩展端口包含主机端口、SDRAM控制器、静态管线接口、4个DMA通道。4个LVDS连接端口(每一个都连接2个DMA通道),支持8片DSP共享总线的片上仲裁,无需其它逻辑。IEEE 1149.1兼容的JTAG测试端口用于片上仿真。外部端口的DMA传输速率可达1 GB/s,每个链路口的DMA传输速率可达1 GB/s,共计5 GB/s的外部I/O能力。而且,ADSP-TFS201S的静态超标量结构使其每周期能够执行多达4条指令、24个16位定点运算和6个浮点运算;4条相互独立的内部数据总线(128位),每条连接到6个4 MB的内部存储器块。提供了4 bit的数据、指令I/O访问和33.6 GB/s的内部存储器带宽。因此运行在500 MHz时,ADSP-TS201S的可以提供48亿次40位的MAC运算或者12亿次的80位MAC运算。雷达成像中用到了大量的FFT运算,TS201在计算。FFT时速度很快。例如,运行在500 MHz时,做1 024点的FFT只需18.8μs。ADSP-TS201S有丰富的内部存储资源,而且也特别适合于并行计算,组成高速并行处理器。这对于高分辨SAR实时成像系统而言非常有利。

在此实时成像中的多普勒调频率估计中,数据块为512×4 096(方位向和距离向)个复数。分别按照并且需要计算16个调频率值,即按距离单元分为16个子数据块,每个块为512×256个复数。为保证计算精度,一个复数占2×32 bit的存储单元,即实部虚部各占一个4 bit单元。

由于数据从SDRAM读到内部存储器中需要很多机器周期,在此时计算块就会处于空闲状态,不利于提高运行速度和执行效率,所以在实际计算时,采用如图4所示的流程来提高效率。图4中,相同的箭头表示同时交换数据。当计算块在计算内部存储区1的数据时,内部存储区2通过TS-201S的DMA模块直接和SDRAM交换数据。当计算完内部存储区1的数据时,计算块就直接计算内部存储区2的数据,同时内部存储区1通过 TS-201S的DMA模块直接和SDRAM交换数据,此时计算块一直处于满负荷状态,不用为等待数据而变得空闲,这种运算方式即所谓的“乒乓”方式。在使用DSP实现算法流程时,按方位向求能量和、方位脉压及子孔径相关的运算量最大,重点在这几方面进行优化。

- ADI公司双极性四通道运算放大器OP4177及其应用(02-18)

- 三菱电机的汽车数字处理中心DIATONE DA-PX1采用SHARC处理器(11-10)

- 用Blackfin处理器为您的应用置入低功耗引擎(01-11)

- ADuCM361精密模拟微控制器详细介绍(07-27)

- ADuCM361精密模拟微控制器实例开发手册(独家)(08-12)

- SHARC处理器在音频系统中的典型应用(01-08)