并行流水结构的RS255/RS233译码器设计实现

时间:11-28

来源:互联网

点击:

3 仿真验证与综合

上述译码器采用自顶向下的设计流程划分模块,用Verilog HDL完成RTL代码的编写,然后在Mentor公司的ModelSim SE 6.1b仿真验证工具下编写测试代码进行仿真验证。仿真结果如图6所示,译码器能正确实现译码功能。

因本译码器可纠正16个错误,超过16个错误便不可纠正,在仿真时译码输入样本采用了2种:一种样本不超过16个错误,另一种样本超过16个错误。仿真结果表明,此译码器能在不超过16个错误的样本下正常译码。

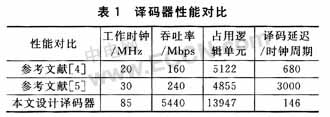

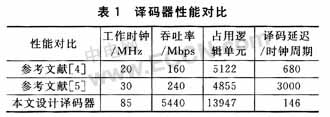

译码器在Quartus II 8.0上进行综合和优化,采用Altera公司Cyclone系列的EP2C15AF256C8芯片为目标器件。译码器的工作时钟频率可达85 MHz,数据吞吐率可达5 440 Mb/s,占用逻辑单元数为13 947个(片内共14 448,占用率为97%),RAM占用16 698位(片内共239 616位,占用率为7%)。译码器性能对比如表1所列。

与参考文献相比,由于本译码器采用了并行结构在增加了不到3倍的硬件资源的情况下,吞吐率时钟比(吞吐率/时钟)提高了8倍,而且缩短了3/4的泽码延迟。与参考文献相比,本文所采用的译码器增加了不到3倍的硬件资源,提高了8倍的吞吐率时钟比。由于参考文献采用串行译码结构,本文所采用的并行流水译码结构较串行译码结构缩减了19/20的译码延迟。

上述译码器采用自顶向下的设计流程划分模块,用Verilog HDL完成RTL代码的编写,然后在Mentor公司的ModelSim SE 6.1b仿真验证工具下编写测试代码进行仿真验证。仿真结果如图6所示,译码器能正确实现译码功能。

因本译码器可纠正16个错误,超过16个错误便不可纠正,在仿真时译码输入样本采用了2种:一种样本不超过16个错误,另一种样本超过16个错误。仿真结果表明,此译码器能在不超过16个错误的样本下正常译码。

译码器在Quartus II 8.0上进行综合和优化,采用Altera公司Cyclone系列的EP2C15AF256C8芯片为目标器件。译码器的工作时钟频率可达85 MHz,数据吞吐率可达5 440 Mb/s,占用逻辑单元数为13 947个(片内共14 448,占用率为97%),RAM占用16 698位(片内共239 616位,占用率为7%)。译码器性能对比如表1所列。

与参考文献相比,由于本译码器采用了并行结构在增加了不到3倍的硬件资源的情况下,吞吐率时钟比(吞吐率/时钟)提高了8倍,而且缩短了3/4的泽码延迟。与参考文献相比,本文所采用的译码器增加了不到3倍的硬件资源,提高了8倍的吞吐率时钟比。由于参考文献采用串行译码结构,本文所采用的并行流水译码结构较串行译码结构缩减了19/20的译码延迟。

电路 仿真 Verilog Mentor ModelSim Quartus Altera 相关文章:

- 基于P89C61x2/ISP1581的USB接口电路的设计(02-13)

- 行波管关断方式对应用系统可靠性的影响(06-24)

- 基于VME总线的RDC接口电路设计(06-29)

- 单芯片集成电路优化自适应转向大灯系统的设计 (07-12)

- 单片机应用系统的抗干扰技术(08-07)

- 基于FPGA的线阵CCD驱动器设计(11-26)