DSP SPI口和串行EEPROM在变频器中的应用

时间:11-27

来源:互联网

点击:

1 引言

变频器的开发中我们选用TMS320F240芯片做主CPU,TMS320F240系列是美国TI公司于1997年推出的,专为数字电机控制和其它控制应用系统而设计的16位定点数字信号处理器。它将数字信号处理的高速运算功能与面向电机的强大控制能力结合在一起,成为中低端变频器理想的主控芯片。F240片内外设包括双10位A/D转换器,带有锁相环PLL时钟模块,带中断的看门狗定时器模块,串行通信接口SCI及串行外设接口SPI,另外,还集成了一个事件管理模块EVM。因此,TMS320F240基本能满足笔者变频器设计的要求。

变频器有几百甚至上千个参数,这些参数值都要求系统断电后不能丢失,在设计中我们选用非易失性存储器EEPROM保存数据。每次上电时,从EEPROM中读取上次参数的设定值,以保证变频器运行状态的连续性,同样每次断电时,也要保存变频器此次运行的参数设定情况,以便开机时读取。本文阐述了变频器开发中F240扩展EEPROM(X5168)的设计思路和实现过程。

2 对TMS320F240的串行外设接口(SPI)的说明

TMS320F240的串行外设接口(SPI)模块是一个高速同步串行输入/输出端口,它允许F240控制器和片外外设或其他控制器进行串行通信,在通信过程中,SPI能够以任意给定的传输速率对具有可编成长度(1-8位)的串行比特流进行收发。该模块也是一个8位外设,它直接挂在16位的片内外设总线上,因此,外设总线的高8位读写访问对该模块是没有意义的。

SPI模块的特性如下:

(1) 4个外部引脚。SPISOM I为SPI从输出/主输入引脚;SPISIMO为SPI从输入/主输出引脚;SPISTE为SPI从发送使能引脚;SPICLK为SPI串行时钟引脚。

(2) 两种工作方式,即主模式(Master)和从模式(Slave)。

(3) 数据字长。1-8个数据位。

(4) 可同时接收和发送数据,发送和接收操作可通过中断或查询方法来完成。

(5) 波特率,l25种可编程的波特率,下列两个公式给出了计算SPI的波特率的方法:

1. 当SPIBRR=3-127时,SPI波特率=系统时钟频率/(SPI寄存器的值+1);

2. 当SPIBRR=0、1、2时,SPI波特率=系统时钟频率/4;

(6) 4种时钟方案,由时钟极性位(SPICCR寄存器的位6)和时钟相位位(SPICTL寄存器的位3)进行设置,包括:

1. 无延时下降沿有效:串行外设接口在SPICLK 信号下降沿发送数据,而在SPICLK 信号上升沿接收数据;

2. 有延时下降沿有效:串行外设接口在SPICLK 信号下降沿之前的半个周期时发送数据,而在SPICLK 信号下降沿接收数据;

3. 无延时上升沿有效:串行外设接口在SPICLK 信号上升沿发送数据,而在SPICLK 信号下降沿接收数据;

4. 有延时上升沿有效:串行外设接口在SPICLK 信号上升沿之前的半个周期时发送数据, 在SPICLK 信号上升沿接收数据。

3 对X5168的说明

DSP处理速度比较快,且本设计需要保存的数据量大,笔者选择了XICOR公司的带16Kb SPI EEPROM 的CPU监视器X5168。器件把四种常用的功能:上电复位、看门狗定时器、电源电压监控和块锁存保护的串行EEPROM 存储器集成在一个封装之内,这种组合降低了系统成本,减少了电路板空间,增加了可靠性。

器件的存储器部分是带有XICOR公司的块锁存保护的CMOS串行EEPROM 阵列,阵列的内部组织是x8位。具有串行外围接口(SPI)和软件协议的特点,允许在简单的四线总线上工作。利用XICOR专有的直接写入晶片,提供最小为100,000次擦写和最少为100 年的数据保存期。

4 DSP与X5168的连接通信

4.1硬件设计

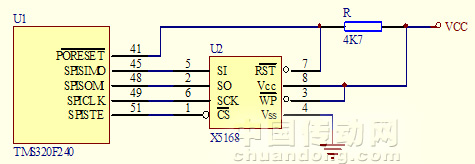

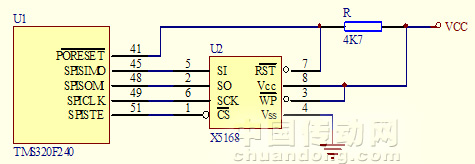

在变频器设计中DSP与X5168的硬件连接图如图1

图1 TMS320F240与X5168连接原理图

串行外设接口(SPI)有两种工作模式:主模式和从模式,与X5168 连接时工作于主模式。从图中可看到,X5168通过四根线来完成与DSP的数据交换,DSP的SPISIMO、SPISOMI、SPICLK、SPISTE引脚分别连接X5168的SI(串行输入)、SO(串行输出)、SCK(串行时钟)、/CS(片选端),此时的F240控制器称为“主机”,这种情况下,SPI在SPICLK引脚上提供了整个串行通信网络所需的串行时钟;数据从SPISIMO引脚输出;并锁存从SPISOMI引脚输入的数据;SPIBRR寄存器决定了整个串行通信网络中数据发送和接收时的位传输率。

写入SPIDAT的数据启动了SPISIMO引脚上的数据发送,先发送最高有效位;同时,接收的数据通过SPISOMI引脚移入SPIDAT的最低有效位。当有一定数量的数据位通过SPIDAT移位时,产生下列事件:

一、SPI INT FLAG置1

二、SPIDAT的内容传送到SPIBUF

三、如果SPI INT ENA也被置1,则产生中断请求

在主模式中,无论寄存器SPIPC1的位5(SPISTE FUNCTION)为何值,SPISTE引脚都将用作通用数字I/O引脚。在本设计中,引脚SPISTE用作从机SPI模块的片选引脚;在将主机数据传送到从机器件之前,应将从机器件片选引脚拉低电平,并且在传送完主机数据之后,重新将该引脚拉为高电平。

变频器的开发中我们选用TMS320F240芯片做主CPU,TMS320F240系列是美国TI公司于1997年推出的,专为数字电机控制和其它控制应用系统而设计的16位定点数字信号处理器。它将数字信号处理的高速运算功能与面向电机的强大控制能力结合在一起,成为中低端变频器理想的主控芯片。F240片内外设包括双10位A/D转换器,带有锁相环PLL时钟模块,带中断的看门狗定时器模块,串行通信接口SCI及串行外设接口SPI,另外,还集成了一个事件管理模块EVM。因此,TMS320F240基本能满足笔者变频器设计的要求。

变频器有几百甚至上千个参数,这些参数值都要求系统断电后不能丢失,在设计中我们选用非易失性存储器EEPROM保存数据。每次上电时,从EEPROM中读取上次参数的设定值,以保证变频器运行状态的连续性,同样每次断电时,也要保存变频器此次运行的参数设定情况,以便开机时读取。本文阐述了变频器开发中F240扩展EEPROM(X5168)的设计思路和实现过程。

2 对TMS320F240的串行外设接口(SPI)的说明

TMS320F240的串行外设接口(SPI)模块是一个高速同步串行输入/输出端口,它允许F240控制器和片外外设或其他控制器进行串行通信,在通信过程中,SPI能够以任意给定的传输速率对具有可编成长度(1-8位)的串行比特流进行收发。该模块也是一个8位外设,它直接挂在16位的片内外设总线上,因此,外设总线的高8位读写访问对该模块是没有意义的。

SPI模块的特性如下:

(1) 4个外部引脚。SPISOM I为SPI从输出/主输入引脚;SPISIMO为SPI从输入/主输出引脚;SPISTE为SPI从发送使能引脚;SPICLK为SPI串行时钟引脚。

(2) 两种工作方式,即主模式(Master)和从模式(Slave)。

(3) 数据字长。1-8个数据位。

(4) 可同时接收和发送数据,发送和接收操作可通过中断或查询方法来完成。

(5) 波特率,l25种可编程的波特率,下列两个公式给出了计算SPI的波特率的方法:

1. 当SPIBRR=3-127时,SPI波特率=系统时钟频率/(SPI寄存器的值+1);

2. 当SPIBRR=0、1、2时,SPI波特率=系统时钟频率/4;

(6) 4种时钟方案,由时钟极性位(SPICCR寄存器的位6)和时钟相位位(SPICTL寄存器的位3)进行设置,包括:

1. 无延时下降沿有效:串行外设接口在SPICLK 信号下降沿发送数据,而在SPICLK 信号上升沿接收数据;

2. 有延时下降沿有效:串行外设接口在SPICLK 信号下降沿之前的半个周期时发送数据,而在SPICLK 信号下降沿接收数据;

3. 无延时上升沿有效:串行外设接口在SPICLK 信号上升沿发送数据,而在SPICLK 信号下降沿接收数据;

4. 有延时上升沿有效:串行外设接口在SPICLK 信号上升沿之前的半个周期时发送数据, 在SPICLK 信号上升沿接收数据。

3 对X5168的说明

DSP处理速度比较快,且本设计需要保存的数据量大,笔者选择了XICOR公司的带16Kb SPI EEPROM 的CPU监视器X5168。器件把四种常用的功能:上电复位、看门狗定时器、电源电压监控和块锁存保护的串行EEPROM 存储器集成在一个封装之内,这种组合降低了系统成本,减少了电路板空间,增加了可靠性。

器件的存储器部分是带有XICOR公司的块锁存保护的CMOS串行EEPROM 阵列,阵列的内部组织是x8位。具有串行外围接口(SPI)和软件协议的特点,允许在简单的四线总线上工作。利用XICOR专有的直接写入晶片,提供最小为100,000次擦写和最少为100 年的数据保存期。

4 DSP与X5168的连接通信

4.1硬件设计

在变频器设计中DSP与X5168的硬件连接图如图1

图1 TMS320F240与X5168连接原理图

串行外设接口(SPI)有两种工作模式:主模式和从模式,与X5168 连接时工作于主模式。从图中可看到,X5168通过四根线来完成与DSP的数据交换,DSP的SPISIMO、SPISOMI、SPICLK、SPISTE引脚分别连接X5168的SI(串行输入)、SO(串行输出)、SCK(串行时钟)、/CS(片选端),此时的F240控制器称为“主机”,这种情况下,SPI在SPICLK引脚上提供了整个串行通信网络所需的串行时钟;数据从SPISIMO引脚输出;并锁存从SPISOMI引脚输入的数据;SPIBRR寄存器决定了整个串行通信网络中数据发送和接收时的位传输率。

写入SPIDAT的数据启动了SPISIMO引脚上的数据发送,先发送最高有效位;同时,接收的数据通过SPISOMI引脚移入SPIDAT的最低有效位。当有一定数量的数据位通过SPIDAT移位时,产生下列事件:

一、SPI INT FLAG置1

二、SPIDAT的内容传送到SPIBUF

三、如果SPI INT ENA也被置1,则产生中断请求

在主模式中,无论寄存器SPIPC1的位5(SPISTE FUNCTION)为何值,SPISTE引脚都将用作通用数字I/O引脚。在本设计中,引脚SPISTE用作从机SPI模块的片选引脚;在将主机数据传送到从机器件之前,应将从机器件片选引脚拉低电平,并且在传送完主机数据之后,重新将该引脚拉为高电平。

看门狗 总线 PIC DSP 电压 电路 CMOS 相关文章:

- 单片机与PLC编程的区别(10-18)

- 微处理器超长启动周期中的外部看门狗管理方案(05-27)

- 看门狗管理方案设计及应用汇总(01-14)

- DSP自动加载过程及程序烧写的简化设计(02-24)

- CapsMCU在小家电产品中的应用(04-03)

- 基于Proteus和ADS的ARM虚拟实验室建设(05-12)