一个针对FPGA的完全可配置嵌入式32位RISC处理器

时间:11-27

来源:互联网

点击:

使用嵌入式微处理器的FPGA设计不断增长。根据Dataquest的统计,一年大约启动10万个FPGA设计项目,其中约30%包含某种形式的微处理器。

形成这种趋势有几个方面的原因。首先,数据流应用更适合可编程硬件,同时嵌入式微处理器更适合于执行控制流的应用。第二,要改变设计时,嵌入式处理器呈现更大的灵活性。最后,用软核的嵌入式微处理器消除了处理器过时的风险。从传统上而言,对嵌入式FPGA微处理器有一些限制,包括成本,速度和设计性能。随着工艺技术和设计技术的进步,这些限制正在不断改善,现在设计人员更有可能在他们的应用中考虑使用嵌入式FPGA微处理器。

与过去相比,现成的微处理器已经大大比嵌入式微处理器便宜。但是,今天的低成本FPGA被证明是一个节约成本的解决方案。如果设计中已经使用了FPGA,处理器可以整合到现有的FPGA架构,节省了分立器件或新的FPGA成本。设计周期也是一个重要的因素。将硬件与微处理器子系统构成相关的架构并进行实施能有多快?编写,测试和在微处理器上调试运行的代码需要多久?在过去几年中,在整体功能和易用性方面,针对嵌入式微处理器开发的软件工具也有了明显的改善。因此,现在可以在几分钟内运行设计,并且进行测试。产品上市的时间缩短了,因为现在用软件实现功能比硬件更快,更简单。

用现成的微处理器达到的性能有良好的历史记录。随着技术的改进,FPGA在功能和整个系统的速度方面有了显著的进步。由于现在的FPGA能够处理更大的带宽,嵌入式处理器对于许多设计有很大的吸引力。此外,由于FPGA与其他专用模块的紧密配合,软IP核的扩展性提供了一个系统接口,就性能和吞吐量方面而言,现在一个片上处理器可以提供卓越的设计方案。

当评估诸如LatticeMico32这样的特殊处理器时,使用嵌入式软处理器的优点非常清楚。

一个典型的嵌入式处理器子系统

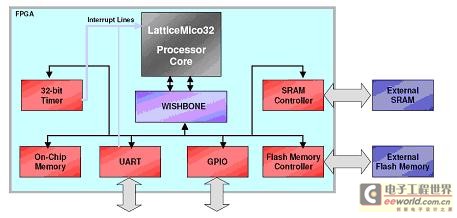

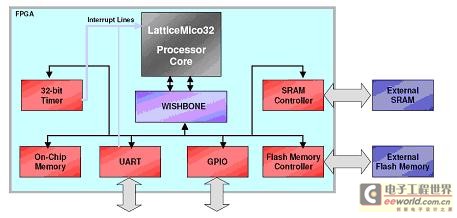

让我们来看看一个典型的嵌入式处理器子系统,例如,LatticeMico32软处理器。该处理器需要有能与外界通信的功能,因此通常核连接到一个片上总线系统,在此情况下是WISHBONE开放源代码总线。然后还需要一个存储系统,用来保存处理器程序代码以及处理器核使用的数据。对外部通信而言,在一个典型的系统中有各种接口,从简单的通信接口和连接、更复杂的协议到应用中的专用硬件模块。现在该处理器总线架构需要连接外设和存储器系统。一个典型的系统如图1所示。

图1 典型的嵌入式RISC处理器子系统

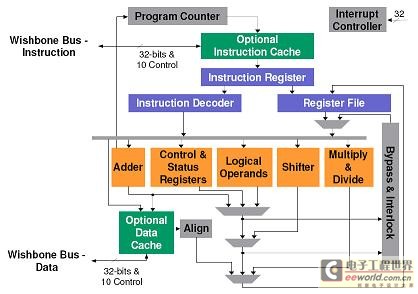

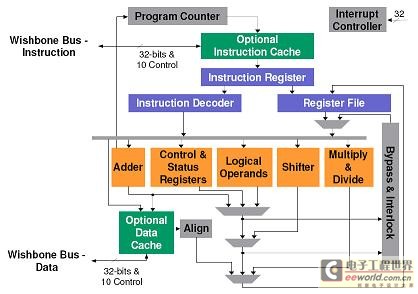

让我们来看看处理器核本身:LatticeMico32是基于哈佛总线结构的RISC架构的微处理器(图2)。 RISC体系结构提供了一个简单的指令集和更快的性能。哈佛总线架构提供独立的指令和数据总线,能够执行单周期指令。该处理器拥有32个通用寄存器,可处理多达32个外部的中断。定制的处理器可以插入乘法器或桶形移位器,以及不同的调试功能。

图2 LatticeMico32:一个可配置的RISC处理器核

Mico32可以用于各种存储系统,同时使用内嵌存储器用于存储指令和数据。内嵌存储器可以建立一个本地哈佛结构,并允许单周期访问指令和数据。对于更大的存储器需求,处理器通过一个仲裁器连接到其他的存储器模块或接口。这可以是用FPGA的存储器资源来实现的 “片上”存储器,或接口至外部存储器,诸如SSRAM、Flash和DRAM。处理所有访问协议至外部存储器的合适接口模块是由MSB提供的。提供可选的指令和数据高速缓存,能够配置成各种选择(高速缓存的大小,高速缓存块的大小等等)。

通过一个开放源码Wishbone总线接口,该处理器连接到各种外围元件。针对快速周转周期,图形用户界面可以轻松和快速地创建处理器平台。除了标准存储器控制器,这可能包括各种接口,不仅支持I2C、通用IO、定时器,UART以及SPI,还能支持更复杂的模块,如PCI接口或TriSpeed以太网MAC。

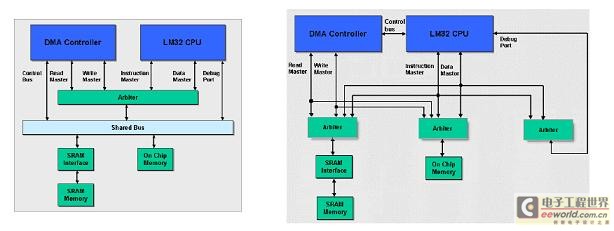

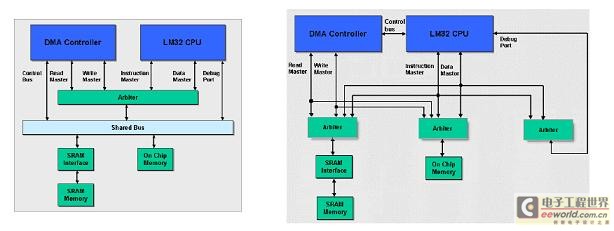

直接存储器访问(DMA)控制器是可用的,添加主器件(master)至Wishbone总线,以免除处理器的数据传输工作。这也允许有DMA功能的外设高效地直接传输数据到存储系统,从而节省了片上总线的带宽。

除了外围元件和DMA,用户可以自定义仲裁方案。总线结构产生器支持主器件(master)方和从器件(Slave)方的总线仲裁。如果能够满足系统性能的要求,主器件方总线仲裁提供了一个简单的低成本解决方案。然而,如果在设计中有多个总线主器件和多个从器件,在任何时间主器件方总线仲裁限制与单总线主器件通信。在许多设计中,通过两个或两个以上的总线主器件同时与独立的从器件进行通信,从器件方仲裁改进了性能。图3展示了可用的仲裁方案。

图3 仲裁方案

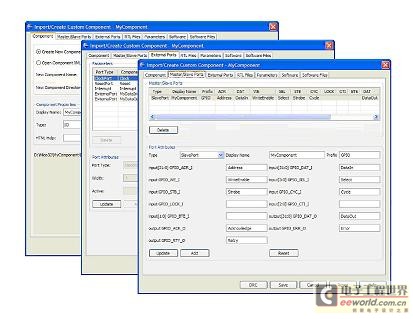

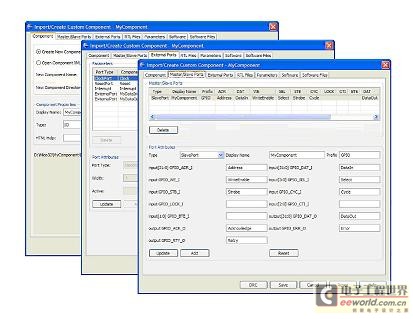

用户还可以创建自己的基于Wishbone总线的外设元件,然后通过整合到MSB自动连接到总线。因此,LatticeMico32的架构提供了两种可能性:第一,人们可以创建定制的元件,将它放人MSB中的可用元件列表(图4)。第二,可以构建出所谓的Passthru元件,可以将Wishbone接口引出到核的外面,因此,用户可以在FPGA的其他部分添加任何逻辑块。

图4 创建定制的外围组件

这些配置选项能够针对不同的应用定制LatticeMico32。带宽范围从小的和片内或片外存储器面积优化的控制器到具有多个接口的全功能平台,以及访问更大的存储器(可能是片外)。从FPGA访问其他的逻辑模块还允许处理器系统和FPGA专用模块之间的密切互动,以便进一步改进性能。取消了传统上使用并行于FPGA的外部控制器的复杂访问机制。

形成这种趋势有几个方面的原因。首先,数据流应用更适合可编程硬件,同时嵌入式微处理器更适合于执行控制流的应用。第二,要改变设计时,嵌入式处理器呈现更大的灵活性。最后,用软核的嵌入式微处理器消除了处理器过时的风险。从传统上而言,对嵌入式FPGA微处理器有一些限制,包括成本,速度和设计性能。随着工艺技术和设计技术的进步,这些限制正在不断改善,现在设计人员更有可能在他们的应用中考虑使用嵌入式FPGA微处理器。

与过去相比,现成的微处理器已经大大比嵌入式微处理器便宜。但是,今天的低成本FPGA被证明是一个节约成本的解决方案。如果设计中已经使用了FPGA,处理器可以整合到现有的FPGA架构,节省了分立器件或新的FPGA成本。设计周期也是一个重要的因素。将硬件与微处理器子系统构成相关的架构并进行实施能有多快?编写,测试和在微处理器上调试运行的代码需要多久?在过去几年中,在整体功能和易用性方面,针对嵌入式微处理器开发的软件工具也有了明显的改善。因此,现在可以在几分钟内运行设计,并且进行测试。产品上市的时间缩短了,因为现在用软件实现功能比硬件更快,更简单。

用现成的微处理器达到的性能有良好的历史记录。随着技术的改进,FPGA在功能和整个系统的速度方面有了显著的进步。由于现在的FPGA能够处理更大的带宽,嵌入式处理器对于许多设计有很大的吸引力。此外,由于FPGA与其他专用模块的紧密配合,软IP核的扩展性提供了一个系统接口,就性能和吞吐量方面而言,现在一个片上处理器可以提供卓越的设计方案。

当评估诸如LatticeMico32这样的特殊处理器时,使用嵌入式软处理器的优点非常清楚。

一个典型的嵌入式处理器子系统

让我们来看看一个典型的嵌入式处理器子系统,例如,LatticeMico32软处理器。该处理器需要有能与外界通信的功能,因此通常核连接到一个片上总线系统,在此情况下是WISHBONE开放源代码总线。然后还需要一个存储系统,用来保存处理器程序代码以及处理器核使用的数据。对外部通信而言,在一个典型的系统中有各种接口,从简单的通信接口和连接、更复杂的协议到应用中的专用硬件模块。现在该处理器总线架构需要连接外设和存储器系统。一个典型的系统如图1所示。

图1 典型的嵌入式RISC处理器子系统

让我们来看看处理器核本身:LatticeMico32是基于哈佛总线结构的RISC架构的微处理器(图2)。 RISC体系结构提供了一个简单的指令集和更快的性能。哈佛总线架构提供独立的指令和数据总线,能够执行单周期指令。该处理器拥有32个通用寄存器,可处理多达32个外部的中断。定制的处理器可以插入乘法器或桶形移位器,以及不同的调试功能。

图2 LatticeMico32:一个可配置的RISC处理器核

Mico32可以用于各种存储系统,同时使用内嵌存储器用于存储指令和数据。内嵌存储器可以建立一个本地哈佛结构,并允许单周期访问指令和数据。对于更大的存储器需求,处理器通过一个仲裁器连接到其他的存储器模块或接口。这可以是用FPGA的存储器资源来实现的 “片上”存储器,或接口至外部存储器,诸如SSRAM、Flash和DRAM。处理所有访问协议至外部存储器的合适接口模块是由MSB提供的。提供可选的指令和数据高速缓存,能够配置成各种选择(高速缓存的大小,高速缓存块的大小等等)。

通过一个开放源码Wishbone总线接口,该处理器连接到各种外围元件。针对快速周转周期,图形用户界面可以轻松和快速地创建处理器平台。除了标准存储器控制器,这可能包括各种接口,不仅支持I2C、通用IO、定时器,UART以及SPI,还能支持更复杂的模块,如PCI接口或TriSpeed以太网MAC。

直接存储器访问(DMA)控制器是可用的,添加主器件(master)至Wishbone总线,以免除处理器的数据传输工作。这也允许有DMA功能的外设高效地直接传输数据到存储系统,从而节省了片上总线的带宽。

除了外围元件和DMA,用户可以自定义仲裁方案。总线结构产生器支持主器件(master)方和从器件(Slave)方的总线仲裁。如果能够满足系统性能的要求,主器件方总线仲裁提供了一个简单的低成本解决方案。然而,如果在设计中有多个总线主器件和多个从器件,在任何时间主器件方总线仲裁限制与单总线主器件通信。在许多设计中,通过两个或两个以上的总线主器件同时与独立的从器件进行通信,从器件方仲裁改进了性能。图3展示了可用的仲裁方案。

图3 仲裁方案

用户还可以创建自己的基于Wishbone总线的外设元件,然后通过整合到MSB自动连接到总线。因此,LatticeMico32的架构提供了两种可能性:第一,人们可以创建定制的元件,将它放人MSB中的可用元件列表(图4)。第二,可以构建出所谓的Passthru元件,可以将Wishbone接口引出到核的外面,因此,用户可以在FPGA的其他部分添加任何逻辑块。

图4 创建定制的外围组件

这些配置选项能够针对不同的应用定制LatticeMico32。带宽范围从小的和片内或片外存储器面积优化的控制器到具有多个接口的全功能平台,以及访问更大的存储器(可能是片外)。从FPGA访问其他的逻辑模块还允许处理器系统和FPGA专用模块之间的密切互动,以便进一步改进性能。取消了传统上使用并行于FPGA的外部控制器的复杂访问机制。

嵌入式 FPGA 总线 Verilog DSP 连接器 仿真 uClinux 相关文章:

- 嵌入式系统的定义与发展历史(11-15)

- 嵌入式系统亲密接触(11-22)

- 嵌入式系统设计中的USB OTG方案(02-01)

- 嵌入式线控驾驶系统开发过程中设计和测试考虑(02-02)

- 一个典型的嵌入式系统设计和实现 (02-02)

- DDR SDRAM在嵌入式系统中的应用(02-07)