语音/数据/媒体网络时代需要的基础设施DSP

时间:11-26

来源:互联网

点击:

语音/数据/媒体网络的兴起要求高性能与高速 IO 完美结合。本文将探讨如何选择可满足上述要求的 DSP,提供低成本解决方案

多媒体内容随着总流量的增长而变得日益丰富,这为设备制造商带来了前所未有的工程设计挑战与机遇。他们必须制造出新一代能够处理持续急速上升的汇聚流量的设备,该汇聚流量不同于过去主导基础局端设计范例的语音与数据流量。

这种变革是上世纪70年代计算机革命以来的多重趋势引发的。

● 从纯语音流量到语音与数据流量的转变。这一趋势在数十年前就已开始了,现在仍在继续。

● 多媒体流量,特别是流媒体,加入现有的语音与数据流量。电信运营商转向提供语音、视频与数据服务的“三重播放业务”可充分证实这一发展趋势。

● 从固定地址服务到家庭服务再到移动服务的演进。有线基础局端中从语音到数据再到媒体的演进现在正在无线领域悄然进行。

● 上述三个趋势推动了另一趋势的发展:从电路交换传输到基于数据包的传输的演进,特别是对因特网协议(IP)流量。

在语音通信时代,电信信号处理无非是回声消除、数据调制解调器的线路调节以及在交换电路上进行数据调制/解调的信号处理。目前,对音频、视频和数据流进行数字编码/解码以及压缩/解压缩的算法就有数十种之多。简言之,电信基础局端不仅仅是要处理更多的数据,而且要实现信号处理量的指数级增长以实时处理大量数据。

显而易见,要实现信号处理量的指数级增长需要大幅提高性能。一种方法是仅加快数字信号处理器(DSP)的时钟速度。但这种解决方案不是长久之计,主要原因如下:首先,芯片时钟速度有限;其次,流量负载呈指数级而非线性增长,即使在最高时钟速度下,也将很快无法满足性能要求。另一个根本问题是基础局端设备采用机架安装,对尺寸和散热都有严格的要求。在机架尺寸不变(缩小尺寸除外)的情况下,高时钟速度带来的高散热最终也会使仅提高时钟速度这一方法不可行。将来,电路板性能的提升会受到其功耗预算、楼宇的使用年限与位置以及安装基础局端设备的机架等的限制。

提高性能

电信设计工程师面临着一个巨大的挑战。他们必须在更小的板级空间内提供更出色的性能、增加通道密度、处理日益多样化的媒体阵列,同时保持通信的灵活性与低成本特性。

为应对这些挑战,DSP一直在改进。从芯片设计人员的角度,这意味着要将上述趋势转化为特定的 IC 特性与架构。

同时实现高性能与低功耗目标的最佳策略是在低电压芯片上采用优化的处理引擎及高效 I/O 处理尽可能多的数据。

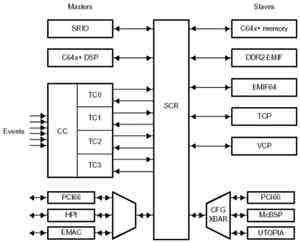

处理不断增多的原始数据量要求极高的性能与高效的片上数据传输能力。从架构上讲,这可通过交换中心资源 (SCR) 连接处理元件(DSP CPU、DSP 外设、协处理器加速器以及内部存储器)得以实现,即具有主从单元的纵横制架构。例如,德州仪器的TMS320C6455 DSP 采用的就是这种架构,如图 1 所示。

图1 TMS320C645x器件结构图

SCR左边的任一主单元均可直接与 SCR 右边的从单元相连。主单元包括 DSP 的 CPU、串行高速 IO (SRIO)、四个传输控制器 (TC)以及将三个主外设(PCI、HPI 与 EMAC)连接至 SCR 的纵横制端口。从单元包括 DSP 存储器、DDR 存储器接口、Turbo 协处理器 (TCP)、Viterbi 协处理器 (VCP) 以及将多个外设连接至 SCR 的纵横制端口。

这种架构既快速又高效,因为 SCR 使主从单元之间实现了真正的同时数据传输。例如,PCI 至 DDR EMIF 的连接独立于 PCI 166 至 DSP CPU 的连接。数据完全是并行传输。当多个主单元访问同一个从单元时,SCR 执行判优。同时系统设计人员可以通过对主单元的优先级别进行编程来施加某些控制。

架构要求

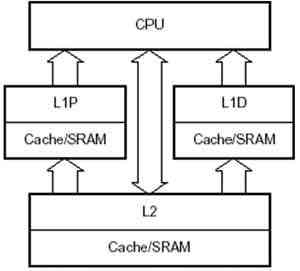

在执行算法时,CPU与存储器之间的指令和数据传输至关重要。在如图2所示的 TMS320C6455 DSP的存储器系统中,可通过使用256位宽的数据总线并在CPU与存储器之间的内部直接存储器存取(DMA)架构上创建两层高速缓存来优化数据传输。

图2 TMS320C64x+内部存储器

另一个架构要求是高效片上处理引擎。一种高效的方法是集成片上协处理器,以加速要求高性能的特定功能。例如,MS320C6455 DSP就集成了Viterbi协处理器(VCP)与Turbo协处理器 (TCP),如图1所示。

片上处理工作完成后,开发人员仍需将大量数据从芯片传输至电路板上,最终传输到电信传输介质上。显然应选择高速IO,但考虑到上述的异构架构,确定哪种处理方法最佳就会变得复杂。

最佳解决方案是为片内板级接口提供多种高性能IO接口。SRIO是异构多处理器器件间通信的最佳选择,因为其高吞吐消息传递方案可实现95%的带宽利用率(4x 串行双向链路可达10Gb/s)。

当然,外部存储器传输最好采用 32位DDR2存储器控制器;同样,连接片外器件最好采用66MHz的PCI总线;处理板上或板外IP流量的最好选择1Gb/s以太网媒体接入控制器 (EMAC);电信专用的通用测试与操作PHY接口则可充分满足ATM (UTOPIA 2)连接的 需求。

虽然 DSP处理能力随着具有更强并行能力以及其他高级特性的新架构的推出而显著提高,但电路板设计人员还可通过将多个DSP高效集成到单个电路板来获取更明显的改善。使用 SRIO 快速连接大大简化了这项工作,因为从DSP软件的角度,DSP之间的数据流处理与单个DSP内的数据流处理并没有很大的差异。

多媒体内容随着总流量的增长而变得日益丰富,这为设备制造商带来了前所未有的工程设计挑战与机遇。他们必须制造出新一代能够处理持续急速上升的汇聚流量的设备,该汇聚流量不同于过去主导基础局端设计范例的语音与数据流量。

这种变革是上世纪70年代计算机革命以来的多重趋势引发的。

● 从纯语音流量到语音与数据流量的转变。这一趋势在数十年前就已开始了,现在仍在继续。

● 多媒体流量,特别是流媒体,加入现有的语音与数据流量。电信运营商转向提供语音、视频与数据服务的“三重播放业务”可充分证实这一发展趋势。

● 从固定地址服务到家庭服务再到移动服务的演进。有线基础局端中从语音到数据再到媒体的演进现在正在无线领域悄然进行。

● 上述三个趋势推动了另一趋势的发展:从电路交换传输到基于数据包的传输的演进,特别是对因特网协议(IP)流量。

在语音通信时代,电信信号处理无非是回声消除、数据调制解调器的线路调节以及在交换电路上进行数据调制/解调的信号处理。目前,对音频、视频和数据流进行数字编码/解码以及压缩/解压缩的算法就有数十种之多。简言之,电信基础局端不仅仅是要处理更多的数据,而且要实现信号处理量的指数级增长以实时处理大量数据。

显而易见,要实现信号处理量的指数级增长需要大幅提高性能。一种方法是仅加快数字信号处理器(DSP)的时钟速度。但这种解决方案不是长久之计,主要原因如下:首先,芯片时钟速度有限;其次,流量负载呈指数级而非线性增长,即使在最高时钟速度下,也将很快无法满足性能要求。另一个根本问题是基础局端设备采用机架安装,对尺寸和散热都有严格的要求。在机架尺寸不变(缩小尺寸除外)的情况下,高时钟速度带来的高散热最终也会使仅提高时钟速度这一方法不可行。将来,电路板性能的提升会受到其功耗预算、楼宇的使用年限与位置以及安装基础局端设备的机架等的限制。

提高性能

电信设计工程师面临着一个巨大的挑战。他们必须在更小的板级空间内提供更出色的性能、增加通道密度、处理日益多样化的媒体阵列,同时保持通信的灵活性与低成本特性。

为应对这些挑战,DSP一直在改进。从芯片设计人员的角度,这意味着要将上述趋势转化为特定的 IC 特性与架构。

同时实现高性能与低功耗目标的最佳策略是在低电压芯片上采用优化的处理引擎及高效 I/O 处理尽可能多的数据。

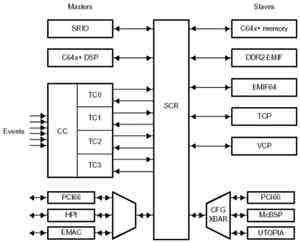

处理不断增多的原始数据量要求极高的性能与高效的片上数据传输能力。从架构上讲,这可通过交换中心资源 (SCR) 连接处理元件(DSP CPU、DSP 外设、协处理器加速器以及内部存储器)得以实现,即具有主从单元的纵横制架构。例如,德州仪器的TMS320C6455 DSP 采用的就是这种架构,如图 1 所示。

图1 TMS320C645x器件结构图

SCR左边的任一主单元均可直接与 SCR 右边的从单元相连。主单元包括 DSP 的 CPU、串行高速 IO (SRIO)、四个传输控制器 (TC)以及将三个主外设(PCI、HPI 与 EMAC)连接至 SCR 的纵横制端口。从单元包括 DSP 存储器、DDR 存储器接口、Turbo 协处理器 (TCP)、Viterbi 协处理器 (VCP) 以及将多个外设连接至 SCR 的纵横制端口。

这种架构既快速又高效,因为 SCR 使主从单元之间实现了真正的同时数据传输。例如,PCI 至 DDR EMIF 的连接独立于 PCI 166 至 DSP CPU 的连接。数据完全是并行传输。当多个主单元访问同一个从单元时,SCR 执行判优。同时系统设计人员可以通过对主单元的优先级别进行编程来施加某些控制。

架构要求

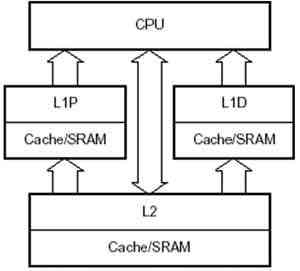

在执行算法时,CPU与存储器之间的指令和数据传输至关重要。在如图2所示的 TMS320C6455 DSP的存储器系统中,可通过使用256位宽的数据总线并在CPU与存储器之间的内部直接存储器存取(DMA)架构上创建两层高速缓存来优化数据传输。

图2 TMS320C64x+内部存储器

另一个架构要求是高效片上处理引擎。一种高效的方法是集成片上协处理器,以加速要求高性能的特定功能。例如,MS320C6455 DSP就集成了Viterbi协处理器(VCP)与Turbo协处理器 (TCP),如图1所示。

片上处理工作完成后,开发人员仍需将大量数据从芯片传输至电路板上,最终传输到电信传输介质上。显然应选择高速IO,但考虑到上述的异构架构,确定哪种处理方法最佳就会变得复杂。

最佳解决方案是为片内板级接口提供多种高性能IO接口。SRIO是异构多处理器器件间通信的最佳选择,因为其高吞吐消息传递方案可实现95%的带宽利用率(4x 串行双向链路可达10Gb/s)。

当然,外部存储器传输最好采用 32位DDR2存储器控制器;同样,连接片外器件最好采用66MHz的PCI总线;处理板上或板外IP流量的最好选择1Gb/s以太网媒体接入控制器 (EMAC);电信专用的通用测试与操作PHY接口则可充分满足ATM (UTOPIA 2)连接的 需求。

虽然 DSP处理能力随着具有更强并行能力以及其他高级特性的新架构的推出而显著提高,但电路板设计人员还可通过将多个DSP高效集成到单个电路板来获取更明显的改善。使用 SRIO 快速连接大大简化了这项工作,因为从DSP软件的角度,DSP之间的数据流处理与单个DSP内的数据流处理并没有很大的差异。

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)