用EZ-USB实现TMS320C6X与主机数据传输

时间:11-25

来源:互联网

点击:

DSP主要应用于实时和大数据量的信号处理系统,当它与主机进行通信时,数据交换速度和接口的复杂度是系统的一个关键性能指标,因此迫切需要一种能满足高速、简洁要求的通信方式,通用串行总线USB以其高速和内置电源两个特性,对提高设备的性能、降低成本和系统小型化具有很大的实际意义,本系统采用高速DSP(TMS320C6713),配合嵌入USB2.0协议的芯片CY7C68013,实现小规模主从式系统中主机与DSP间的高速通信。经实际验证,系统运行可靠,是一种比较好的高速数据传输与处理的解决方案。

1 USB控制芯片

Cypress公司的EZ-USB FX2系列芯片是最早符合USB2.0协议的微控制器之一。它集成了收发器(transceiver)、串行接口引擎(SIE),增强型的8051内核以及可编程的外围接口(GPIF),FX2系列芯片独特的结构使数据传输速度最高可达到56Mbps,最大程度地满足了USB2.0的带宽。

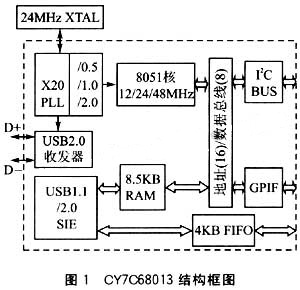

CY7C68013的结构框图如图1所示。

FX2的端点缓冲区分为大小两组:EP0、EP1(IN)、EP1(OUT)是小端点,大小为64字节,只能由CPU来存取,不能由外部逻辑连接;EP2、EP4、EP6、EP8是大的可配置的端点,EP2和EP4默认为OUT端点,EP6和EP8默认为IN端点。FX2为其大端点提供多种缓冲方式,满足了传输中高带宽的要求,传输过程中EZ-USB FX2从IN缓冲区中读取上传到主机的数据,在OUT缓冲区中写入供外部处理器读取的数据。它具备全速(12Mbps)和高速(480Mbps)两种传输速率,并具有USB协议所规定的4种传输模式,即控制传输(control mode)、中断传输(interrupt mode)、块传输(bulk mode)和等时传输(isochronous mode)。

2 系统硬件构架

2.1 USB与DSP的硬件连接

系统中选用的数字信号处理器是TI公司发布的C6000浮点系列中的TMS320C6713,其峰值处理速度能达到1350MFLOPS(百万次浮点操作/s)。外设资源包括直接存储器访问控制器(DMA),外部存储器接口(EMIF)、串行口、扩展总线或主机口、定时器等。系统中利用其EMIF口,连接可编程逻辑芯片CPLD来扩展USB控制接口。CY7C68013能非常灵活地实现与DSP或MCU的接口。当其作为主设备时,通用可编程接口(GPIF)具有可编程的波形描述符和配置寄存器,能够轻易地兼容绝大多数总线标准,当其作为从设备时,4KB的大容量FIFO用于数据缓冲,简化了接口的外部硬件设计,可采用同步或异步方式与主设备(如ASIC,DSP等)连接。

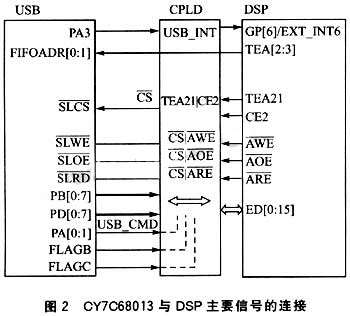

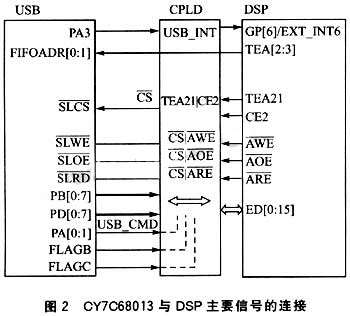

在本方案中,使其作为从设备,选用了Slave FIFOs,异步读/写,在这种模式下,DSP可以像读/写普通FIFO一样对CY7C68013内部的多层缓冲FIFO进行读/写。主要信号连接如图2所示。主机(PC)发出命令的同时也由PA3提供中断触发信号给DSP的外部中断引脚6(EXT_INT6)。其上升沿被检测到以后,DSP就进入相应中断服务程序,开始处理USB的传输,DSP通过CPLD对CY7C68013进行读写及使能控制,“或”组合逻辑满足严格的时序要求,FLAGB和FLAGC是CY7C68013内部FIFO的空、满状态标志,PA[0:1]表示PC发送的命令类型。这些信息在CPLD内部整合到数据总线ED[0:15],DSP开始传输数据包前对其提取判断,TMS320C6713对CY7C68013内部端点(EP)的选择,是通过地址线TEA[2:3]来实现。

2.2 系统总体结构设计

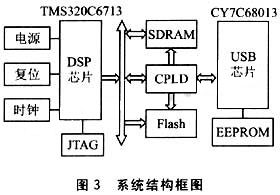

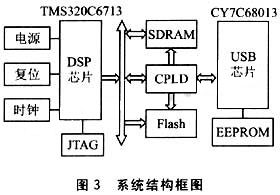

根据上述硬件通信模式搭建基于PC、USB、DSP的主从式系统,当系统上电完成各模块固件配置和硬件初始化后,可由PC发出控制命令,以外部信号触发DSP进入相应的中断处理程序,自动完成数据流USB下载、DSB处理和USB回传的多次循环过程;PC显示处理后的结果。系统总体结构框图如图3所示。

DSP芯片通过片中的EMIF(包括4个存储空间CE[0:3])为SDRAM,Flash等器件提供接口。SDRAM为同步存储器件,EMIF有专门的控制线和时钟与它进行无缝连接(CE0空间)。这里SDRAM用做数据存储器。

对于C6000系列DSP,调试好的应用程序需要固化,以便系统上电时能自动加载运行。方案中采用Flash启动引导模式,位于EMIF异步接口CE1空间。

复位电路提供系统上电和工作电压异常时的自动复位及人工控制复位。时钟电路为DSP处理模块提供时钟信号。

USB的接口电路提供PC与DSP的高速数据传输通道,接口芯片通过CPLD与外部处理器DSP相连,置于EMIF的CE2空间(通信模式如前所述)。

3 通信模块软件设计

Cypress公司为了简化和加速用户使用EZ-USB FX2芯片进行USB外设的开发过程,特别设计了CY7C68013的开发板,并带有一个开发包,内含一个USB外设所必需的驱动程序、应用程序以及一个完整的固件程序的框架,这个框架可以执行EZ-USB芯片的初始化,USB标准设备请求的处理和USB挂起电源管理服务;用户只需要提供一个USB描述符表,添加其他端点接受和发送数据的通信代码,以及控制外围电路的程序代码即可。

1 USB控制芯片

Cypress公司的EZ-USB FX2系列芯片是最早符合USB2.0协议的微控制器之一。它集成了收发器(transceiver)、串行接口引擎(SIE),增强型的8051内核以及可编程的外围接口(GPIF),FX2系列芯片独特的结构使数据传输速度最高可达到56Mbps,最大程度地满足了USB2.0的带宽。

CY7C68013的结构框图如图1所示。

FX2的端点缓冲区分为大小两组:EP0、EP1(IN)、EP1(OUT)是小端点,大小为64字节,只能由CPU来存取,不能由外部逻辑连接;EP2、EP4、EP6、EP8是大的可配置的端点,EP2和EP4默认为OUT端点,EP6和EP8默认为IN端点。FX2为其大端点提供多种缓冲方式,满足了传输中高带宽的要求,传输过程中EZ-USB FX2从IN缓冲区中读取上传到主机的数据,在OUT缓冲区中写入供外部处理器读取的数据。它具备全速(12Mbps)和高速(480Mbps)两种传输速率,并具有USB协议所规定的4种传输模式,即控制传输(control mode)、中断传输(interrupt mode)、块传输(bulk mode)和等时传输(isochronous mode)。

2 系统硬件构架

2.1 USB与DSP的硬件连接

系统中选用的数字信号处理器是TI公司发布的C6000浮点系列中的TMS320C6713,其峰值处理速度能达到1350MFLOPS(百万次浮点操作/s)。外设资源包括直接存储器访问控制器(DMA),外部存储器接口(EMIF)、串行口、扩展总线或主机口、定时器等。系统中利用其EMIF口,连接可编程逻辑芯片CPLD来扩展USB控制接口。CY7C68013能非常灵活地实现与DSP或MCU的接口。当其作为主设备时,通用可编程接口(GPIF)具有可编程的波形描述符和配置寄存器,能够轻易地兼容绝大多数总线标准,当其作为从设备时,4KB的大容量FIFO用于数据缓冲,简化了接口的外部硬件设计,可采用同步或异步方式与主设备(如ASIC,DSP等)连接。

在本方案中,使其作为从设备,选用了Slave FIFOs,异步读/写,在这种模式下,DSP可以像读/写普通FIFO一样对CY7C68013内部的多层缓冲FIFO进行读/写。主要信号连接如图2所示。主机(PC)发出命令的同时也由PA3提供中断触发信号给DSP的外部中断引脚6(EXT_INT6)。其上升沿被检测到以后,DSP就进入相应中断服务程序,开始处理USB的传输,DSP通过CPLD对CY7C68013进行读写及使能控制,“或”组合逻辑满足严格的时序要求,FLAGB和FLAGC是CY7C68013内部FIFO的空、满状态标志,PA[0:1]表示PC发送的命令类型。这些信息在CPLD内部整合到数据总线ED[0:15],DSP开始传输数据包前对其提取判断,TMS320C6713对CY7C68013内部端点(EP)的选择,是通过地址线TEA[2:3]来实现。

2.2 系统总体结构设计

根据上述硬件通信模式搭建基于PC、USB、DSP的主从式系统,当系统上电完成各模块固件配置和硬件初始化后,可由PC发出控制命令,以外部信号触发DSP进入相应的中断处理程序,自动完成数据流USB下载、DSB处理和USB回传的多次循环过程;PC显示处理后的结果。系统总体结构框图如图3所示。

DSP芯片通过片中的EMIF(包括4个存储空间CE[0:3])为SDRAM,Flash等器件提供接口。SDRAM为同步存储器件,EMIF有专门的控制线和时钟与它进行无缝连接(CE0空间)。这里SDRAM用做数据存储器。

对于C6000系列DSP,调试好的应用程序需要固化,以便系统上电时能自动加载运行。方案中采用Flash启动引导模式,位于EMIF异步接口CE1空间。

复位电路提供系统上电和工作电压异常时的自动复位及人工控制复位。时钟电路为DSP处理模块提供时钟信号。

USB的接口电路提供PC与DSP的高速数据传输通道,接口芯片通过CPLD与外部处理器DSP相连,置于EMIF的CE2空间(通信模式如前所述)。

3 通信模块软件设计

Cypress公司为了简化和加速用户使用EZ-USB FX2芯片进行USB外设的开发过程,特别设计了CY7C68013的开发板,并带有一个开发包,内含一个USB外设所必需的驱动程序、应用程序以及一个完整的固件程序的框架,这个框架可以执行EZ-USB芯片的初始化,USB标准设备请求的处理和USB挂起电源管理服务;用户只需要提供一个USB描述符表,添加其他端点接受和发送数据的通信代码,以及控制外围电路的程序代码即可。

DSP 总线 USB Cypress 收发器 CPLD MCU 电路 电压 电源管理 相关文章:

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)