TMS320C5000性能介绍-数字信号处理器

时间:11-25

来源:互联网

点击:

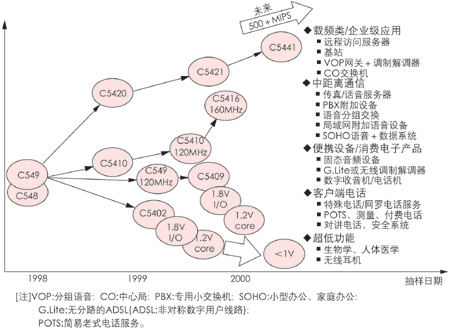

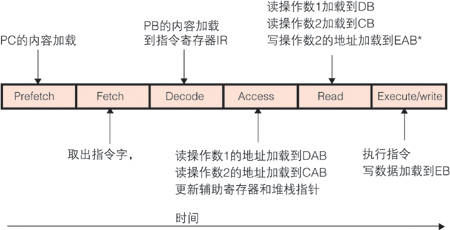

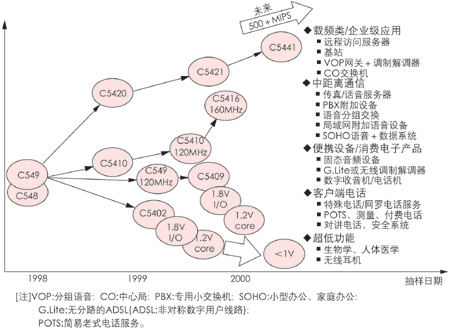

TMS320C54x是目前普遍使用的定点DSP芯片。它的特点是功耗很低(在100MIPS时为60mW),可用于数字蜂窝通信、个人通信系统、寻呼机、个人数字助理(PDA)、ATM(异步传输模式)交换机、数字无线通信、调制解调器等领域。图1表示了C54x的发展过程及应用领域。

图1 TMS320C5000性能发展状况及应用领域

TMS320系列的同一代芯片具有相同的CPU结构,但根据市场的不同需要,形成新的存储器与外设的不同组合,产生了多种派生器件。

TMS320C54x关键特性

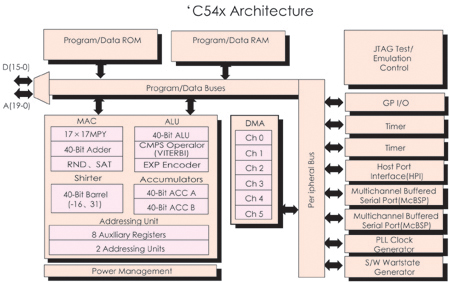

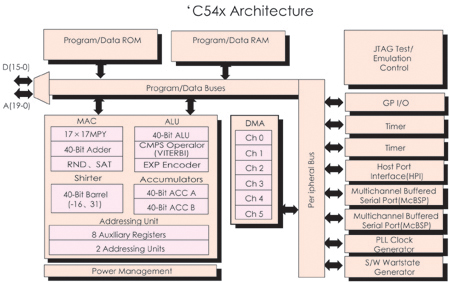

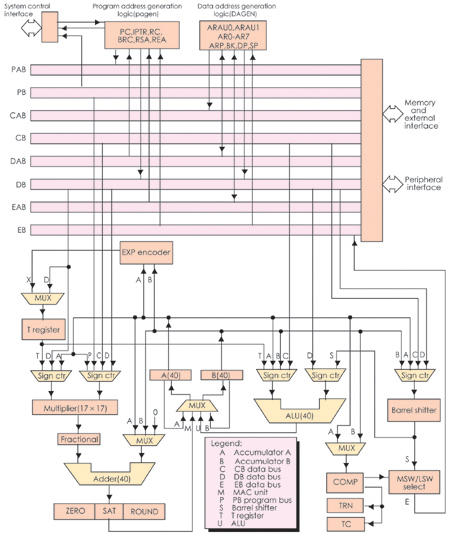

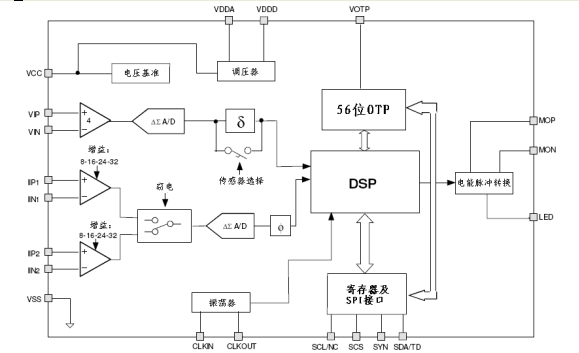

图2是C54x功能结构图,它的主要性能如下:

图2 TMS320C54x功能结构框图

⒈ CPU

先进的多总线结构:一组程序总线(PAB、PB),三组数据总线(CAB、CB,DAB、DB,EAB、EB)

40位的数学逻辑单元(ALU):包括40位的桶形移位寄存器和两个独立的40位累加器

17 17位并行乘法器和40位专用加法器,单周期完成乘法/累加(MAC)

适于Viterbi运算的比较、选择、存储单元(CSSU)

指数编码器,可在单周期内计算(40位)累加器中数值的指数

两个地址产生器,包括八个辅助寄存器和两个的算术单元

⒉ 存储器

可寻址存储空间达192K字(程序、数据及I/O各64 64bit),C548还可扩展程序存储器(8兆字)

典型C5400芯片存储器

⒊ 片内外设

软件可编程等待状态产生器

可编程的块交换

片内锁相环时钟产生器

禁止外部总线的控制机制

⒋ 指令集

重复单条指令与重复指令块

存储器块移动指令

32位数运算指令

可同时读取2或3个操作数的指令

具有并行保存和并行加载的算术指令

条件保存指令

⒌ 功耗控制

IDLE1、IDLE2和IDLE3指令可控制其进入降功耗模式

可控制是否输出CLKOUT信号

⒍ IEEE标准的1149.1边界扫描逻辑接口

TMS320C54x结构概述

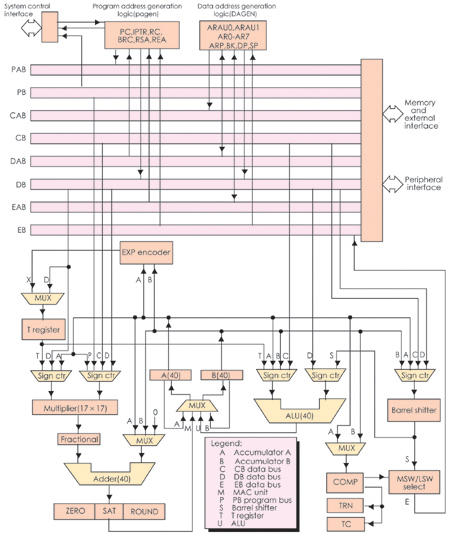

'C54x由中央处理器CPU、存储器和片内外设组成,采用哈佛结构,有独立的程序空间、数据空间和I/O空间。图3是'C54x的内部硬件框图。

对所有的'C54x器件来说,图中下半部所示的中央处理单元(CPU)是通用的。

总线结构

一组程序总线(PAB、PB)和三组数据总线CAB、CB,DAB、DB,EAB、EB)将内部各部件联系起来。

图3 TMS320C54x内部硬件框图

PB- 程序总线,传送程序代码或存在程序空间的数据;

CB、DB、EB- 数据总线,连接CPU、数据地址产生逻辑、程序地址产生逻辑、片内外设及存储器等各部件;

CB和DB- 传送从存储器读出的数据,即“读”操作使用的数据总线;

EB-传送向存储器写入的数据,即"写"操作使用的数据总线;

PAB、CAB、DAB、EAB- 各对应的地址总线;

图4 ALU功能框图

中央处理单元(CPU)

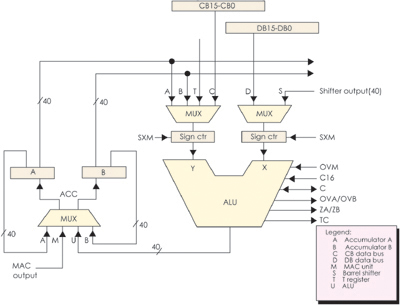

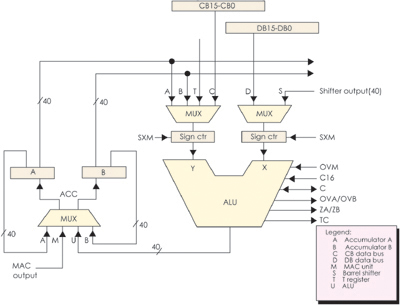

ALU:算术逻辑运算单元

主要由40位ALU和两个40位累加器(ACCA和ACCB)组成,如图4所示。

ALU和两个累加器用来完成40位二进制补码的算术运算,也能完成布尔运算。当状态寄存储器ST1的C16位置1时,可做两个16位ALU,同时完成两个16位运算。

输入:

16位立即数;

来自数据存储器的16

位数;

来自暂存器T的16位

数;

来自数据存储器读出

的两个16位数;

来自数据存储器读出

的一个32位数;

来自累加器(A和B)

的40位数;

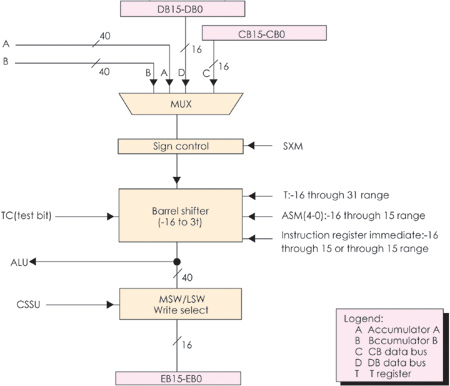

图5 桶形移位器功能框图

输出:ALU的40位输出被送往累加器A或B。

图6 乘/加模块功能方框图

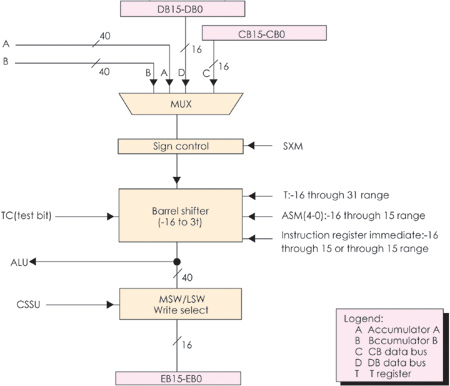

桶形移位器:将输入数据左移0~31位或右移0~16位,经常用作数字定标、位提取、扩展算术和溢出保护等操作。 输入40位:来自累加器或经DB、CB的 数据存储器;

输出40位:连到ALU或经EB连到数据存储器;

所移位数由指令中移位字段、ST1的ASM字段或T寄存器指定移位位数决定。

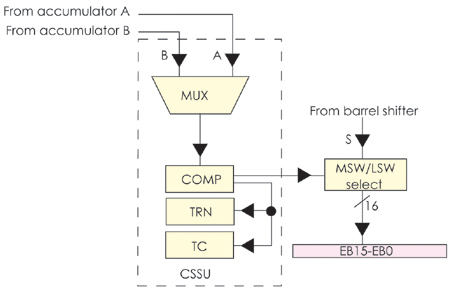

图7 比较、选择与保存单元(CSSU)功能框图

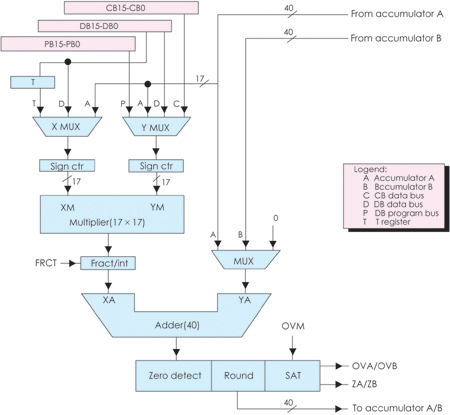

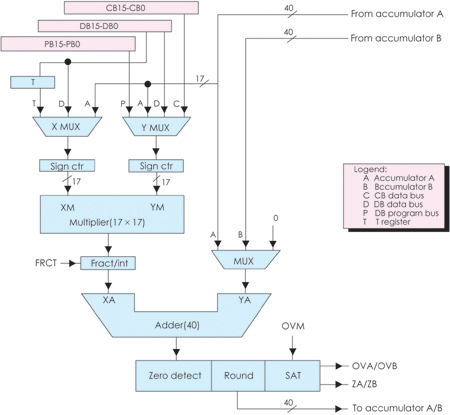

乘/加模块:由乘法器、加法器、输入数据的符号控制逻辑、小数控制逻辑、零检测、舍入、溢出/饱和逻辑和16位暂存寄存器T等组成。乘法器和ALU在一个指令周期内共同完成(17 17补码)乘/加(40位)运算,且可并行地作ALU运算,这些功能可用来做Euclidean距离及LMS滤波等复杂运算。乘/加模块功能方框图如图6所示。

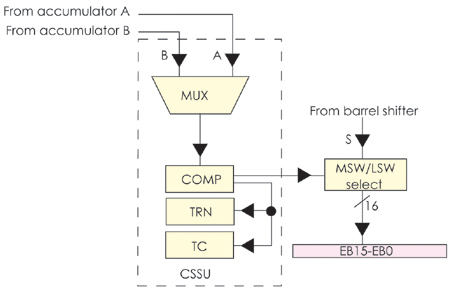

比较、选择与保存单元(CSSU):可以完成累加器的高位字和低位字之间的最大值比较(CMPS指令)。另一功能是利用优化的片内硬件资源完成数据通信、模式识别等领域中经常用到的Viterbi蝶形运算。

图8 指数编码器

指数编码器:用于支持单周期指令EXP的专用硬件,如图8所示。

累加器中数值的指数值,以二进制补码形式(-8~31)存放于暂存器T中;

CPU状态和控制寄存器:

'C54x共有3个16位状态和控制寄存器(PMST、ST0、ST1)它们都是存储器映象寄存器,可以方便地写入数据、或由数据存储器对它们加载。

内部存储器

·'C54x的存储器分为三个可独立选择的空间:程序空间、数据空间和I/O空间;

·'C54x的片内存储器包括ROM和RAM,其中RAM又可分为SARAM和DARAM:SARAM为单寻址寄存储器,DARAM为双寻址寄存储器(一周期内可以访问两次)。

ROM一般配置成程序存储空间,用于存放要执行的指令、系数表等固定操作数。也可以部分地安排到数据存储空间,由PMST的状态位 和DROM决定;RAM 一般安排到数据存储空间,存放执行指令所要用的数据。但也可以安排到程序空间,由PMST的状态位OVLY决定。不同'C54x系列内部存储器配置各不相同。

'C54x的寻址方式

TMS320C54x的指令可能含有1个存储器操作数(指令说明中用Smem表示),也可能有2个存储器操作数(指令说明中用Xmem、Ymem表示),分别称为单存储器操作数和双存储器操作数。单存储器操作数有7种寻址方式,它们是:

立即寻址: 操作数(常数)含在指

令中;

绝对寻址: 指令中含有操作数

的16位地址;

累加器寻址: 操作数地址在累加器

中(A);

直接寻址: 指令中含有操作数

地址的低7 位;

间接寻址: 操作数的地址在辅

助寄存器中,支持倒

位序寻址、循环寻址

等功能;

存储器映像的寄存器寻址:

访问存储器映像寄存器,

又不影响DP或SP;

堆栈寻址: 访问堆栈;

双存储器操作数支持一些特殊指令:

如MAC、FIR等复杂

指令。

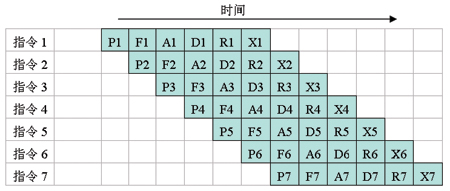

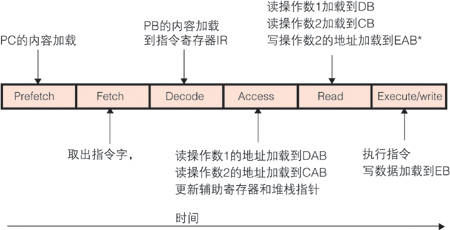

'C54x的六级指令流水线

'C54x CPU的指令流水线有六级,每个周期有六条指令在工作,它们处于整个执行过程的不同阶段,如图9所示。

图9 流水线不同工作阶段操作内容

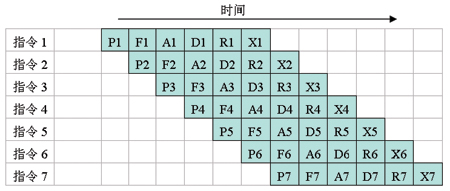

流水线的工作全部为单字指令连续执行时(理想情况)如图10 所示。

图10 流水线正常工作时做业情况

图1 TMS320C5000性能发展状况及应用领域

TMS320系列的同一代芯片具有相同的CPU结构,但根据市场的不同需要,形成新的存储器与外设的不同组合,产生了多种派生器件。

TMS320C54x关键特性

图2是C54x功能结构图,它的主要性能如下:

图2 TMS320C54x功能结构框图

⒈ CPU

先进的多总线结构:一组程序总线(PAB、PB),三组数据总线(CAB、CB,DAB、DB,EAB、EB)

40位的数学逻辑单元(ALU):包括40位的桶形移位寄存器和两个独立的40位累加器

17 17位并行乘法器和40位专用加法器,单周期完成乘法/累加(MAC)

适于Viterbi运算的比较、选择、存储单元(CSSU)

指数编码器,可在单周期内计算(40位)累加器中数值的指数

两个地址产生器,包括八个辅助寄存器和两个的算术单元

⒉ 存储器

可寻址存储空间达192K字(程序、数据及I/O各64 64bit),C548还可扩展程序存储器(8兆字)

典型C5400芯片存储器

⒊ 片内外设

软件可编程等待状态产生器

可编程的块交换

片内锁相环时钟产生器

禁止外部总线的控制机制

⒋ 指令集

重复单条指令与重复指令块

存储器块移动指令

32位数运算指令

可同时读取2或3个操作数的指令

具有并行保存和并行加载的算术指令

条件保存指令

⒌ 功耗控制

IDLE1、IDLE2和IDLE3指令可控制其进入降功耗模式

可控制是否输出CLKOUT信号

⒍ IEEE标准的1149.1边界扫描逻辑接口

TMS320C54x结构概述

'C54x由中央处理器CPU、存储器和片内外设组成,采用哈佛结构,有独立的程序空间、数据空间和I/O空间。图3是'C54x的内部硬件框图。

对所有的'C54x器件来说,图中下半部所示的中央处理单元(CPU)是通用的。

总线结构

一组程序总线(PAB、PB)和三组数据总线CAB、CB,DAB、DB,EAB、EB)将内部各部件联系起来。

图3 TMS320C54x内部硬件框图

PB- 程序总线,传送程序代码或存在程序空间的数据;

CB、DB、EB- 数据总线,连接CPU、数据地址产生逻辑、程序地址产生逻辑、片内外设及存储器等各部件;

CB和DB- 传送从存储器读出的数据,即“读”操作使用的数据总线;

EB-传送向存储器写入的数据,即"写"操作使用的数据总线;

PAB、CAB、DAB、EAB- 各对应的地址总线;

图4 ALU功能框图

中央处理单元(CPU)

ALU:算术逻辑运算单元

主要由40位ALU和两个40位累加器(ACCA和ACCB)组成,如图4所示。

ALU和两个累加器用来完成40位二进制补码的算术运算,也能完成布尔运算。当状态寄存储器ST1的C16位置1时,可做两个16位ALU,同时完成两个16位运算。

输入:

16位立即数;

来自数据存储器的16

位数;

来自暂存器T的16位

数;

来自数据存储器读出

的两个16位数;

来自数据存储器读出

的一个32位数;

来自累加器(A和B)

的40位数;

图5 桶形移位器功能框图

输出:ALU的40位输出被送往累加器A或B。

图6 乘/加模块功能方框图

桶形移位器:将输入数据左移0~31位或右移0~16位,经常用作数字定标、位提取、扩展算术和溢出保护等操作。 输入40位:来自累加器或经DB、CB的 数据存储器;

输出40位:连到ALU或经EB连到数据存储器;

所移位数由指令中移位字段、ST1的ASM字段或T寄存器指定移位位数决定。

图7 比较、选择与保存单元(CSSU)功能框图

乘/加模块:由乘法器、加法器、输入数据的符号控制逻辑、小数控制逻辑、零检测、舍入、溢出/饱和逻辑和16位暂存寄存器T等组成。乘法器和ALU在一个指令周期内共同完成(17 17补码)乘/加(40位)运算,且可并行地作ALU运算,这些功能可用来做Euclidean距离及LMS滤波等复杂运算。乘/加模块功能方框图如图6所示。

比较、选择与保存单元(CSSU):可以完成累加器的高位字和低位字之间的最大值比较(CMPS指令)。另一功能是利用优化的片内硬件资源完成数据通信、模式识别等领域中经常用到的Viterbi蝶形运算。

图8 指数编码器

指数编码器:用于支持单周期指令EXP的专用硬件,如图8所示。

累加器中数值的指数值,以二进制补码形式(-8~31)存放于暂存器T中;

CPU状态和控制寄存器:

'C54x共有3个16位状态和控制寄存器(PMST、ST0、ST1)它们都是存储器映象寄存器,可以方便地写入数据、或由数据存储器对它们加载。

内部存储器

·'C54x的存储器分为三个可独立选择的空间:程序空间、数据空间和I/O空间;

·'C54x的片内存储器包括ROM和RAM,其中RAM又可分为SARAM和DARAM:SARAM为单寻址寄存储器,DARAM为双寻址寄存储器(一周期内可以访问两次)。

ROM一般配置成程序存储空间,用于存放要执行的指令、系数表等固定操作数。也可以部分地安排到数据存储空间,由PMST的状态位 和DROM决定;RAM 一般安排到数据存储空间,存放执行指令所要用的数据。但也可以安排到程序空间,由PMST的状态位OVLY决定。不同'C54x系列内部存储器配置各不相同。

'C54x的寻址方式

TMS320C54x的指令可能含有1个存储器操作数(指令说明中用Smem表示),也可能有2个存储器操作数(指令说明中用Xmem、Ymem表示),分别称为单存储器操作数和双存储器操作数。单存储器操作数有7种寻址方式,它们是:

立即寻址: 操作数(常数)含在指

令中;

绝对寻址: 指令中含有操作数

的16位地址;

累加器寻址: 操作数地址在累加器

中(A);

直接寻址: 指令中含有操作数

地址的低7 位;

间接寻址: 操作数的地址在辅

助寄存器中,支持倒

位序寻址、循环寻址

等功能;

存储器映像的寄存器寻址:

访问存储器映像寄存器,

又不影响DP或SP;

堆栈寻址: 访问堆栈;

双存储器操作数支持一些特殊指令:

如MAC、FIR等复杂

指令。

'C54x的六级指令流水线

'C54x CPU的指令流水线有六级,每个周期有六条指令在工作,它们处于整个执行过程的不同阶段,如图9所示。

图9 流水线不同工作阶段操作内容

流水线的工作全部为单字指令连续执行时(理想情况)如图10 所示。

图10 流水线正常工作时做业情况

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)