基于DDS与USB的通信对抗教学演示系统

时间:11-25

来源:互联网

点击:

4 系统的设计实现

4.1 干扰模块的设计

干扰模块原理图如图5所示。在干扰模块的设计中,选用了常用的DDS芯片AD9854与FPGA相结合的方式来产生干扰频率。为了实现干扰信号功率的可控制,拟在DDS输出的信号加上衰减器。采用计算机通过USB芯片来控制干扰模式的选择和干扰信号参数的选择。DDS产生的信号先通过低通滤波再放大,目的是为抑制杂散信号。

在跟踪式干扰中,FPGA接收电子侦察所获得的通信信号,引导DDS产生同频的干扰信号。在非跟踪式干扰中,由计算机控制产生单频干扰、扫频干扰以及随机调频噪声等样式的干扰信号,这些干扰信号和原跳频信号在合路器合路输出,送给跳频接收机,以此来检验跳频通信对这些干扰样式的抗干扰能力。

4.2控制模块的设计

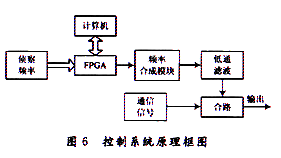

在系统的整体设计过程中,非常重要的部分就是对于整个实验系统的控制。系统的整体控制模块原理框图如图6所示。

从图中可以看出,干扰模块中的FPGA芯片,在系统控制中起着核心作用。在该模块中,FPGA主要完成4个方面的任务:

(1)实现与电子侦察模块的实时通信,不断地接收侦察模块送来的跳频信号信息,并立即做出相应的反应。

(2)实现与计算机主机的通信,控制USB芯片的读写程序,随时接收主机发出的控制指令,并完成相应的功能。

(3)实现对DDS芯片的控制,根据需要选择DDS不同的工作模式。

(4)实现对衰减器的控制,根据主机的命令选择不同的频率幅度。

5 结 语

通过对实际硬件电路的分析与调试,系统实现了计算机对USB芯片的控制、FPGA对DDS芯片的控制、侦察模块与干扰模块的互连通信以及各类干扰方式的可控实现。在进行实际试验时,通过对不同干扰方式的效果进行比较,还可以选择出对跳频电台通信最有效的干扰方式,并且对今后研究实战形式的跳频侦察干扰系统具有一定的实际参考意义。

4.1 干扰模块的设计

干扰模块原理图如图5所示。在干扰模块的设计中,选用了常用的DDS芯片AD9854与FPGA相结合的方式来产生干扰频率。为了实现干扰信号功率的可控制,拟在DDS输出的信号加上衰减器。采用计算机通过USB芯片来控制干扰模式的选择和干扰信号参数的选择。DDS产生的信号先通过低通滤波再放大,目的是为抑制杂散信号。

在跟踪式干扰中,FPGA接收电子侦察所获得的通信信号,引导DDS产生同频的干扰信号。在非跟踪式干扰中,由计算机控制产生单频干扰、扫频干扰以及随机调频噪声等样式的干扰信号,这些干扰信号和原跳频信号在合路器合路输出,送给跳频接收机,以此来检验跳频通信对这些干扰样式的抗干扰能力。

4.2控制模块的设计

在系统的整体设计过程中,非常重要的部分就是对于整个实验系统的控制。系统的整体控制模块原理框图如图6所示。

从图中可以看出,干扰模块中的FPGA芯片,在系统控制中起着核心作用。在该模块中,FPGA主要完成4个方面的任务:

(1)实现与电子侦察模块的实时通信,不断地接收侦察模块送来的跳频信号信息,并立即做出相应的反应。

(2)实现与计算机主机的通信,控制USB芯片的读写程序,随时接收主机发出的控制指令,并完成相应的功能。

(3)实现对DDS芯片的控制,根据需要选择DDS不同的工作模式。

(4)实现对衰减器的控制,根据主机的命令选择不同的频率幅度。

5 结 语

通过对实际硬件电路的分析与调试,系统实现了计算机对USB芯片的控制、FPGA对DDS芯片的控制、侦察模块与干扰模块的互连通信以及各类干扰方式的可控实现。在进行实际试验时,通过对不同干扰方式的效果进行比较,还可以选择出对跳频电台通信最有效的干扰方式,并且对今后研究实战形式的跳频侦察干扰系统具有一定的实际参考意义。

USB 电子 FPGA 电路 CMOS ADC 电压 Altera DSP ADI 比较器 DAC 电流 收发器 相关文章:

- USB设备的调试与测试技巧(11-11)

- USB系统结构与应用设计(01-18)

- 基于C8051F320 USB接口的数据采集存储电路(01-18)

- 基于USB的CAN总线适配器设计(01-21)

- 带USB接口的短信收发最小系统设计(01-23)

- 基于USB总线和Aduc831单片机的数据采集系统的设计(01-25)