基于DSP E1-16XS的硬件开发平台设计

时间:11-15

来源:互联网

点击:

|

|

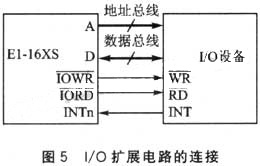

图5中,IORD和IOWR为I/O访问时的读控制信号和写控制信号,分别连接到I/O设计的读和写控制端;I/O设备的中断输出信号INT连接到DSP的中断输入信号INTn。E1-16XS提供了最多7个外部中断输入可供连接。

|

3 PCB板设计要点

设计好电路图后,就可以设计PCB板了,在系统中,E1-16XS的片内工作频率可以达到150MHz以上,系统总线频率也接近100MHz,因此,在PCB设计过程中,应该遵循高频电路设计的基本原则。首先应注意电源的质量与分配,其次要注意信号线和时钟线的分布。

(1)电源质量与分配

在设计PCB板时,给各个单元电路提供高质量的电源,会使系统的稳定性大幅度提高。一般应在电源进入印刷电路板的位置和靠近各器件的电源引脚处加上几十~几百μf的电容,以滤除电源噪声,还要注意在器件的电源和地之间加上0.01μF-0.1μF左右的电容,用来滤除元器件工作时产生的高频噪声,由于双面PCB板电源采用电源总线的方式,受到电路板面积的限制,一般存在较大的直流电阻,所以为了提高系统的稳定性,通常采用多层板,一般专门拿出两层,作为电源层和地层,而不在其上布信号线。低阻抗的电源层也可以像地层一样作为高频信号的返回通路,可以有效地降低噪声。

(2)同类型信号线的分布

在设计PCB时,对于处理器的输入输出信号中的数据线、地址线等相同类型的线应该成组、平行分布、并保持它们之间的长短差异不要太大,采用这种方式布线的既可以减少干扰,增加系统的稳定性,还可以简化布线,使PCB板的外观美观。

(3)时钟信号线的分布

较高频的时钟信号是电路板的关键信号,频率越高的时钟其布线要求也越高,布线时应使时钟源到负载的联线尽量短,线应尽量宽,不同时钟之间,时钟与其他信号之间避免平行走线。信号负载较多时,在一个驱动器上不要驱动其他时钟信号,保持时钟信号的质量良好。

结语

该精简开发板具有最小化的功能,用户仅仅需要在Flash里预先烧写Boot监控程序,就可以进行应用程序的调试和下载,该开发板具有良好的扩展性,通过I/O扩展接口为户的硬件扩展提供了很多的便利。用户可以在不更改Boot监控程序的前提下对该精简开发板进行硬件功能(串口、USB、可编程器件等)的扩充。

嵌入式 DSP 电子 MCU CMOS 电路 总线 看门狗 电压 振荡器 PCB 电路图 电容 电阻 USB 相关文章:

- 嵌入式系统的定义与发展历史(11-15)

- 嵌入式系统亲密接触(11-22)

- 嵌入式系统设计中的USB OTG方案(02-01)

- 嵌入式线控驾驶系统开发过程中设计和测试考虑(02-02)

- 一个典型的嵌入式系统设计和实现 (02-02)

- DDR SDRAM在嵌入式系统中的应用(02-07)