一款32位嵌入式CPU的定点加法器设计

时间:11-05

来源:互联网

点击:

从CPU的指令执行频率上看,算术逻辑单元、程序计数器、协处理器是CPU中使用频率最多的模块,而加法器正是这些模块的核心部件,几乎所有的关键路径都与之有关,因而设计一种通用于这些模块的加法器是整个CPU设计中关键的一步。为此,笔者根据32位CPU的400MHz主频的要求,结合CPU流水线结构,借鉴各种算法成熟的加法器,提出一种电路设计简单、速度快、功耗低、版图面积小的32位改进定点加法器的设计方案。

1 设计思路

对于高性能CPU中使用的加法器,速度显然是第一位的,所以考虑采用并行计算的方法,并且在电路的设计上采用少量的器件来获得速度上的巨大提升。从面积角度出发,链式进位加法器(Ripple-Carry Adder)的器件最少,面积最小,版图工作量也最小,可是由于加法器的高位进位要等待低位的运算结束后才能得到,所以没有办法在速度上达到要求。鉴于此,采用类似于链式加法器的结构。

首先从进位选择加法器(Carry-Select Adder)得到提示,将32位加法器一分为二,分为低16位加法器和高16位加法器,再将低16位加法器的进位输出作为选择信号,用于选择高16位加法器的和及第27位的进位输出(这个进位输出要在溢出逻辑判断中使用,而普通的加法器则不用产生进位)。通过这样的处理,将一个32位的加法器简化就成了两个16位的加法器,如图1所示。

另外,从超前进位加法器(Carry-Look-Ahead Adder)获得提示,在超前进位加法器中引入中间变量G和P用于加速进位链的速度。而G和P在逻辑表达式上与前一级的进位无关,只与每一级的操作数输入有关,而且它们又是构成本级进位的必要部分。在微处理器的数据通道上,数据传输是并行进行的,即两个32位操作数几乎同一时间到达加法器。所以,G和P不论是加法器的最低位还是加法器的最高位,几乎都可以在相同的时间内得到,因而在进位链上就可以借鉴这个特点加速进位的传递。以一个四位加法器为例,有如下的逻辑推导过程:

令上式中P1P2P3P4为Pgroup,G1P2P3P4+G2P3P4+G3P4+G4为Ggroup,如果将32位加法器划分为若干的小块,则每一个小块都可以有自己相对应的Ggroup和Pgroup。由此可知对于整个加法器的时延来说,关键路径的时延总值可以由三部分组成:①产生Ggroup和Pgroup的时延;②进位传递逻辑上的器件时延;③加法器进位链上的导线时延。对于这三类时延,时延①与时延(②+③)存在重叠的部分,于是使这两类时延合理衔接,可以使得进位链上的逻辑级数最小,从而使得电路上的传输时延达到最小。

2 具体实现

2.1 4位加法器模块的实现

在具体的电路设计中,先将32位数据通道划分成了高低两部分,然后以4位为单元划分成更小的模块。这些模块在结构上是基本一致的,但在功能上要完成本模块四组操作数(A[k:k+3]和B[k:k+3])与进位Ck的加法运算,并要产生模块的中间变量Ggroup和Pgroup的运算。

对于单一的每一位,定义它的G和P分别为:Gi=AiBi, Pi=Ai⊕Bi,加法器的和SUMi=Ai⊕Bi⊕Ci-1=Pi⊕Ci-1,考虑到器件的实际驱动能力,结合加法器的另一个功能——减法运算,设计出如图2所示的带减法功能的一位加法器电路。

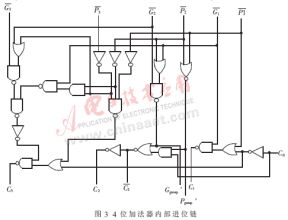

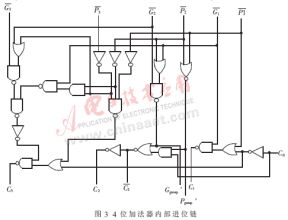

设计的4位加法器进位链如图3所示,除C0外,输入( i和

i和 i)都是由图2的一位加法器产生的,所有4位进位链Ci都按超前进位加法器连接方式直接接入相应位置。由此可以看出,进位信号到达各位的逻辑级数是相当的,只要在进位信号到达之前使所有的中间信号

i)都是由图2的一位加法器产生的,所有4位进位链Ci都按超前进位加法器连接方式直接接入相应位置。由此可以看出,进位信号到达各位的逻辑级数是相当的,只要在进位信号到达之前使所有的中间信号 i和

i和 i都能及时产生,就能及时得到每一位的和(SUM)。

i都能及时产生,就能及时得到每一位的和(SUM)。

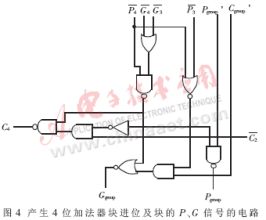

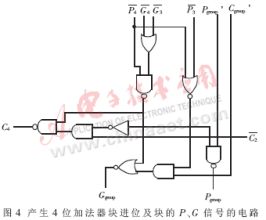

图4是产生4位加法器块进位及块的Ggroup和Pgroup信号的电路。借鉴于超前进位加法器的传递逻辑电路,可知并不是所有的4位加法器都需要向它的下一个模块传送进位信号,而只要产生传递进位所需的Ggroup和Pgroup信号即可。而有些位置,由于进位链设计的实际需要,只需要利用4位加法器模块产生的进位信号,而不必采用传递逻辑产生的进位信号,具体的情况还是有区别的。为了充分利用图3中产生的相关信号的复用,在进位信号C4的产生电路部分,进位链方向上的逻辑级数只有两级,可以说还是比较简单了。可是,综合前面所谈到的4位加法器的电路,可以发现有一些中间信号( i和

i和 i)的负载是不均衡的,如

i)的负载是不均衡的,如 2的负载比

2的负载比 3或

3或 4要重很多。所以在设计的时候,如果考虑到尽量降低版图的复杂程度,就要在面积上做出适当的牺牲,尽量以最大负载进行考虑,使得器件的设计符合时延上的要求;同时还要充分考虑到在深亚微米工艺条件下导线的时延问题,即设计的电路不但要考虑到所承受的器件的负载,而且还要结合版图设计中实际的导线负载,定出上述电路的合理尺寸。

4要重很多。所以在设计的时候,如果考虑到尽量降低版图的复杂程度,就要在面积上做出适当的牺牲,尽量以最大负载进行考虑,使得器件的设计符合时延上的要求;同时还要充分考虑到在深亚微米工艺条件下导线的时延问题,即设计的电路不但要考虑到所承受的器件的负载,而且还要结合版图设计中实际的导线负载,定出上述电路的合理尺寸。

1 设计思路

对于高性能CPU中使用的加法器,速度显然是第一位的,所以考虑采用并行计算的方法,并且在电路的设计上采用少量的器件来获得速度上的巨大提升。从面积角度出发,链式进位加法器(Ripple-Carry Adder)的器件最少,面积最小,版图工作量也最小,可是由于加法器的高位进位要等待低位的运算结束后才能得到,所以没有办法在速度上达到要求。鉴于此,采用类似于链式加法器的结构。

首先从进位选择加法器(Carry-Select Adder)得到提示,将32位加法器一分为二,分为低16位加法器和高16位加法器,再将低16位加法器的进位输出作为选择信号,用于选择高16位加法器的和及第27位的进位输出(这个进位输出要在溢出逻辑判断中使用,而普通的加法器则不用产生进位)。通过这样的处理,将一个32位的加法器简化就成了两个16位的加法器,如图1所示。

另外,从超前进位加法器(Carry-Look-Ahead Adder)获得提示,在超前进位加法器中引入中间变量G和P用于加速进位链的速度。而G和P在逻辑表达式上与前一级的进位无关,只与每一级的操作数输入有关,而且它们又是构成本级进位的必要部分。在微处理器的数据通道上,数据传输是并行进行的,即两个32位操作数几乎同一时间到达加法器。所以,G和P不论是加法器的最低位还是加法器的最高位,几乎都可以在相同的时间内得到,因而在进位链上就可以借鉴这个特点加速进位的传递。以一个四位加法器为例,有如下的逻辑推导过程:

令上式中P1P2P3P4为Pgroup,G1P2P3P4+G2P3P4+G3P4+G4为Ggroup,如果将32位加法器划分为若干的小块,则每一个小块都可以有自己相对应的Ggroup和Pgroup。由此可知对于整个加法器的时延来说,关键路径的时延总值可以由三部分组成:①产生Ggroup和Pgroup的时延;②进位传递逻辑上的器件时延;③加法器进位链上的导线时延。对于这三类时延,时延①与时延(②+③)存在重叠的部分,于是使这两类时延合理衔接,可以使得进位链上的逻辑级数最小,从而使得电路上的传输时延达到最小。

2 具体实现

2.1 4位加法器模块的实现

在具体的电路设计中,先将32位数据通道划分成了高低两部分,然后以4位为单元划分成更小的模块。这些模块在结构上是基本一致的,但在功能上要完成本模块四组操作数(A[k:k+3]和B[k:k+3])与进位Ck的加法运算,并要产生模块的中间变量Ggroup和Pgroup的运算。

对于单一的每一位,定义它的G和P分别为:Gi=AiBi, Pi=Ai⊕Bi,加法器的和SUMi=Ai⊕Bi⊕Ci-1=Pi⊕Ci-1,考虑到器件的实际驱动能力,结合加法器的另一个功能——减法运算,设计出如图2所示的带减法功能的一位加法器电路。

设计的4位加法器进位链如图3所示,除C0外,输入(

i和

i和 i)都是由图2的一位加法器产生的,所有4位进位链Ci都按超前进位加法器连接方式直接接入相应位置。由此可以看出,进位信号到达各位的逻辑级数是相当的,只要在进位信号到达之前使所有的中间信号

i)都是由图2的一位加法器产生的,所有4位进位链Ci都按超前进位加法器连接方式直接接入相应位置。由此可以看出,进位信号到达各位的逻辑级数是相当的,只要在进位信号到达之前使所有的中间信号 i和

i和 i都能及时产生,就能及时得到每一位的和(SUM)。

i都能及时产生,就能及时得到每一位的和(SUM)。

图4是产生4位加法器块进位及块的Ggroup和Pgroup信号的电路。借鉴于超前进位加法器的传递逻辑电路,可知并不是所有的4位加法器都需要向它的下一个模块传送进位信号,而只要产生传递进位所需的Ggroup和Pgroup信号即可。而有些位置,由于进位链设计的实际需要,只需要利用4位加法器模块产生的进位信号,而不必采用传递逻辑产生的进位信号,具体的情况还是有区别的。为了充分利用图3中产生的相关信号的复用,在进位信号C4的产生电路部分,进位链方向上的逻辑级数只有两级,可以说还是比较简单了。可是,综合前面所谈到的4位加法器的电路,可以发现有一些中间信号(

i和

i和 i)的负载是不均衡的,如

i)的负载是不均衡的,如 2的负载比

2的负载比 3或

3或 4要重很多。所以在设计的时候,如果考虑到尽量降低版图的复杂程度,就要在面积上做出适当的牺牲,尽量以最大负载进行考虑,使得器件的设计符合时延上的要求;同时还要充分考虑到在深亚微米工艺条件下导线的时延问题,即设计的电路不但要考虑到所承受的器件的负载,而且还要结合版图设计中实际的导线负载,定出上述电路的合理尺寸。

4要重很多。所以在设计的时候,如果考虑到尽量降低版图的复杂程度,就要在面积上做出适当的牺牲,尽量以最大负载进行考虑,使得器件的设计符合时延上的要求;同时还要充分考虑到在深亚微米工艺条件下导线的时延问题,即设计的电路不但要考虑到所承受的器件的负载,而且还要结合版图设计中实际的导线负载,定出上述电路的合理尺寸。

电路 相关文章:

- 基于P89C61x2/ISP1581的USB接口电路的设计(02-13)

- 行波管关断方式对应用系统可靠性的影响(06-24)

- 基于VME总线的RDC接口电路设计(06-29)

- 单芯片集成电路优化自适应转向大灯系统的设计 (07-12)

- 单片机应用系统的抗干扰技术(08-07)

- 基于FPGA的线阵CCD驱动器设计(11-26)