基于ARM Cortex-M3的嵌入式网络播放系统

时间:11-05

来源:互联网

点击:

随着网络应用的普及,为普通嵌入式系统增加网络功能,能更好满足消费者对网络资源的需求。这里采用基于ARM Cortex-M3的微控制器LM3S1138实现一种具备网络功能的播放终端系统,该系统不仅具有良好的播放效果,还可从网络音乐服务器上点播音乐并实时播放。

1 网络播放系统的设计方案

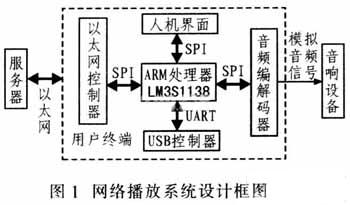

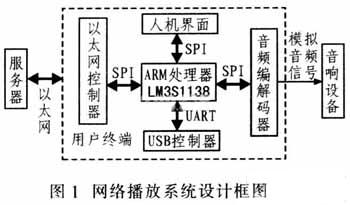

该网络播放系统由服务器、用户终端和音响设备组成。其中,服务器通过以太网提供音乐资源,用户终端通过网络下载音频数据再实现音频解码,音响设备实现音乐播放。图1给出该系统设计框图。

该系统设计采用基于ARM Cortex-M3的控制器LM3Sll38作为主控制器。该控制器改进了代码密度,减少中断延时,实现Thumb-2指令集,并具有更低功耗,适用于嵌入式微处理器;网络模块采用以太网控制器ENC602J28;音频编解码器采用VSl003,该器件拥有自主产权的DSP处理器核,具有高性能、低功耗等特性;并采用USB总线接口器件CH375扩展存储模块。支持海量存储。

将嵌入式实时操作系统μC/OS-II移植到主处理器上,实现多任务的调度管理。系统工作时,通过操作播放器上的配置按钮,设置服务器和用户终端的相关网络配置,点击播放器中的连接按钮,发送连接服务器请求,服务器收到用户终端的连接请求,验证终端帐号正确后开始网络连接,向用户传送点播的资源列表,用户终端在播放器界面显示列表,此时,用户可以选择点播的歌曲,然后将音乐文件下载到存储设备中,下载完毕后,服务器关闭网络连接,播放器就可播放已下载歌曲。

2 系统硬件模块设计

2.1 以太网接口

ENC28J60是独立的以太网控制器,采用业界标准的SPI串行接口,具有10 Mb/s SPI接口,符合IEEE802.3协议,内置10 Mb/s以太网物理层器件(PHY)及介质访问控制器(MAC)。另外,它还具有可编程8 KB双端口SRAM缓冲器,此缓冲存储器具有灵活可靠的数据管理机制,以高效方式进行信息包的存储、检索和修改,以减轻主控器件的内存负荷。

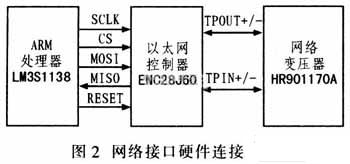

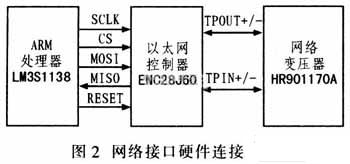

图2为网络接口硬件连接示意图。ENC28J60通过SPI总线实现与LM3Sll38的数据传输,CS为片选信号,SCLK为时钟信号,MOSI/MISO为数据传输串口。此外,ENC28J60还与网络变压器HR901l70A相连,引出刚45接口。

2.2音频接口

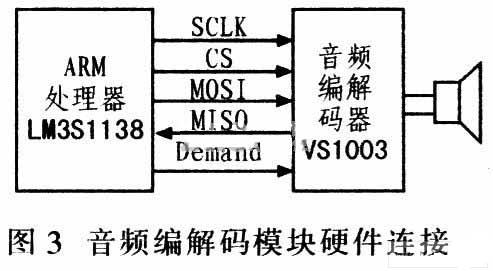

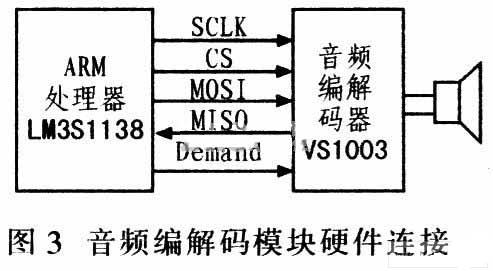

VSl003音频编解码器为VSl0XX系列第3代产品,包括MP3/WMA/MIDI解码和ADPCM编码2个单器件。其内置有高性能、低功耗的DSP处理核(VSDSP),工作内存,可供用户程序使用的5.5 KB RAM,串行SPI总线接口,高质量的采样频率可调的过采样D/A转换器以及16位的过采样A/D转换器。图3为音频编解码器模块硬件连接示意图,VSl003采用SPI总线与LM3Sll38实现通信。其中,SCLK为输入时钟,CS为片选信号,MOSI/MISO为数据串口,Demand为命令有效信号,VSl003外接音频输出设备。

2.3 USB控制接口

CH375是一款支持USB-HOST主机方式和USB-DE-VICE/SLAVE从设备方式的器件,主机端点输入和输出缓冲区各64字节,支持常用的12 Mb/s全速USB设备,支持USB设备的控制传输、批量传输、中断传输。内置固件处理海量存储设备的专用通讯协议,支持Bulk-Only传输协议和 SCSI,UFI,RBC或等效命令集的USB存储设备。

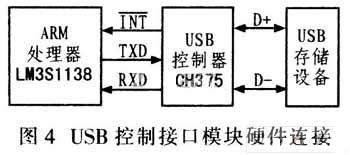

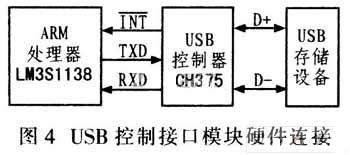

图4为USB控制接口模块硬件连接示意图,CH375通过UART串口与LM3S1138传输数据,*****为中断信号,TXD/RXD为数据传输串口,CH375连接USB存储设备。

3 系统软件设计

μC/OS-II是专门为嵌入式应用设计的实时操作系统内核,其具有以下优点:源代码公开,代码结构清晰,注释详尽,组织有条理,具有良好的可扩展性和可移植性,最多可以管理60个任务。该系统移植的μC/OS-II由用户层、中间件层、μC/OS-II源码层、μC/OS-II移植层和驱动库组成。用户层存放用户代码及设置,其中Main.c是用户编写任务处,Main.h定义堆栈大小及优先级;中间件层Middleware存放UART、 SPI等串口通信中间件和TCP/IP协议栈LwIP;μC/OS-II源码层Source存放μC/OS-II的源代码;μC/OS-II移植层 Port存放μC/OS-Ⅱ基于LM3S的移植代码,包括OS_CPU_C.C,OS_CPU_A.A,OS_CPU.C等3个必要文件;驱动库层是直接面向硬件设备层,它是硬件设备和应用程序之间的枢纽,直接与系统底层的硬件设备打交道,按照硬件设备的具体工作方式读写设备寄存器。将寄存器的数据与应用软件交互,ENC28J60、VSl003和CH375的驱动函数都在该层。

3.1网络驱动程序

本系统采用ENC28J60以太网控制器,需编写网络设备驱动程序,实现低层网络接口及硬件函数驱动。该驱动程序设计主要包含网卡的初始化和数据的发送接收。

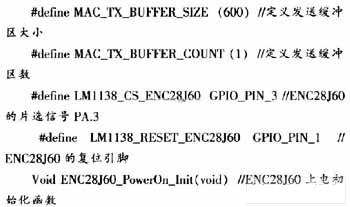

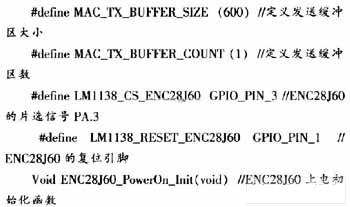

网卡初始化的驱动程序包括定义发送缓冲区大小、发送缓冲区数、ENC28J60的片选信号、ENC28J60的复位引脚以及网卡自检。具体程序代码如下:

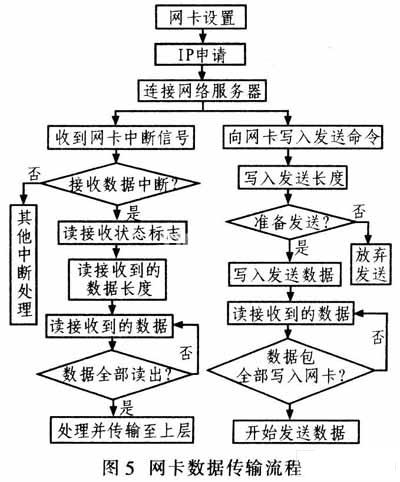

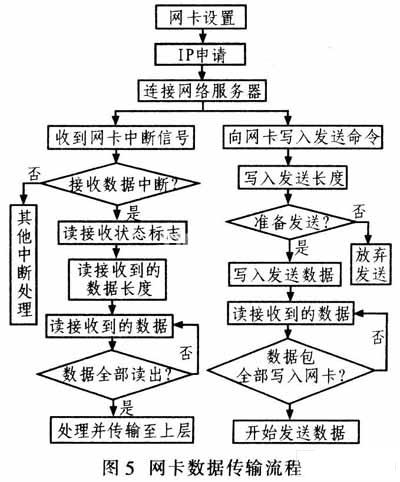

网卡数据传输的驱动程序包括申请IP地址,建立与服务器的连接,以及数据的接收和发送等,图5为其程序流程。

1 网络播放系统的设计方案

该网络播放系统由服务器、用户终端和音响设备组成。其中,服务器通过以太网提供音乐资源,用户终端通过网络下载音频数据再实现音频解码,音响设备实现音乐播放。图1给出该系统设计框图。

该系统设计采用基于ARM Cortex-M3的控制器LM3Sll38作为主控制器。该控制器改进了代码密度,减少中断延时,实现Thumb-2指令集,并具有更低功耗,适用于嵌入式微处理器;网络模块采用以太网控制器ENC602J28;音频编解码器采用VSl003,该器件拥有自主产权的DSP处理器核,具有高性能、低功耗等特性;并采用USB总线接口器件CH375扩展存储模块。支持海量存储。

将嵌入式实时操作系统μC/OS-II移植到主处理器上,实现多任务的调度管理。系统工作时,通过操作播放器上的配置按钮,设置服务器和用户终端的相关网络配置,点击播放器中的连接按钮,发送连接服务器请求,服务器收到用户终端的连接请求,验证终端帐号正确后开始网络连接,向用户传送点播的资源列表,用户终端在播放器界面显示列表,此时,用户可以选择点播的歌曲,然后将音乐文件下载到存储设备中,下载完毕后,服务器关闭网络连接,播放器就可播放已下载歌曲。

2 系统硬件模块设计

2.1 以太网接口

ENC28J60是独立的以太网控制器,采用业界标准的SPI串行接口,具有10 Mb/s SPI接口,符合IEEE802.3协议,内置10 Mb/s以太网物理层器件(PHY)及介质访问控制器(MAC)。另外,它还具有可编程8 KB双端口SRAM缓冲器,此缓冲存储器具有灵活可靠的数据管理机制,以高效方式进行信息包的存储、检索和修改,以减轻主控器件的内存负荷。

图2为网络接口硬件连接示意图。ENC28J60通过SPI总线实现与LM3Sll38的数据传输,CS为片选信号,SCLK为时钟信号,MOSI/MISO为数据传输串口。此外,ENC28J60还与网络变压器HR901l70A相连,引出刚45接口。

2.2音频接口

VSl003音频编解码器为VSl0XX系列第3代产品,包括MP3/WMA/MIDI解码和ADPCM编码2个单器件。其内置有高性能、低功耗的DSP处理核(VSDSP),工作内存,可供用户程序使用的5.5 KB RAM,串行SPI总线接口,高质量的采样频率可调的过采样D/A转换器以及16位的过采样A/D转换器。图3为音频编解码器模块硬件连接示意图,VSl003采用SPI总线与LM3Sll38实现通信。其中,SCLK为输入时钟,CS为片选信号,MOSI/MISO为数据串口,Demand为命令有效信号,VSl003外接音频输出设备。

2.3 USB控制接口

CH375是一款支持USB-HOST主机方式和USB-DE-VICE/SLAVE从设备方式的器件,主机端点输入和输出缓冲区各64字节,支持常用的12 Mb/s全速USB设备,支持USB设备的控制传输、批量传输、中断传输。内置固件处理海量存储设备的专用通讯协议,支持Bulk-Only传输协议和 SCSI,UFI,RBC或等效命令集的USB存储设备。

图4为USB控制接口模块硬件连接示意图,CH375通过UART串口与LM3S1138传输数据,*****为中断信号,TXD/RXD为数据传输串口,CH375连接USB存储设备。

3 系统软件设计

μC/OS-II是专门为嵌入式应用设计的实时操作系统内核,其具有以下优点:源代码公开,代码结构清晰,注释详尽,组织有条理,具有良好的可扩展性和可移植性,最多可以管理60个任务。该系统移植的μC/OS-II由用户层、中间件层、μC/OS-II源码层、μC/OS-II移植层和驱动库组成。用户层存放用户代码及设置,其中Main.c是用户编写任务处,Main.h定义堆栈大小及优先级;中间件层Middleware存放UART、 SPI等串口通信中间件和TCP/IP协议栈LwIP;μC/OS-II源码层Source存放μC/OS-II的源代码;μC/OS-II移植层 Port存放μC/OS-Ⅱ基于LM3S的移植代码,包括OS_CPU_C.C,OS_CPU_A.A,OS_CPU.C等3个必要文件;驱动库层是直接面向硬件设备层,它是硬件设备和应用程序之间的枢纽,直接与系统底层的硬件设备打交道,按照硬件设备的具体工作方式读写设备寄存器。将寄存器的数据与应用软件交互,ENC28J60、VSl003和CH375的驱动函数都在该层。

3.1网络驱动程序

本系统采用ENC28J60以太网控制器,需编写网络设备驱动程序,实现低层网络接口及硬件函数驱动。该驱动程序设计主要包含网卡的初始化和数据的发送接收。

网卡初始化的驱动程序包括定义发送缓冲区大小、发送缓冲区数、ENC28J60的片选信号、ENC28J60的复位引脚以及网卡自检。具体程序代码如下:

网卡数据传输的驱动程序包括申请IP地址,建立与服务器的连接,以及数据的接收和发送等,图5为其程序流程。

嵌入式 ARM Cortex 解码器 DSP USB 总线 变压器 LCD 相关文章:

- 嵌入式系统的定义与发展历史(11-15)

- 嵌入式系统亲密接触(11-22)

- 嵌入式系统设计中的USB OTG方案(02-01)

- 嵌入式线控驾驶系统开发过程中设计和测试考虑(02-02)

- 一个典型的嵌入式系统设计和实现 (02-02)

- DDR SDRAM在嵌入式系统中的应用(02-07)