基于单片机和CPLD的多路精确延时控制系统

时间:11-04

来源:互联网

点击:

4 系统软件设计

本系统软件设计包括CPUO单元、NO.1~NO.n输出单元及CPLD单元程序设计。由于对时间要求严格,采用汇编语言编写,信号输出由中断程序完成,由于中断响应过程、现场保护以及中断后必要的设置条件检测需要时间,所以软件必须通过容余指令(比如NOP)的延时,可保证counter0输出和控制信号延时起点在同一时刻。

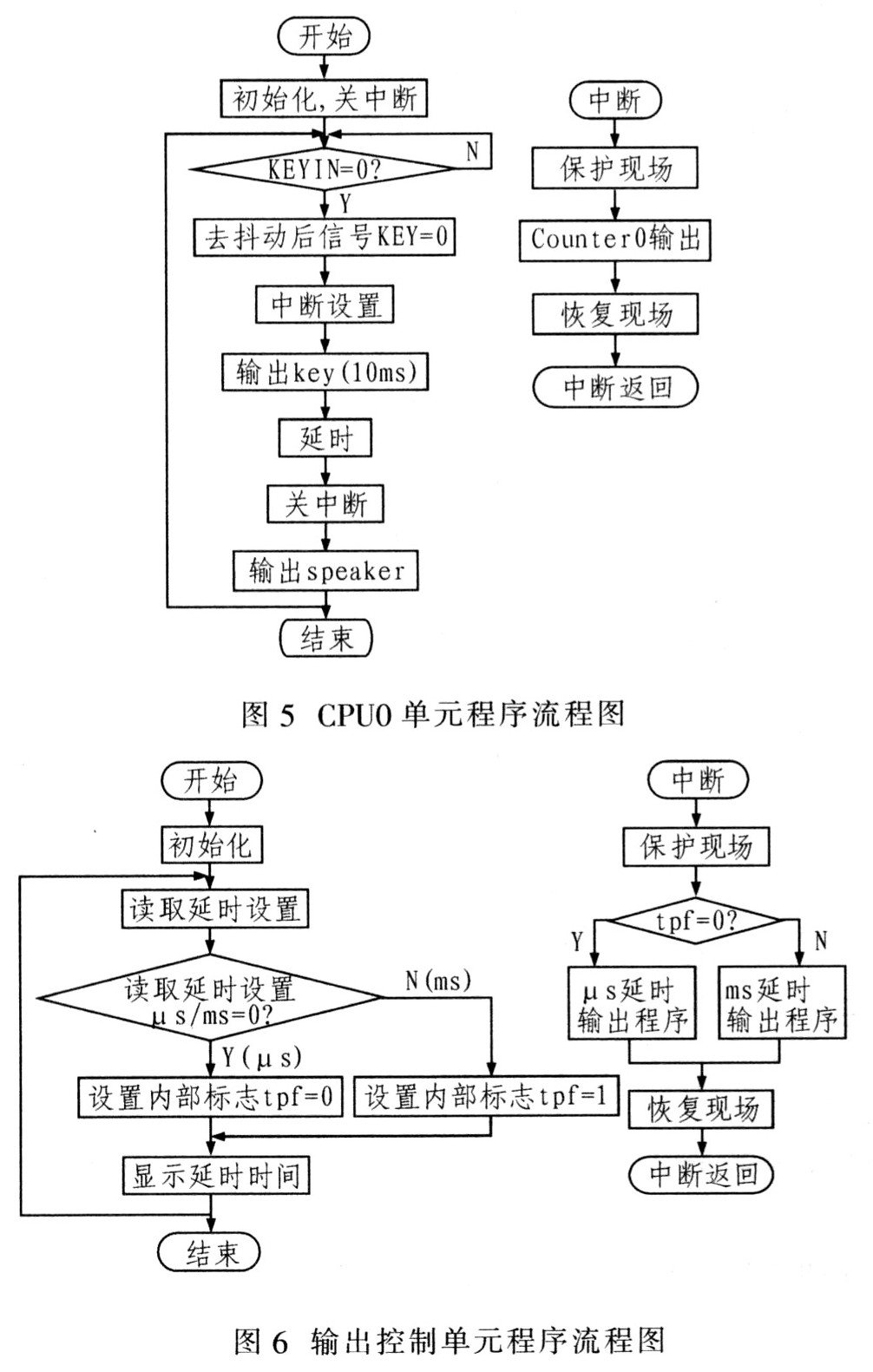

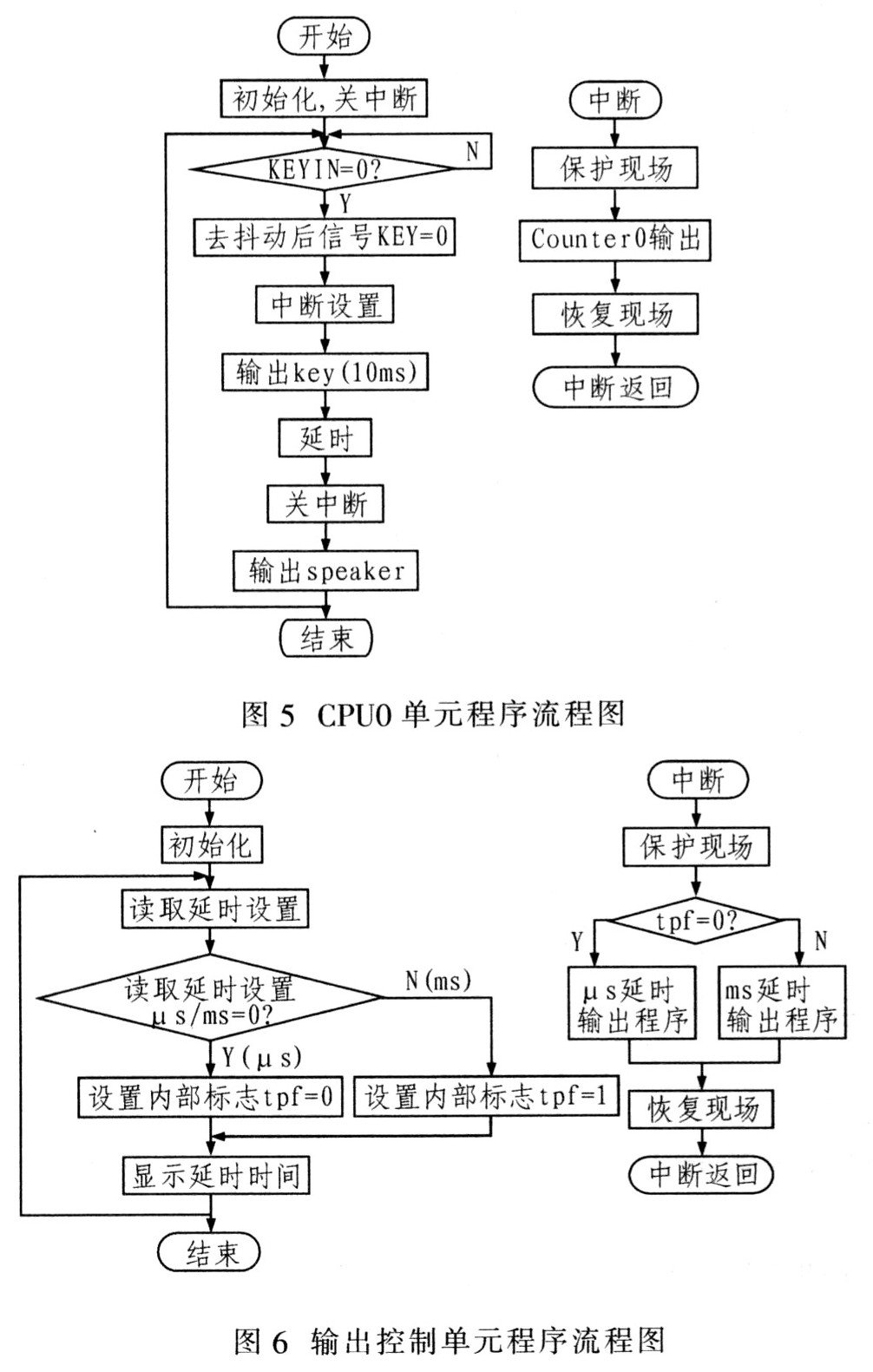

CPU0单元程序流程如图5所示。CPU0主程序完成系统初始化、按键检测、去抖动信号输出和工作状态提示音输出等工作,中断服务程序计时基准信号counterO输出。输出控制单元NO.1一NO.n程序流程如图6所示,各单元主程序完成μs/ms设置检测,延时设置读取,延时时间显示,中断程序完成控制信号输出功能。CPLD程序采用VHDL语言编写,采用QHalftusⅡ软件编译仿真。

5 结语

该系统设计可应用于电容组(9只)放电控制系统,在放电电子开关控制端、负载端测量以及微秒级延时范围内,延时误差小于O.1μs,毫秒级延时范围内,延时误差小于50μs。实际测试显示,系统实现了设计要求的调整精度。基于单片机+CPLD的多路精确延时控制系统充分利用单片机和CPLD的各自特点,实现主要设计指标。实际应用证明,该系统能够完全满足时序逻辑要求中严格控制系统的控制需求。

本系统软件设计包括CPUO单元、NO.1~NO.n输出单元及CPLD单元程序设计。由于对时间要求严格,采用汇编语言编写,信号输出由中断程序完成,由于中断响应过程、现场保护以及中断后必要的设置条件检测需要时间,所以软件必须通过容余指令(比如NOP)的延时,可保证counter0输出和控制信号延时起点在同一时刻。

CPU0单元程序流程如图5所示。CPU0主程序完成系统初始化、按键检测、去抖动信号输出和工作状态提示音输出等工作,中断服务程序计时基准信号counterO输出。输出控制单元NO.1一NO.n程序流程如图6所示,各单元主程序完成μs/ms设置检测,延时设置读取,延时时间显示,中断程序完成控制信号输出功能。CPLD程序采用VHDL语言编写,采用QHalftusⅡ软件编译仿真。

5 结语

该系统设计可应用于电容组(9只)放电控制系统,在放电电子开关控制端、负载端测量以及微秒级延时范围内,延时误差小于O.1μs,毫秒级延时范围内,延时误差小于50μs。实际测试显示,系统实现了设计要求的调整精度。基于单片机+CPLD的多路精确延时控制系统充分利用单片机和CPLD的各自特点,实现主要设计指标。实际应用证明,该系统能够完全满足时序逻辑要求中严格控制系统的控制需求。

CPLD 单片机 振荡器 电压 电路 CMOS 看门狗 VHDL 仿真 电容 电子 相关文章:

- 在选用FPGA进行设计时如何降低功耗 (03-09)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 基于CPLD的DSP微处理器与CAN控制器接口设计(06-19)

- 采用CPLD增强单片机P89C669外部设备扩展能力(07-18)

- Xilinx配置快速入门指南(08-03)

- 微机保护控制接口的CPLD抗干扰设计(11-13)