8051单片机中DPTR的扩展设计

时间:11-03

来源:互联网

点击:

3 仿真测试

在MCS8051中,针对以上3个模块分别作了修改,将DPTR扩展为两组,通过对DPTR_SEK(设定为SFR的E1H)中DPTR状态标志位dps进行操作,来实现对DPTR0和DPTRl的选取,并利用仿真软件Modelsim6.0进行了仿真测试。由于在实现DPTR扩展时主要针对SFR读写模块、PC指针模块和片外RAM地址模块这3个模块进行了修改,因此对于DPTR扩展的仿真测试也分3个模块进行。

3.1 针对SFR读写模块的测试

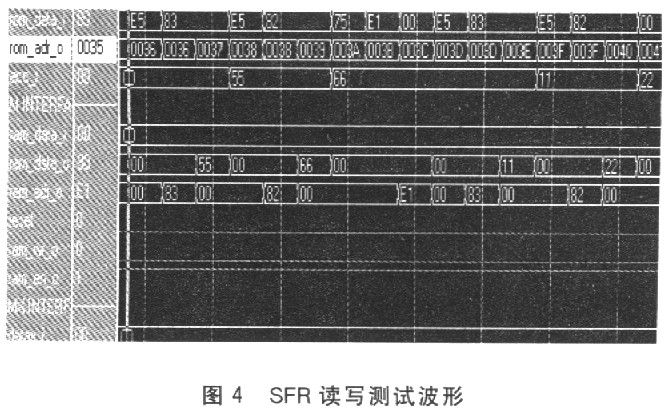

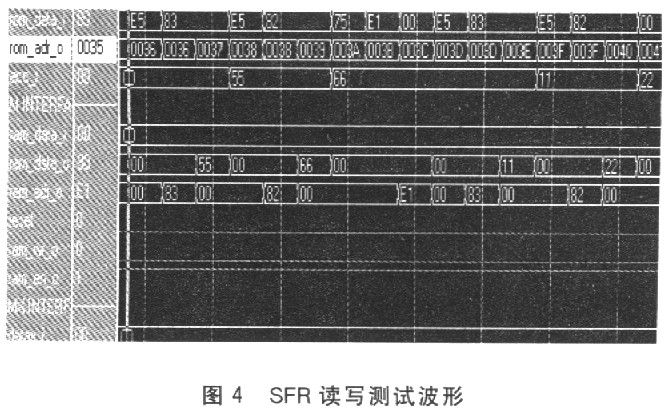

该模块的测试主要为测试DPTR0和DPTRl的数据传输。首先对DPTR状态标志dps位进行操作,分别选取DPTR0和DPTRl;其次分别对其进行写操作;最后将DPTR0和DPTRl中数据值依次输出寄存器A中。具体波形如图4所示。

由图4可知,在执行指令75E100前后(即将dps复位,选取DPTR0),DPH和DPL输出(执行指令E583,E582)到寄存器A中的值不同。指令75E100执行前DPH输出为55,DPL输出为66,执行后输出分别为11和22,因此表明通过dps进行DPTR选取,读写操作无误,即对SFR读写模块的修改无误。

3.2 针对PC指针的数据查表测试

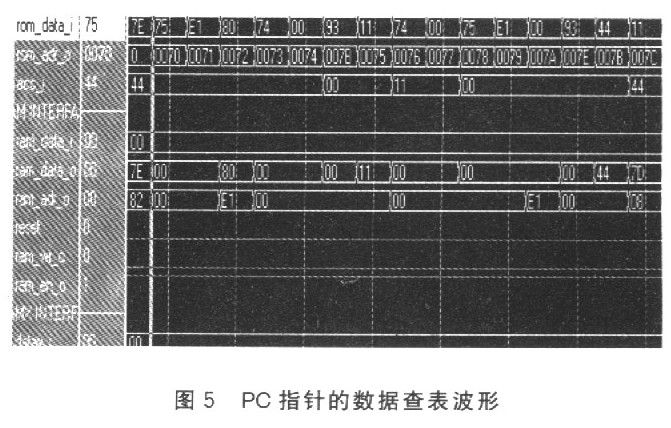

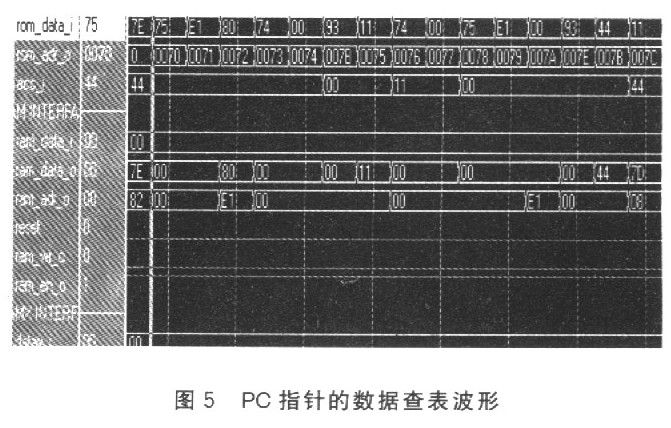

针对此模块,进行了一个查表测试,即向DPTR0和DPTRl中分别写入datal和data2两个数据表的地址;而后利用dps选取DPTR0和DPTRl,再分别对其进行数据查表输出。具体波形如图5所示。

选取DPTRl(已存入data2地址,执行指令75E180)后,将寄存器A清零(执行指令7400),并将查表数据输出(执行指令93),输出数据为11H;而后选取DPTR0,再次将寄存器A清零,并进行查表输出,输出数据为44H。对比可发现输出数据与表中数据一致。由此表明,通过dps选取DPTR0和DPTRl,进行数据查表操作无误,即对PC指针模块的修改无误。

3.3 片外RAM数据读写测试

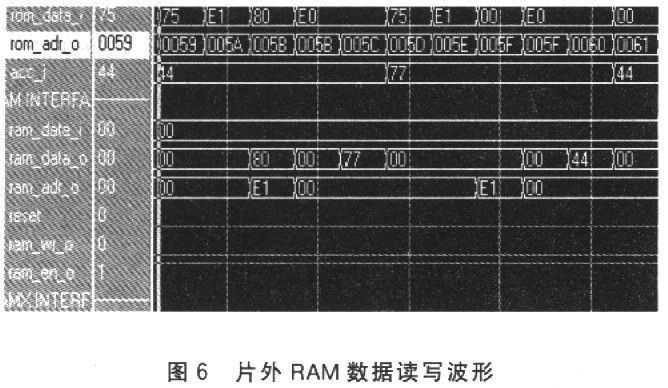

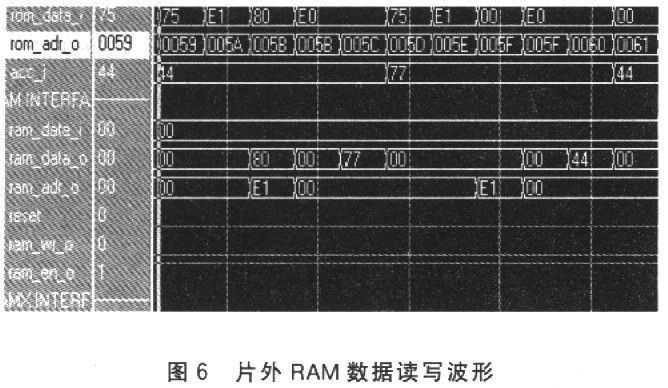

对于片外RAM数据读写测试,即大规模数据转移,测试方案为:首先将DPTR0和DPTRl中分别写入地址actr0和adrl,再分别对这两个地址写人数据,最后将这两个地址的数据通过DPTRO和DPTRl读出,将读出的结果与写入结果对比,具体测试波形如图6所示。

将dps置位(执行指令75E180)选取DPR1后,将片外RAM中adrl数据读出,输出数据为77H;将dps复位(执行指令75E100)选取DPTR0后,将adr0数据读出,输出数据为44H。经对比可发现与所写入的数据一致。由此可表明,通过dps选择DPTR0和DPTRl对片外RAM进行数据读写无误,即表明对片外RAM地址模块的修改无误。

3.4 FPGA仿真测试

基于MCS805l这款8051微控制器,我们还进行了实际的FPGA仿真测试。首先利用RS232接口,在从计算机上将太规模数据接收并写入到MCS8051片外RAM的地址adr0中;再利用例程2所给方法,进行大规模数据转移,将数据转移写入到地址adrl中;最后通过RS232接口将adrl中数据发送到计算机。通过对比发送和接收的数据发现,笔者对于DPTR的扩展无误。

结语

通过扩展DPTR可使8051在大规模数据转移时的执行效率大大提高,这使得采用扩展805l作为微控制器的嵌入式系统,在大规模数据转移时,其处理速度将大大提高。利用文中所阐述的方法也可将DPTR扩展为多组,但其具体应用意义尚需进一步探讨。

在MCS8051中,针对以上3个模块分别作了修改,将DPTR扩展为两组,通过对DPTR_SEK(设定为SFR的E1H)中DPTR状态标志位dps进行操作,来实现对DPTR0和DPTRl的选取,并利用仿真软件Modelsim6.0进行了仿真测试。由于在实现DPTR扩展时主要针对SFR读写模块、PC指针模块和片外RAM地址模块这3个模块进行了修改,因此对于DPTR扩展的仿真测试也分3个模块进行。

3.1 针对SFR读写模块的测试

该模块的测试主要为测试DPTR0和DPTRl的数据传输。首先对DPTR状态标志dps位进行操作,分别选取DPTR0和DPTRl;其次分别对其进行写操作;最后将DPTR0和DPTRl中数据值依次输出寄存器A中。具体波形如图4所示。

由图4可知,在执行指令75E100前后(即将dps复位,选取DPTR0),DPH和DPL输出(执行指令E583,E582)到寄存器A中的值不同。指令75E100执行前DPH输出为55,DPL输出为66,执行后输出分别为11和22,因此表明通过dps进行DPTR选取,读写操作无误,即对SFR读写模块的修改无误。

3.2 针对PC指针的数据查表测试

针对此模块,进行了一个查表测试,即向DPTR0和DPTRl中分别写入datal和data2两个数据表的地址;而后利用dps选取DPTR0和DPTRl,再分别对其进行数据查表输出。具体波形如图5所示。

选取DPTRl(已存入data2地址,执行指令75E180)后,将寄存器A清零(执行指令7400),并将查表数据输出(执行指令93),输出数据为11H;而后选取DPTR0,再次将寄存器A清零,并进行查表输出,输出数据为44H。对比可发现输出数据与表中数据一致。由此表明,通过dps选取DPTR0和DPTRl,进行数据查表操作无误,即对PC指针模块的修改无误。

3.3 片外RAM数据读写测试

对于片外RAM数据读写测试,即大规模数据转移,测试方案为:首先将DPTR0和DPTRl中分别写入地址actr0和adrl,再分别对这两个地址写人数据,最后将这两个地址的数据通过DPTRO和DPTRl读出,将读出的结果与写入结果对比,具体测试波形如图6所示。

将dps置位(执行指令75E180)选取DPR1后,将片外RAM中adrl数据读出,输出数据为77H;将dps复位(执行指令75E100)选取DPTR0后,将adr0数据读出,输出数据为44H。经对比可发现与所写入的数据一致。由此可表明,通过dps选择DPTR0和DPTRl对片外RAM进行数据读写无误,即表明对片外RAM地址模块的修改无误。

3.4 FPGA仿真测试

基于MCS805l这款8051微控制器,我们还进行了实际的FPGA仿真测试。首先利用RS232接口,在从计算机上将太规模数据接收并写入到MCS8051片外RAM的地址adr0中;再利用例程2所给方法,进行大规模数据转移,将数据转移写入到地址adrl中;最后通过RS232接口将adrl中数据发送到计算机。通过对比发送和接收的数据发现,笔者对于DPTR的扩展无误。

结语

通过扩展DPTR可使8051在大规模数据转移时的执行效率大大提高,这使得采用扩展805l作为微控制器的嵌入式系统,在大规模数据转移时,其处理速度将大大提高。利用文中所阐述的方法也可将DPTR扩展为多组,但其具体应用意义尚需进一步探讨。

单片机 电路 51单片机 嵌入式 VHDL 仿真 FPGA 相关文章:

- 单片机智能频率信号装置(11-25)

- 单片机在医学信号检测仪中的应用(02-07)

- 单片机应用编程技巧(02-25)

- DSP与单片机通信的多种方案设计(03-08)

- 单片机与PC机串行通信的实现方法 (02-25)

- 单片机与PC通信的简化接口 (05-11)